8b10b编码 verilog

参考网址[https://asics.chuckbenz.com/]

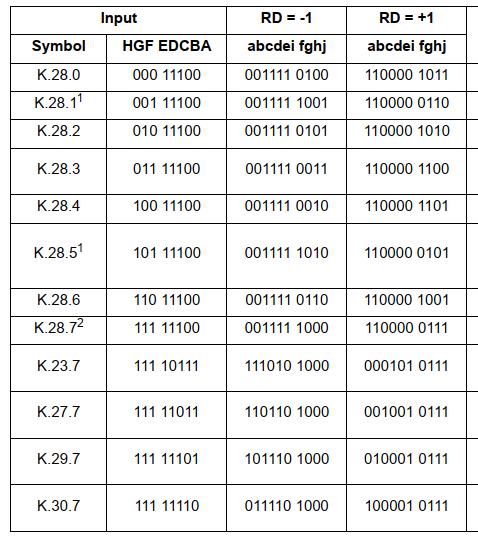

8bit与10bit对应图

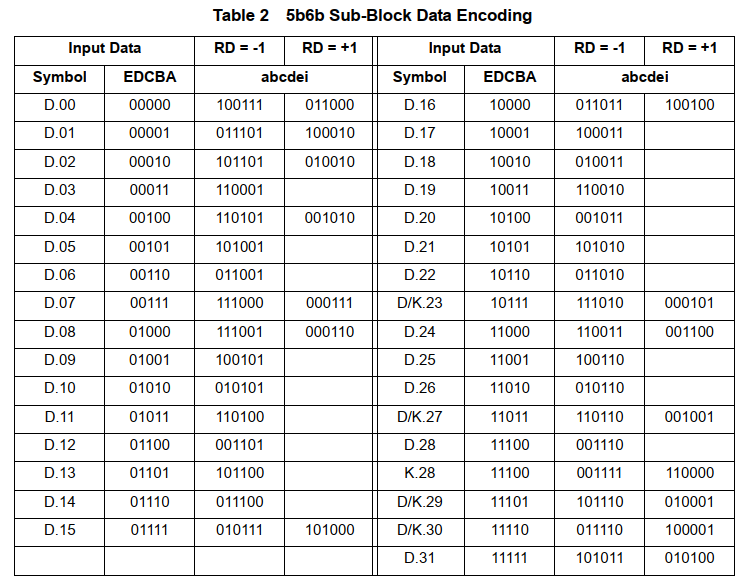

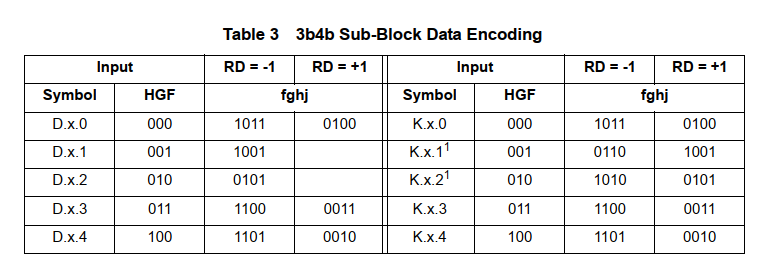

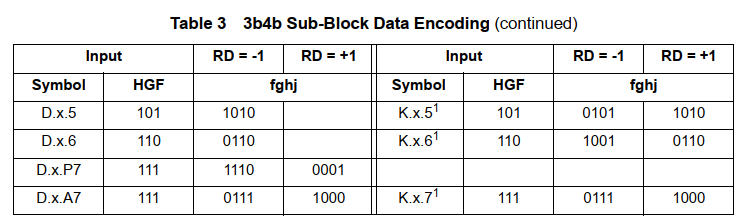

包含255个D码与12个K码,K码常用作控制字符。常表示为D.x.y或K.x.y(x为低5位的值,y为高3位的值)。

disparity表示当前0,1个数状态。0表示当前0的个数>=1的个数,1表示1的个数>=0的个数。

a7与p7

当KD共用x码值(23,27,29,30)时,通过高3位区分,D码使用备用P7编码,K码使用A7编码。

其余情况下,根据5b6b的译码结果决定使用p7还是a7,避免出现连续的0或者1。

经过观察,只有D.17.7,D.18.7,D.20.7和所有的K码使用A7编码,其余情况下都使用P7。

encode

输入变化前的disparity,data_in,输出data_out,变化后的disparity。

其中data_in为9bit数,最高位表示是否为k码,低8bit为8bit编码。

以9'b0_0000_0000,disparity=0为例,

首先取低5位,为00000,此时disparity为0,查表5b6b编码为100111。

100111中1的个数大于0的个数,所以需要disparity翻转为1。

高3位为000,此时disparity为1,3b4b编码为0100。

0100中0的个数大于1的个数,此时disparity翻转为0。

所以最后输出10bit数1001110100(可能需要翻转高低位),disparity为1。

disparity这种两步的变换可以简化为一步,encode得到的10bit中0,1个数不等时,进行翻转,否则不翻转。

disparity变化条件

当前的disparity为0时,进行5b6b或者3b4b编码时,选择的编码一定是1的个数>=0的个数。、

选择编码1的个数>0的个数时,disparity翻转,否则不翻转。

当前的disparity为1时,进行5b6b或者3b4b编码时,选择的编码一定是0的个数>=1的个数。、

选择编码0的个数>1的个数时,disparity翻转,否则不翻转。

decode

输入当前disparity,10bit数,输出code_err,disp_err,变化后的disparity,9bit数。

当当前10bit码不存在对应的8bit码时,code_err拉高。

当当前disparity为0且10bit数中0的个数大于1的个数时,或disparity为1且10bit数中1的个数大于0的个数时,disp_err拉高。

当前disparity相同时,变化后的disparity应与encode的变化后disparity相同。

源码转载:

encode.v

// Chuck Benz, Hollis, NH Copyright (c)2002

//

// The information and description contained herein is the

// property of Chuck Benz.

//

// Permission is granted for any reuse of this information

// and description as long as this copyright notice is

// preserved. Modifications may be made as long as this

// notice is preserved.

// per Widmer and Franaszek

module encode (datain, dispin, dataout, dispout) ;

input [8:0] datain ;

input dispin ; // 0 = neg disp; 1 = pos disp

output [9:0] dataout ;

output dispout ;

wire ai = datain[0] ;

wire bi = datain[1] ;

wire ci = datain[2] ;

wire di = datain[3] ;

wire ei = datain[4] ;

wire fi = datain[5] ;

wire gi = datain[6] ;

wire hi = datain[7] ;

wire ki = datain[8] ;

wire aeqb = (ai & bi) | (!ai & !bi) ;

wire ceqd = (ci & di) | (!ci & !di) ;

wire l22 = (ai & bi & !ci & !di) |

(ci & di & !ai & !bi) |

( !aeqb & !ceqd) ;

wire l40 = ai & bi & ci & di ;

wire l04 = !ai & !bi & !ci & !di ;

wire l13 = ( !aeqb & !ci & !di) |

( !ceqd & !ai & !bi) ;

wire l31 = ( !aeqb & ci & di) |

( !ceqd & ai & bi) ;

// The 5B/6B encoding

wire ao = ai ;

wire bo = (bi & !l40) | l04 ;

wire co = l04 | ci | (ei & di & !ci & !bi & !ai) ;

wire do = di & ! (ai & bi & ci) ;

wire eo = (ei | l13) & ! (ei & di & !ci & !bi & !ai) ;

wire io = (l22 & !ei) |

(ei & !di & !ci & !(ai&bi)) | // D16, D17, D18

(ei & l40) |

(ki & ei & di & ci & !bi & !ai) | // K.28

(ei & !di & ci & !bi & !ai) ;

// pds16 indicates cases where d-1 is assumed + to get our encoded value

wire pd1s6 = (ei & di & !ci & !bi & !ai) | (!ei & !l22 & !l31) ;

// nds16 indicates cases where d-1 is assumed - to get our encoded value

wire nd1s6 = ki | (ei & !l22 & !l13) | (!ei & !di & ci & bi & ai) ;

// ndos6 is pds16 cases where d-1 is + yields - disp out - all of them

wire ndos6 = pd1s6 ;

// pdos6 is nds16 cases where d-1 is - yields + disp out - all but one

wire pdos6 = ki | (ei & !l22 & !l13) ;

// some Dx.7 and all Kx.7 cases result in run length of 5 case unless

// an alternate coding is used (referred to as Dx.A7, normal is Dx.P7)

// specifically, D11, D13, D14, D17, D18, D19.

wire alt7 = fi & gi & hi & (ki |

(dispin ? (!ei & di & l31) : (ei & !di & l13))) ;

wire fo = fi & ! alt7 ;

wire go = gi | (!fi & !gi & !hi) ;

wire ho = hi ;

wire jo = (!hi & (gi ^ fi)) | alt7 ;

// nd1s4 is cases where d-1 is assumed - to get our encoded value

wire nd1s4 = fi & gi ;

// pd1s4 is cases where d-1 is assumed + to get our encoded value

wire pd1s4 = (!fi & !gi) | (ki & ((fi & !gi) | (!fi & gi))) ;

// ndos4 is pd1s4 cases where d-1 is + yields - disp out - just some

wire ndos4 = (!fi & !gi) ;

// pdos4 is nd1s4 cases where d-1 is - yields + disp out

wire pdos4 = fi & gi & hi ;

// only legal K codes are K28.0->.7, K23/27/29/30.7

// K28.0->7 is ei=di=ci=1,bi=ai=0

// K23 is 10111

// K27 is 11011

// K29 is 11101

// K30 is 11110 - so K23/27/29/30 are ei & l31

wire illegalk = ki &

(ai | bi | !ci | !di | !ei) & // not K28.0->7

(!fi | !gi | !hi | !ei | !l31) ; // not K23/27/29/30.7

// now determine whether to do the complementing

// complement if prev disp is - and pd1s6 is set, or + and nd1s6 is set

wire compls6 = (pd1s6 & !dispin) | (nd1s6 & dispin) ;

// disparity out of 5b6b is disp in with pdso6 and ndso6

// pds16 indicates cases where d-1 is assumed + to get our encoded value

// ndos6 is cases where d-1 is + yields - disp out

// nds16 indicates cases where d-1 is assumed - to get our encoded value

// pdos6 is cases where d-1 is - yields + disp out

// disp toggles in all ndis16 cases, and all but that 1 nds16 case

wire disp6 = dispin ^ (ndos6 | pdos6) ;

wire compls4 = (pd1s4 & !disp6) | (nd1s4 & disp6) ;

assign dispout = disp6 ^ (ndos4 | pdos4) ;

assign dataout = {(jo ^ compls4), (ho ^ compls4),

(go ^ compls4), (fo ^ compls4),

(io ^ compls6), (eo ^ compls6),

(do ^ compls6), (co ^ compls6),

(bo ^ compls6), (ao ^ compls6)} ;

endmodule

decode.v

// Chuck Benz, Hollis, NH Copyright (c)2002

//

// The information and description contained herein is the

// property of Chuck Benz.

//

// Permission is granted for any reuse of this information

// and description as long as this copyright notice is

// preserved. Modifications may be made as long as this

// notice is preserved.

// per Widmer and Franaszek

module decode (datain, dispin, dataout, dispout, code_err, disp_err) ;

input [9:0] datain ;

input dispin ;

output [8:0] dataout ;

output dispout ;

output code_err ;

output disp_err ;

wire ai = datain[0] ;

wire bi = datain[1] ;

wire ci = datain[2] ;

wire di = datain[3] ;

wire ei = datain[4] ;

wire ii = datain[5] ;

wire fi = datain[6] ;

wire gi = datain[7] ;

wire hi = datain[8] ;

wire ji = datain[9] ;

wire aeqb = (ai & bi) | (!ai & !bi) ;

wire ceqd = (ci & di) | (!ci & !di) ;

wire p22 = (ai & bi & !ci & !di) |

(ci & di & !ai & !bi) |

( !aeqb & !ceqd) ;

wire p13 = ( !aeqb & !ci & !di) |

( !ceqd & !ai & !bi) ;

wire p31 = ( !aeqb & ci & di) |

( !ceqd & ai & bi) ;

wire p40 = ai & bi & ci & di ;

wire p04 = !ai & !bi & !ci & !di ;

wire disp6a = p31 | (p22 & dispin) ; // pos disp if p22 and was pos, or p31.

wire disp6a2 = p31 & dispin ; // disp is ++ after 4 bits

wire disp6a0 = p13 & ! dispin ; // -- disp after 4 bits

wire disp6b = (((ei & ii & ! disp6a0) | (disp6a & (ei | ii)) | disp6a2 |

(ei & ii & di)) & (ei | ii | di)) ;

// The 5B/6B decoding special cases where ABCDE != abcde

wire p22bceeqi = p22 & bi & ci & (ei == ii) ;

wire p22bncneeqi = p22 & !bi & !ci & (ei == ii) ;

wire p13in = p13 & !ii ;

wire p31i = p31 & ii ;

wire p13dei = p13 & di & ei & ii ;

wire p22aceeqi = p22 & ai & ci & (ei == ii) ;

wire p22ancneeqi = p22 & !ai & !ci & (ei == ii) ;

wire p13en = p13 & !ei ;

wire anbnenin = !ai & !bi & !ei & !ii ;

wire abei = ai & bi & ei & ii ;

wire cdei = ci & di & ei & ii ;

wire cndnenin = !ci & !di & !ei & !ii ;

// non-zero disparity cases:

wire p22enin = p22 & !ei & !ii ;

wire p22ei = p22 & ei & ii ;

//wire p13in = p12 & !ii ;

//wire p31i = p31 & ii ;

wire p31dnenin = p31 & !di & !ei & !ii ;

//wire p13dei = p13 & di & ei & ii ;

wire p31e = p31 & ei ;

wire compa = p22bncneeqi | p31i | p13dei | p22ancneeqi |

p13en | abei | cndnenin ;

wire compb = p22bceeqi | p31i | p13dei | p22aceeqi |

p13en | abei | cndnenin ;

wire compc = p22bceeqi | p31i | p13dei | p22ancneeqi |

p13en | anbnenin | cndnenin ;

wire compd = p22bncneeqi | p31i | p13dei | p22aceeqi |

p13en | abei | cndnenin ;

wire compe = p22bncneeqi | p13in | p13dei | p22ancneeqi |

p13en | anbnenin | cndnenin ;

wire ao = ai ^ compa ;

wire bo = bi ^ compb ;

wire co = ci ^ compc ;

wire do = di ^ compd ;

wire eo = ei ^ compe ;

wire feqg = (fi & gi) | (!fi & !gi) ;

wire heqj = (hi & ji) | (!hi & !ji) ;

wire fghj22 = (fi & gi & !hi & !ji) |

(!fi & !gi & hi & ji) |

( !feqg & !heqj) ;

wire fghjp13 = ( !feqg & !hi & !ji) |

( !heqj & !fi & !gi) ;

wire fghjp31 = ( (!feqg) & hi & ji) |

( !heqj & fi & gi) ;

wire dispout = (fghjp31 | (disp6b & fghj22) | (hi & ji)) & (hi | ji) ;

wire ko = ( (ci & di & ei & ii) | ( !ci & !di & !ei & !ii) |

(p13 & !ei & ii & gi & hi & ji) |

(p31 & ei & !ii & !gi & !hi & !ji)) ;

wire alt7 = (fi & !gi & !hi & // 1000 cases, where disp6b is 1

((dispin & ci & di & !ei & !ii) | ko |

(dispin & !ci & di & !ei & !ii))) |

(!fi & gi & hi & // 0111 cases, where disp6b is 0

(( !dispin & !ci & !di & ei & ii) | ko |

( !dispin & ci & !di & ei & ii))) ;

wire k28 = (ci & di & ei & ii) | ! (ci | di | ei | ii) ;

// k28 with positive disp into fghi - .1, .2, .5, and .6 special cases

wire k28p = ! (ci | di | ei | ii) ;

wire fo = (ji & !fi & (hi | !gi | k28p)) |

(fi & !ji & (!hi | gi | !k28p)) |

(k28p & gi & hi) |

(!k28p & !gi & !hi) ;

wire go = (ji & !fi & (hi | !gi | !k28p)) |

(fi & !ji & (!hi | gi |k28p)) |

(!k28p & gi & hi) |

(k28p & !gi & !hi) ;

wire ho = ((ji ^ hi) & ! ((!fi & gi & !hi & ji & !k28p) | (!fi & gi & hi & !ji & k28p) |

(fi & !gi & !hi & ji & !k28p) | (fi & !gi & hi & !ji & k28p))) |

(!fi & gi & hi & ji) | (fi & !gi & !hi & !ji) ;

wire disp6p = (p31 & (ei | ii)) | (p22 & ei & ii) ;

wire disp6n = (p13 & ! (ei & ii)) | (p22 & !ei & !ii) ;

wire disp4p = fghjp31 ;

wire disp4n = fghjp13 ;

assign code_err = p40 | p04 | (fi & gi & hi & ji) | (!fi & !gi & !hi & !ji) |

(p13 & !ei & !ii) | (p31 & ei & ii) |

(ei & ii & fi & gi & hi) | (!ei & !ii & !fi & !gi & !hi) |

(ei & !ii & gi & hi & ji) | (!ei & ii & !gi & !hi & !ji) |

(!p31 & ei & !ii & !gi & !hi & !ji) |

(!p13 & !ei & ii & gi & hi & ji) |

(((ei & ii & !gi & !hi & !ji) |

(!ei & !ii & gi & hi & ji)) &

! ((ci & di & ei) | (!ci & !di & !ei))) |

(disp6p & disp4p) | (disp6n & disp4n) |

(ai & bi & ci & !ei & !ii & ((!fi & !gi) | fghjp13)) |

(!ai & !bi & !ci & ei & ii & ((fi & gi) | fghjp31)) |

(fi & gi & !hi & !ji & disp6p) |

(!fi & !gi & hi & ji & disp6n) |

(ci & di & ei & ii & !fi & !gi & !hi) |

(!ci & !di & !ei & !ii & fi & gi & hi) ;

assign dataout = {ko, ho, go, fo, eo, do, co, bo, ao} ;

// my disp err fires for any legal codes that violate disparity, may fire for illegal codes

assign disp_err = ((dispin & disp6p) | (disp6n & !dispin) |

(dispin & !disp6n & fi & gi) |

(dispin & ai & bi & ci) |

(dispin & !disp6n & disp4p) |

(!dispin & !disp6p & !fi & !gi) |

(!dispin & !ai & !bi & !ci) |

(!dispin & !disp6p & disp4n) |

(disp6p & disp4p) | (disp6n & disp4n)) ;

endmodule

testbench

// Chuck Benz, Hollis, NH Copyright (c)2002

//

// The information and description contained herein is the

// property of Chuck Benz.

//

// Permission is granted for any reuse of this information

// and description as long as this copyright notice is

// preserved. Modifications may be made as long as this

// notice is preserved.

// 11-OCT-2002: updated with clearer messages, and checking decodeout

`timescale 1ns / 1ns

module test_8b10b ;

reg [29:0] code8b10b [0:267] ;

reg [8:0] testin ;

reg dispin ;

reg [10:0] i ;

wire [9:0] testout ;

wire dispout, decodedisp, decodeerr, disperr ;

wire [8:0] decodeout ;

// My data file is 30 columns. Column 1 becomes [29], 2 becomes [28], etc..

// code[0] is last Column (30)

// First column, [29] is K indication

// columns 2:9, [28:21], are data byte, aka 'm' and 'n' of Dm.n

// columns 10:19, [20:11] are 10b symbol if starting disparity was negative, 0

// columns 20:29, [10:1] are 10b symbol if starting disparity was positive, 1

// column 30, [0], is a 1 if symbol results in a disparity flip

// 0 for a balanced symbol (5 '1's, 5 '0's).

wire [29:0] code = code8b10b[i] ;

wire [9:0] expect_0_disp = {code[11], code[12], code[13], code[14], code[15],

code[16], code[17], code[18], code[19], code[20]} ;

wire [9:0] expect_1_disp = {code[1], code[2], code[3], code[4], code[5],

code[6], code[7], code[8], code[9], code[10]} ;

reg [1023:0] legal ; // mark every used 10b symbol as legal, leave rest marked as not

reg [2047:0] okdisp ; // now mark every used combination of symbol and starting disparity

reg [8:0] mapcode [1023:0] ;

reg [10:0] codedisp0, codedisp1 ;

reg [9:0] decodein ;

reg decdispin ;

integer errors ;

encode DUTE (testin, dispin, testout, dispout) ;

decode DUTD (decodein, decdispin, decodeout, decodedisp, decodeerr, disperr) ;

always @ (code) testin = code[29:21] ;

initial begin

errors = 0 ;

$readmemb ("8b10b_a.mem", code8b10b) ;

//$vcdpluson ;

$dumpvars (0);

$display ("\n\nFirst, test by trying all 268 (256 Dx.y and 12 Kx.y)") ;

$display ("valid inputs, with both + and - starting disparity.");

$display ("We check that the encoder output and ending disparity is correct.");

$display ("We also check that the decoder matches.");

for (i = 0 ; i < 268 ; i = i + 1) begin

// testin = code[29:21] ;

dispin = 0 ;

#1

decodein = testout ;

decdispin = dispin ;

#1

// $display ("%b %b %b %b *%b*", dispin, testin, testout, {dispout, DUTD.disp6a, DUTD.disp6a2, DUTD.disp6a0, DUTD.disp6a2}, decodeout,, decodedisp,, DUTD.k28,, DUTD.disp6b) ;

if (testout != expect_0_disp)

$display ("bad code0 %b %b %b %b %b", dispin, testin, dispout, testout, expect_0_disp) ;

if (dispout != (dispin ^ code[0]))

$display ("bad disp0 %b %b %b %b %b", dispin, testin, dispout, testout, (dispin ^ code[0])) ;

if (0 != (9'b1_1111_1111 & (testin ^ decodeout)))

$display ("diff in abcdefghk decode, %b %b %b %b %b", dispin, testin, dispout, testout, decodeout) ;

if (decodedisp != dispout)

$display ("diff in decoder disp out, %b %b %b %b %b", dispin, testin, dispout, testout, decodeout) ;

if (decodeerr) $display ("decode error asserted improperly, %b %b %b %b %b", dispin, testin, dispout, testout, decodeout) ;

if ((testout != expect_0_disp) | decodeerr |

(dispout != (dispin ^ code[0])) | (decodedisp != dispout))

errors = errors + 1 ;

dispin = 1 ;

#1

decodein = testout ;

decdispin = dispin ;

#1

// $display ("%b %b %b %b *%b*", dispin, testin, testout, {dispout, DUTD.disp6a, DUTD.disp6a2, DUTD.disp6a0, DUTD.disp6a2, DUTD.fghjp31, DUTD.feqg, DUTD.heqj, DUTD.fghj22, DUTD.fi, DUTD.gi, DUTD.hi, DUTD.ji, DUTD.dispout}, decodeout,, decodedisp,, DUTD.k28,, DUTD.disp6b) ;

if (testout != expect_1_disp)

$display ("bad code1 %b %b %b %b %b", dispin, testin, dispout, testout, expect_1_disp) ;

if (dispout != (dispin ^ code[0]))

$display ("bad disp1 %b %b %b %b %b", dispin, testin, dispout, testout, (dispin ^ code[0])) ;

if (0 != (9'b1_1111_1111 & (testin ^ decodeout)))

$display ("diff in abcdefghk decode, %b %b %b %b %b", dispin, testin, dispout, testout, decodeout) ;

if (decodedisp != dispout)

$display ("diff in decoder disp out, %b %b %b %b %b", dispin, testin, dispout, testout, decodeout) ;

if (decodeerr) $display ("decode error asserted improperly, %b %b %b %b %b", dispin, testin, dispout, testout, decodeout) ;

if ((testout != expect_1_disp) | decodeerr |

(dispout != (dispin ^ code[0])) | (decodedisp != dispout))

errors = errors + 1 ;

end

$display ("%d errors in that testing.\n", errors) ;

// Now, having verified all legal codes, lets run some illegal codes

// at the decoder... how to figure illegal codes ? 2048 possible cases,

// lets mark the OK ones...

legal = 0 ;

okdisp = 0 ;

for (i = 0 ; i < 268 ; i = i + 1) begin

#1

// $display ("i=%d: %b %b %d %d %x %x", i, expect_0_disp, expect_1_disp, expect_0_disp, expect_1_disp, expect_0_disp, expect_1_disp) ;

legal[expect_0_disp] = 1 ;

legal[expect_1_disp] = 1 ;

codedisp0 = expect_0_disp ;

codedisp1 = {1'b1, expect_1_disp} ;

okdisp[codedisp0] = 1 ;

okdisp[codedisp1] = 1 ;

mapcode[expect_0_disp] = code[29:21] ;

mapcode[expect_1_disp] = code[29:21] ;

end

$display ("Now lets test all (legal and illegal) codes into the decoder.");

$display ("checking all possible decode inputs") ;

for (i = 0 ; i < 1024 ; i = i + 1) begin

decodein = i ;

decdispin = 0 ;

codedisp1 = 1024 | i ;

#1

if (((legal[i] == 0) & (decodeerr != 1)) |

(legal[i] & (mapcode[i] != decodeout)) |

(legal[i] & (disperr != !okdisp[i])))

$display ("10b:%b start disp:%b 8b:%b end disp:%b codevio:%b dispvio:%b known code:%b used disp:",

decodein, decdispin, decodeout, decodedisp, decodeerr, disperr, legal[i], okdisp[i]) ;

if ((legal[i] == 0) & (decodeerr != 1)) $display ("ERR: decoderr should be 1") ;

if (legal[i] & (mapcode[i] != decodeout)) $display ("ERR: decode output incorrect") ;

if (legal[i] & (disperr != 1) & !okdisp[i]) $display ("ERR: disp err should be asserted") ;

else if (legal[i] & (disperr != 0) & okdisp[i])

$display ("ERR: disp err should not be asserted") ;

if (((legal[i] == 0) & (decodeerr != 1)) |

(legal[i] & !disperr & !okdisp[i]) |

(legal[i] & (mapcode[i] != decodeout)) |

(legal[i] & disperr & okdisp[i]))

errors = errors + 1 ;

decdispin = 1 ;

#1

if (((legal[i] == 0) & (decodeerr != 1)) |

(legal[i] & (mapcode[i] != decodeout)) |

(legal[i] & (disperr != !okdisp[i|1024])))

$display ("10b:%b start disp:%b 8b:%b end disp:%b codevio:%b dispvio:%b known code:%b used disp:",

decodein, decdispin, decodeout, decodedisp, decodeerr, disperr, legal[i], okdisp[i|1024]) ;

if ((legal[i] == 0) & (decodeerr != 1)) $display ("ERR: decoderr should be 1") ;

if (legal[i] & (mapcode[i] != decodeout)) $display ("ERR: decode output incorrect") ;

if (legal[i] & (disperr != 1) & !okdisp[i|1024]) $display ("ERR: disp err should be asserted") ;

else if (legal[i] & (disperr != 0) & okdisp[i|1024])

$display ("ERR: disp err should not be asserted") ;

if (((legal[i] == 0) & (decodeerr != 1)) |

(legal[i] & !disperr & !okdisp[i|1024]) |

(legal[i] & (mapcode[i] != decodeout)) |

(legal[i] & disperr & okdisp[i|1024]))

errors = errors + 1 ;

end // for (i = 0 ; i < 1024 ; i = i + 1)

$display ("\nDone testing decoder.\n") ;

$display ("Total error count: %d", errors);

if (errors == 0) $display ("Congratulations!\n");

$finish ;

end // initial begin

endmodule

8b10b_a.mem(30bit的解释见testbench)

0_00000000_1001110100_0110001011_0

0_00000001_0111010100_1000101011_0

0_00000010_1011010100_0100101011_0

0_00000011_1100011011_1100010100_1

0_00000100_1101010100_0010101011_0

0_00000101_1010011011_1010010100_1

0_00000110_0110011011_0110010100_1

0_00000111_1110001011_0001110100_1

0_00001000_1110010100_0001101011_0

0_00001001_1001011011_1001010100_1

0_00001010_0101011011_0101010100_1

0_00001011_1101001011_1101000100_1

0_00001100_0011011011_0011010100_1

0_00001101_1011001011_1011000100_1

0_00001110_0111001011_0111000100_1

0_00001111_0101110100_1010001011_0

0_00010000_0110110100_1001001011_0

0_00010001_1000111011_1000110100_1

0_00010010_0100111011_0100110100_1

0_00010011_1100101011_1100100100_1

0_00010100_0010111011_0010110100_1

0_00010101_1010101011_1010100100_1

0_00010110_0110101011_0110100100_1

0_00010111_1110100100_0001011011_0

0_00011000_1100110100_0011001011_0

0_00011001_1001101011_1001100100_1

0_00011010_0101101011_0101100100_1

0_00011011_1101100100_0010011011_0

0_00011100_0011101011_0011100100_1

0_00011101_1011100100_0100011011_0

0_00011110_0111100100_1000011011_0

0_00011111_1010110100_0101001011_0

0_00100000_1001111001_0110001001_1

0_00100001_0111011001_1000101001_1

0_00100010_1011011001_0100101001_1

0_00100011_1100011001_1100011001_0

0_00100100_1101011001_0010101001_1

0_00100101_1010011001_1010011001_0

0_00100110_0110011001_0110011001_0

0_00100111_1110001001_0001111001_0

0_00101000_1110011001_0001101001_1

0_00101001_1001011001_1001011001_0

0_00101010_0101011001_0101011001_0

0_00101011_1101001001_1101001001_0

0_00101100_0011011001_0011011001_0

0_00101101_1011001001_1011001001_0

0_00101110_0111001001_0111001001_0

0_00101111_0101111001_1010001001_1

0_00110000_0110111001_1001001001_1

0_00110001_1000111001_1000111001_0

0_00110010_0100111001_0100111001_0

0_00110011_1100101001_1100101001_0

0_00110100_0010111001_0010111001_0

0_00110101_1010101001_1010101001_0

0_00110110_0110101001_0110101001_0

0_00110111_1110101001_0001011001_1

0_00111000_1100111001_0011001001_1

0_00111001_1001101001_1001101001_0

0_00111010_0101101001_0101101001_0

0_00111011_1101101001_0010011001_1

0_00111100_0011101001_0011101001_0

0_00111101_1011101001_0100011001_1

0_00111110_0111101001_1000011001_1

0_00111111_1010111001_0101001001_1

0_01000000_1001110101_0110000101_1

0_01000001_0111010101_1000100101_1

0_01000010_1011010101_0100100101_1

0_01000011_1100010101_1100010101_0

0_01000100_1101010101_0010100101_1

0_01000101_1010010101_1010010101_0

0_01000110_0110010101_0110010101_0

0_01000111_1110000101_0001110101_0

0_01001000_1110010101_0001100101_1

0_01001001_1001010101_1001010101_0

0_01001010_0101010101_0101010101_0

0_01001011_1101000101_1101000101_0

0_01001100_0011010101_0011010101_0

0_01001101_1011000101_1011000101_0

0_01001110_0111000101_0111000101_0

0_01001111_0101110101_1010000101_1

0_01010000_0110110101_1001000101_1

0_01010001_1000110101_1000110101_0

0_01010010_0100110101_0100110101_0

0_01010011_1100100101_1100100101_0

0_01010100_0010110101_0010110101_0

0_01010101_1010100101_1010100101_0

0_01010110_0110100101_0110100101_0

0_01010111_1110100101_0001010101_1

0_01011000_1100110101_0011000101_1

0_01011001_1001100101_1001100101_0

0_01011010_0101100101_0101100101_0

0_01011011_1101100101_0010010101_1

0_01011100_0011100101_0011100101_0

0_01011101_1011100101_0100010101_1

0_01011110_0111100101_1000010101_1

0_01011111_1010110101_0101000101_1

0_01100000_1001110011_0110001100_1

0_01100001_0111010011_1000101100_1

0_01100010_1011010011_0100101100_1

0_01100011_1100011100_1100010011_0

0_01100100_1101010011_0010101100_1

0_01100101_1010011100_1010010011_0

0_01100110_0110011100_0110010011_0

0_01100111_1110001100_0001110011_0

0_01101000_1110010011_0001101100_1

0_01101001_1001011100_1001010011_0

0_01101010_0101011100_0101010011_0

0_01101011_1101001100_1101000011_0

0_01101100_0011011100_0011010011_0

0_01101101_1011001100_1011000011_0

0_01101110_0111001100_0111000011_0

0_01101111_0101110011_1010001100_1

0_01110000_0110110011_1001001100_1

0_01110001_1000111100_1000110011_0

0_01110010_0100111100_0100110011_0

0_01110011_1100101100_1100100011_0

0_01110100_0010111100_0010110011_0

0_01110101_1010101100_1010100011_0

0_01110110_0110101100_0110100011_0

0_01110111_1110100011_0001011100_1

0_01111000_1100110011_0011001100_1

0_01111001_1001101100_1001100011_0

0_01111010_0101101100_0101100011_0

0_01111011_1101100011_0010011100_1

0_01111100_0011101100_0011100011_0

0_01111101_1011100011_0100011100_1

0_01111110_0111100011_1000011100_1

0_01111111_1010110011_0101001100_1

0_10000000_1001110010_0110001101_0

0_10000001_0111010010_1000101101_0

0_10000010_1011010010_0100101101_0

0_10000011_1100011101_1100010010_1

0_10000100_1101010010_0010101101_0

0_10000101_1010011101_1010010010_1

0_10000110_0110011101_0110010010_1

0_10000111_1110001101_0001110010_1

0_10001000_1110010010_0001101101_0

0_10001001_1001011101_1001010010_1

0_10001010_0101011101_0101010010_1

0_10001011_1101001101_1101000010_1

0_10001100_0011011101_0011010010_1

0_10001101_1011001101_1011000010_1

0_10001110_0111001101_0111000010_1

0_10001111_0101110010_1010001101_0

0_10010000_0110110010_1001001101_0

0_10010001_1000111101_1000110010_1

0_10010010_0100111101_0100110010_1

0_10010011_1100101101_1100100010_1

0_10010100_0010111101_0010110010_1

0_10010101_1010101101_1010100010_1

0_10010110_0110101101_0110100010_1

0_10010111_1110100010_0001011101_0

0_10011000_1100110010_0011001101_0

0_10011001_1001101101_1001100010_1

0_10011010_0101101101_0101100010_1

0_10011011_1101100010_0010011101_0

0_10011100_0011101101_0011100010_1

0_10011101_1011100010_0100011101_0

0_10011110_0111100010_1000011101_0

0_10011111_1010110010_0101001101_0

0_10100000_1001111010_0110001010_1

0_10100001_0111011010_1000101010_1

0_10100010_1011011010_0100101010_1

0_10100011_1100011010_1100011010_0

0_10100100_1101011010_0010101010_1

0_10100101_1010011010_1010011010_0

0_10100110_0110011010_0110011010_0

0_10100111_1110001010_0001111010_0

0_10101000_1110011010_0001101010_1

0_10101001_1001011010_1001011010_0

0_10101010_0101011010_0101011010_0

0_10101011_1101001010_1101001010_0

0_10101100_0011011010_0011011010_0

0_10101101_1011001010_1011001010_0

0_10101110_0111001010_0111001010_0

0_10101111_0101111010_1010001010_1

0_10110000_0110111010_1001001010_1

0_10110001_1000111010_1000111010_0

0_10110010_0100111010_0100111010_0

0_10110011_1100101010_1100101010_0

0_10110100_0010111010_0010111010_0

0_10110101_1010101010_1010101010_0

0_10110110_0110101010_0110101010_0

0_10110111_1110101010_0001011010_1

0_10111000_1100111010_0011001010_1

0_10111001_1001101010_1001101010_0

0_10111010_0101101010_0101101010_0

0_10111011_1101101010_0010011010_1

0_10111100_0011101010_0011101010_0

0_10111101_1011101010_0100011010_1

0_10111110_0111101010_1000011010_1

0_10111111_1010111010_0101001010_1

0_11000000_1001110110_0110000110_1

0_11000001_0111010110_1000100110_1

0_11000010_1011010110_0100100110_1

0_11000011_1100010110_1100010110_0

0_11000100_1101010110_0010100110_1

0_11000101_1010010110_1010010110_0

0_11000110_0110010110_0110010110_0

0_11000111_1110000110_0001110110_0

0_11001000_1110010110_0001100110_1

0_11001001_1001010110_1001010110_0

0_11001010_0101010110_0101010110_0

0_11001011_1101000110_1101000110_0

0_11001100_0011010110_0011010110_0

0_11001101_1011000110_1011000110_0

0_11001110_0111000110_0111000110_0

0_11001111_0101110110_1010000110_1

0_11010000_0110110110_1001000110_1

0_11010001_1000110110_1000110110_0

0_11010010_0100110110_0100110110_0

0_11010011_1100100110_1100100110_0

0_11010100_0010110110_0010110110_0

0_11010101_1010100110_1010100110_0

0_11010110_0110100110_0110100110_0

0_11010111_1110100110_0001010110_1

0_11011000_1100110110_0011000110_1

0_11011001_1001100110_1001100110_0

0_11011010_0101100110_0101100110_0

0_11011011_1101100110_0010010110_1

0_11011100_0011100110_0011100110_0

0_11011101_1011100110_0100010110_1

0_11011110_0111100110_1000010110_1

0_11011111_1010110110_0101000110_1

0_11100000_1001110001_0110001110_0

0_11100001_0111010001_1000101110_0

0_11100010_1011010001_0100101110_0

0_11100011_1100011110_1100010001_1

0_11100100_1101010001_0010101110_0

0_11100101_1010011110_1010010001_1

0_11100110_0110011110_0110010001_1

0_11100111_1110001110_0001110001_1

0_11101000_1110010001_0001101110_0

0_11101001_1001011110_1001010001_1

0_11101010_0101011110_0101010001_1

0_11101011_1101001110_1101001000_1

0_11101100_0011011110_0011010001_1

0_11101101_1011001110_1011001000_1

0_11101110_0111001110_0111001000_1

0_11101111_0101110001_1010001110_0

0_11110000_0110110001_1001001110_0

0_11110001_1000110111_1000110001_1

0_11110010_0100110111_0100110001_1

0_11110011_1100101110_1100100001_1

0_11110100_0010110111_0010110001_1

0_11110101_1010101110_1010100001_1

0_11110110_0110101110_0110100001_1

0_11110111_1110100001_0001011110_0

0_11111000_1100110001_0011001110_0

0_11111001_1001101110_1001100001_1

0_11111010_0101101110_0101100001_1

0_11111011_1101100001_0010011110_0

0_11111100_0011101110_0011100001_1

0_11111101_1011100001_0100011110_0

0_11111110_0111100001_1000011110_0

0_11111111_1010110001_0101001110_0

1_00011100_0011110100_1100001011_0

1_00111100_0011111001_1100000110_1

1_01011100_0011110101_1100001010_1

1_01111100_0011110011_1100001100_1

1_10011100_0011110010_1100001101_0

1_10111100_0011111010_1100000101_1

1_11011100_0011110110_1100001001_1

1_11111100_0011111000_1100000111_0

1_11110111_1110101000_0001010111_0

1_11111011_1101101000_0010010111_0

1_11111101_1011101000_0100010111_0

1_11111110_0111101000_1000010111_0