电子竞赛1——基于DDS的AM信号发生器

工程获取:下载地址

- 课题要求

产生AM调幅波;

要求:载波10K,被调制波1K;

短按键1(pin_143)改变该调幅波的调制度:25%、50%、75%;

长按按键1(pin_143)改变被调制信号频率:1K、1.5K、2K、2.5K;

- 方案设计与论证

- DDS工作原理

DDS建立在采样定理基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。DDS与基于PLL的频率合成器相比具有简便、精确、快速、廉价和灵活等优点。

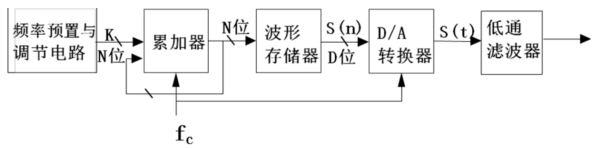

DDS基本原理框图如图2.1所示:它主要由相位累加器、波形存储器、D/A 转换器和低通滤波器构成。

图2.1 DDS基本原理框图

DDS 工作时,在时钟脉冲Fs的控制下对频率控制字X 用累加器进行处理以得到相应的相位码,然后由相位码寻址波形存储器进行相位码―幅度编码变换,再经过D/A 数模变换器得到相应的阶梯波,最后经过低通滤波器对阶梯波进行平滑处理即可得到由频率控制字X决定的频率可调的输出波形。参考频率源一般是高稳定的晶体振荡器,用于DDS 中各部件的同步工作,因此DDS 输出的合成信号频率稳定度与晶体振荡器是相同的。在标准频率参考源的控制下,频率控制字X可决定相应的相位增量,相位累加器则以步长X进行线性累加,相位累加器积满时就会产生一次溢出,从而完成一个周期性动作,这个动作周期即是DDS合成信号的一个周期。

2、AM调制

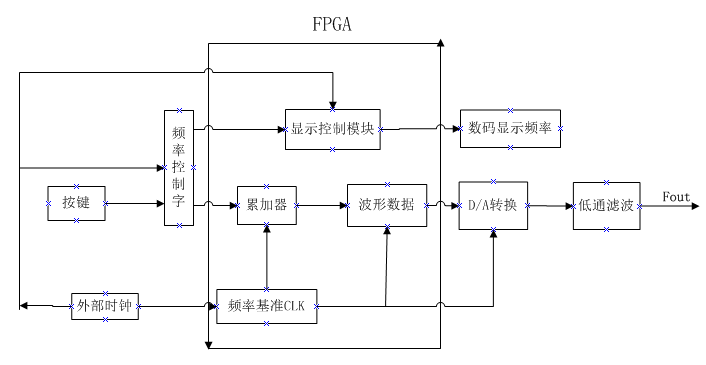

AM调制可以由硬件电路实现,也可由软件实现。由于本课题采用FPGA,在使用FPGA设计DDS系统时,要在满足系统要求和保持DDS 原有优点的基础上,尽量减少硬件复杂性。因此AM调制应在FPGA内部完成,把调制信号添加直流分量后与载波相乘。所设计DDS 的系统结构框图如图1.2.2 所示:

图2.2 DDS系统结构框图

取采样频率为载波频率的4倍。即Fclk=4*Fc=4*10000=40KHz。由于使用的FPGA芯片的晶振频率为20MHz,所以需要对其进行分频操作,并对每个正弦波采样256点。假设波峰为FFH,波谷为00H,每个采样点的取值可由公式Y=128*Sin(2π*)+128算出。

三、单元电路设计

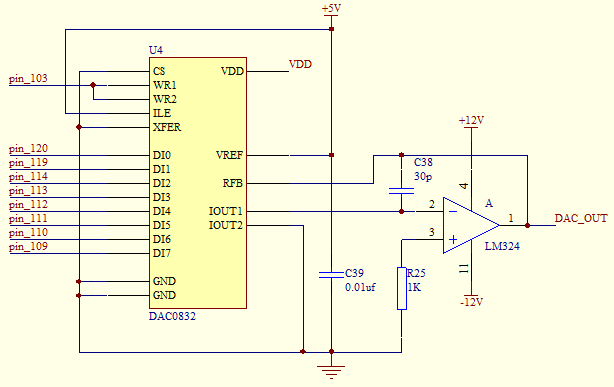

3.1 DAC0832模块

DAC0832芯片以其价格低廉、接口简单、转换控制容易等优点,在嵌入式应用系统中得到广泛的应用。本设计中,DAC0832把FPGA实验板输出的8路数字信号转换成模拟信号,原理图如图3.1所示:

图3.1 DAC0832模块

D/A转换结果采用电流形式输出。若需要相应的模拟电压信号,可通过一个高输入阻抗的线性运算放大器实现。运放的反馈电阻可通过RFB端引用片内固有电阻,也可外接。

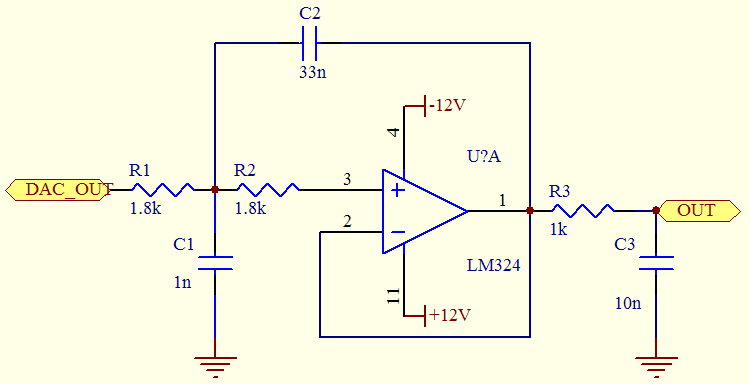

3.2 三阶低通滤波器

DAC0832模块输出的信号含有高次谐波分量,需要用滤波器滤除。本设计采用三阶低通滤波器,该滤波器由一个二阶巴特沃斯低通滤波器和一个一阶无源RC低通滤波器组成。其原理图如图3.2所示:

图3.2 三阶低通滤波器

取截止频率略高于一次谐波频率(15.3KHz),由公式Fc1=,Fc2=,计算得R1=R2=1.8K,C1=1n,C2=33n,C3=10n,R3=4.3K。

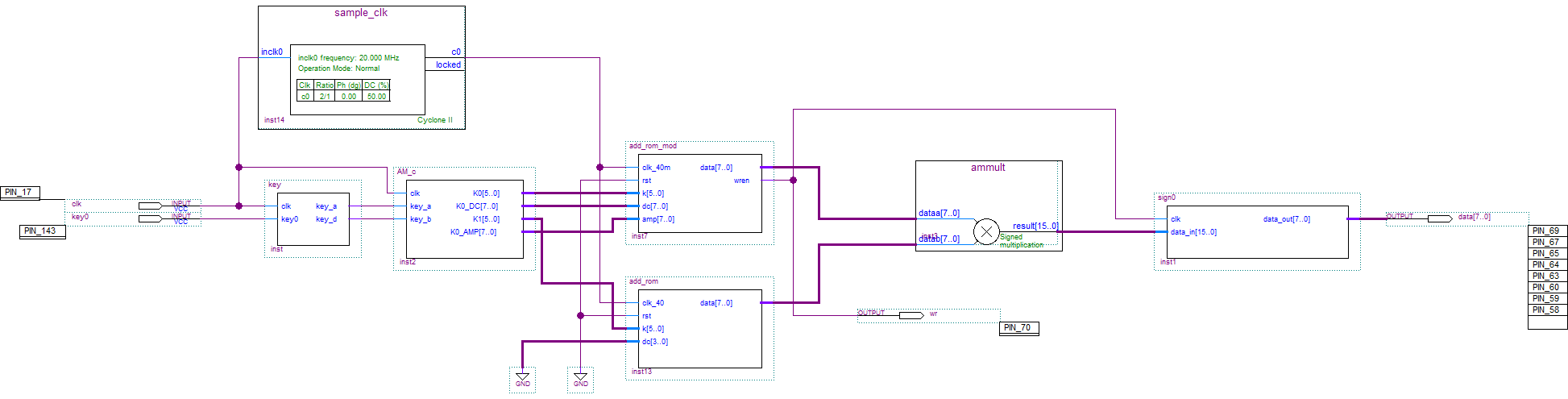

四、软件设计

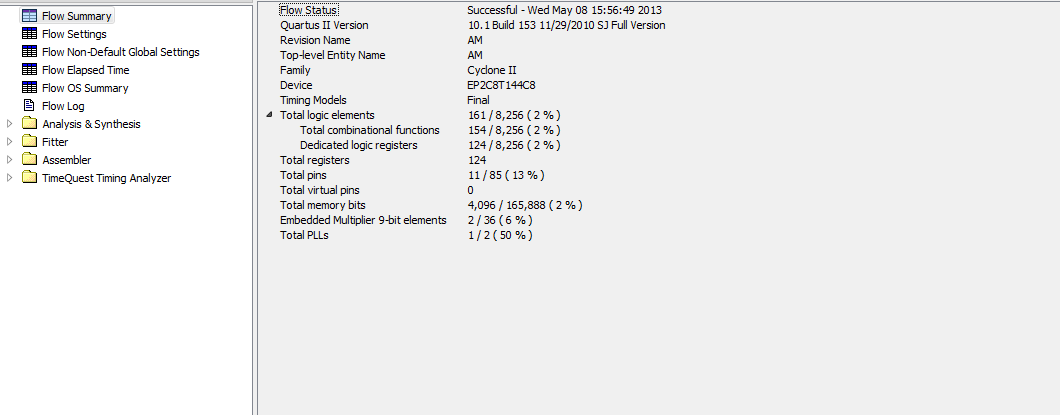

题目中要求载波的F=10khz,调制波的F分别为1khz,到2.5khz,步进为0.5khz,合成方法采取DDS数字合成方法,选择采样频率为64khz,本项目采样的FPGA板是EP2C8,实验板晶振的大小为20MHZ,为了得到精确的采样的时钟,采用PLL锁相环,DDS中rom数据选用有符号数的正弦波,数据宽度为8,深度256,DAC芯片采用DAC0832。以下是软件的框图:

FPGA资源消耗情况:

五、系统测试

1、测试仪器

直流稳压电源 GPS3303

示波器 YB4365

2、测试波形

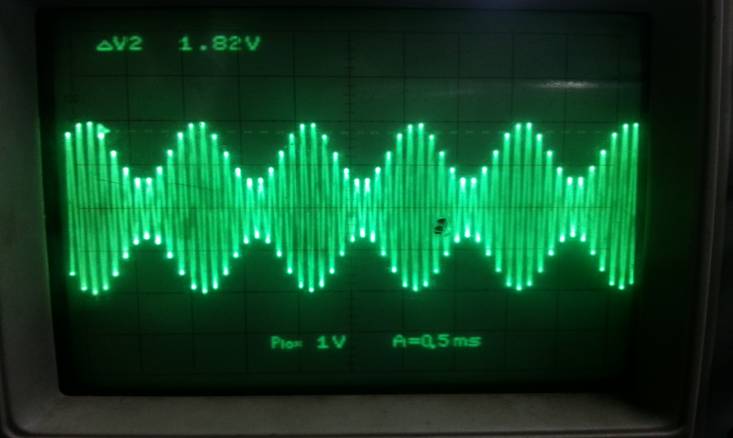

(1)调制度

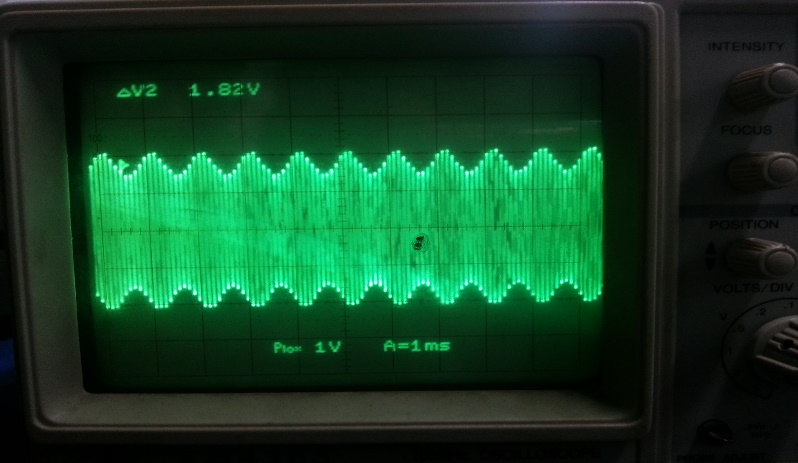

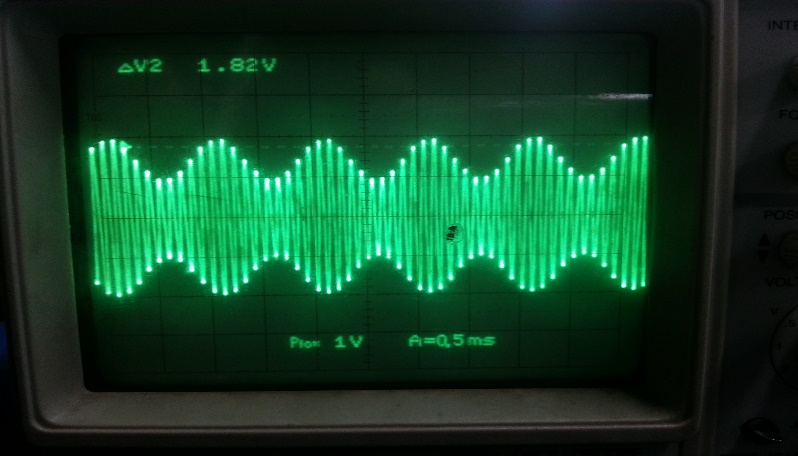

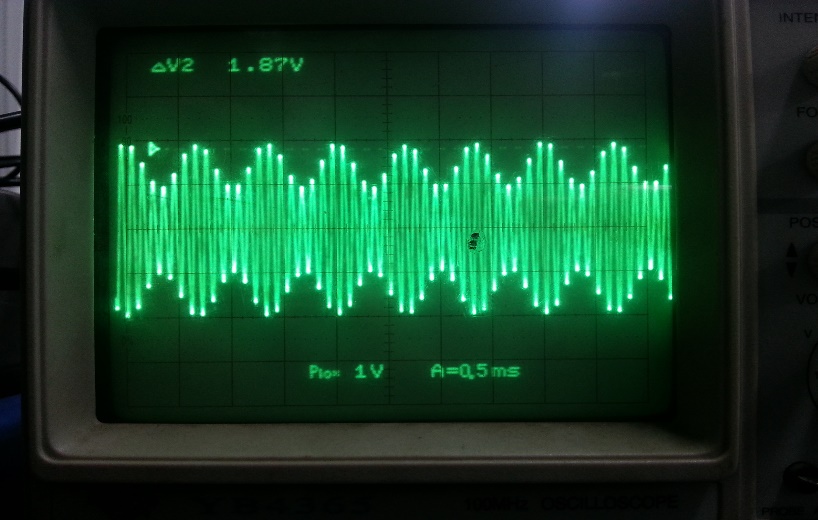

选取调制频率为1KHz,测得不同调制度的信号波形如表5-1所示:

|

调制度:25% |

|

调制度:50% |

|

调制度:75% |

表5-1 调制度

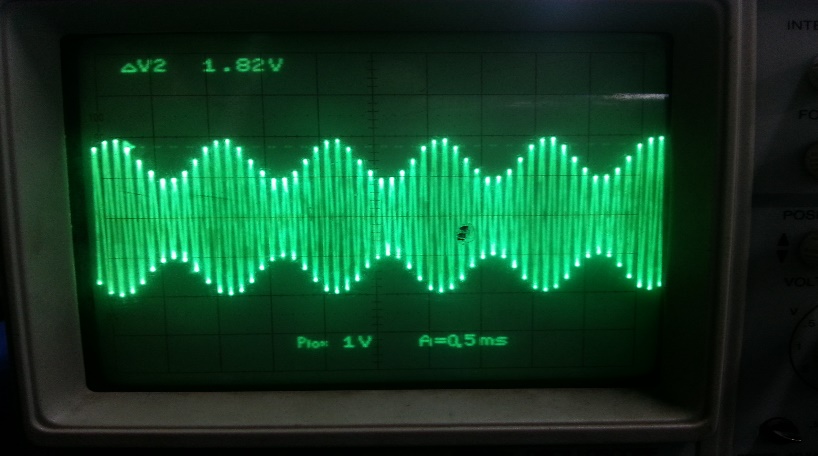

(2)调制信号频率

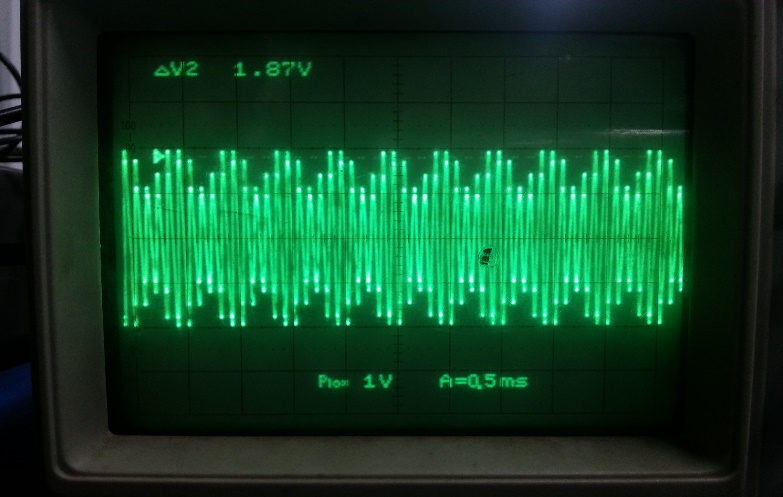

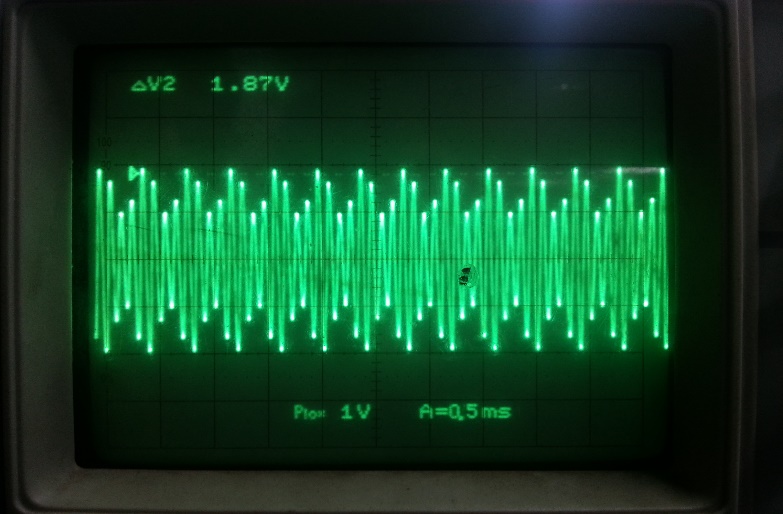

选取调制度为50%,测得不同调制频率下的信号波形如表5-2所示:

|

调制信号频率:1KHz |

|

调制信号频率:1.5KHz |

|

调制信号频率:2KHz |

|

调制信号频率:2.5KHz |

表5-2 调制信号频率