FPGA JTAG接口保护电路

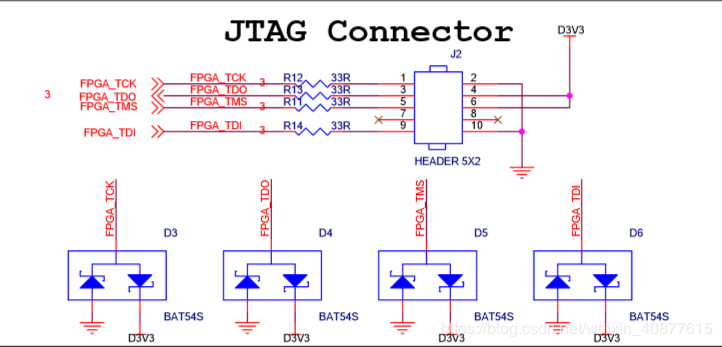

手头上两块FPGA开发板(黑金和正点原子)的FPGA接口部分设计略有不同,黑金的开发板特别在接口上加了保护电路。如图:

使用BAT54钳位。

查了下网上确实有人反映ALTERA的FPGA的JTAG接口IO容易损坏,有人怀疑了ALTERA为了省成本将内部钳位电路优化掉了,导致这一原因,所以外部加上这部分钳位电路。

1.这里就有一个疑问,一般的接口保护电路多采用TVS管来做。那这里是否可以用TVS来保护?

原理上,我想是可以的。但在TVS管的元器件选型上,竟然很难找到5V以下的TVS管。

2.为什么没有5V以下的TVS管?

这是网上答案------10V是最大脉冲峰值电流情况下的最大箝位电压,一般情况下会低于这个值。

国标规定的冲击波形持续时间都是μs级的,也就是说后端电路承受的10V左右的电压只有几十个μs左右,一般情况下是可以承受的,不然3.3V的TVS管肯定卖不出去了

TVS的箝位电压不可能像稳压管那么精确

所以关于保护电路就可以这样分析,芯片一般内部自带了钳位保护电路,而接口部分使用TVS管。当外部静电放射ESD,由TVS管进行初级吸收,钳位电路次级保护。

posted on 2020-05-13 16:48 xzj19870125 阅读(3929) 评论(0) 编辑 收藏 举报

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· 开发者必知的日志记录最佳实践

· SQL Server 2025 AI相关能力初探

· Linux系列:如何用 C#调用 C方法造成内存泄露

· AI与.NET技术实操系列(二):开始使用ML.NET

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 【自荐】一款简洁、开源的在线白板工具 Drawnix

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· Docker 太简单,K8s 太复杂?w7panel 让容器管理更轻松!