Verilog-ams语法解析

Verilog – AMS 语法解析(1)电阻

在使用SIMpiles时候会用到一些Verilog A的代码,这个系列相当于LTspice的Sub circuit 系列。希望能帮助大家更快的完成工作有时间整点活。

本期解析代码如下

module hello_world ; analog begin @(initial_step) $strobe("Hello World!") ; end endmodule |

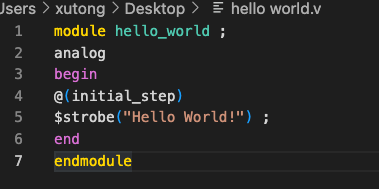

参考代码1

图1:参考代码1

第一行

代表定义一个模块,模块名称为hello_world

最后一行

代表结束这个模块的定义

第三行和第六行代表

这个执行顺序是按照顺序来执行的,先执行第4行在执行第五行

而initial_step则表示下面的代码只在分析一开始的时侯运算,不会每次都运算

第二行

Analog 关键字引入了模拟的运算过程,代表这个信号始终是连续的在Hello world的这个例程里面并没有太大感觉。

第五行

$strobe(“hello world”);其实相当于C语言的Printf

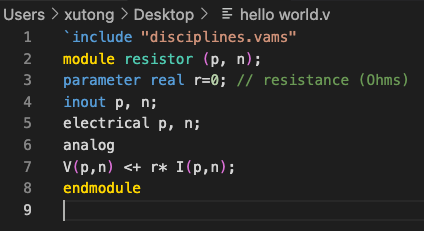

`include "disciplines.vams" module resistor (p, n); parameter real r=0; // resistance (Ohms) inout p, n; electrical p, n; analog V(p,n) <+ r* I(p,n); endmodule |

参考代码2

图2:参考代码2

因为Verilog A 不止用于描述电路也能描述其他东西,这里的disciplines.vams 代表一个头文件,和C语言的头文件是一个意思,里面已经实现了一些功能模块

第2行和Verilog 一样他也有输入输出端口,在这里p 和n是他的端口,在这里这个端口是inout型代表他们又是输入又是输出。

防自动大写electrical p,n代表p,n是电气相关的端口,意味着这个端口的输入的是电压/电流信号

防自动大写 analog 代表以下的表达式是表述模拟信号的,就是表示下面的表达式是连续变化的。

以下引用:THE DESIGNER’S GUIDE TO VERILOG-AMS

“模拟关键字引入了模拟过程。模拟过程用于描述连续时间行为。从句法上讲,它是一个模拟关键字,后跟一个描述信号之间关系的语句。这种关系在任何时候都必须是真实的。在这种情况下,定义端口信号之间关系的语句是贡献语句。贡献语句采用贡献运算符左侧的分支信号的形式,“<+”,然后是右侧的表达式 。”

<+ 的意思可能表示的是两边的代码在任何时刻都是相等的,可以从左到右也可以从右到左,具体我们到时候可以将电阻的Verilog A 模块开始去观察其变化。

另提一嘴,在Verilog A 里面 parameter 有两种类型,一种是integral另外一种是real,real用于给这些电路器件参数。

在描述p,n的电压电流关系时候和LTspice要看 a,b的电压是一样的,只需要描述成V(a,b)即可,电流的关系式也是一样的。

参考文档

THE DESIGNER’S GUIDE TO VERILOG-AMS

SIMetrix Verilog A Manual