(8)逻辑综合

一、概述

定义:综合是将行为描述的电路、RTL级电路转化为门级的过程

目的:决定电路的门级结构,寻求功耗、时序和面积的平衡,增强电路的测试性

工具;Design Compiler

二、具体过程

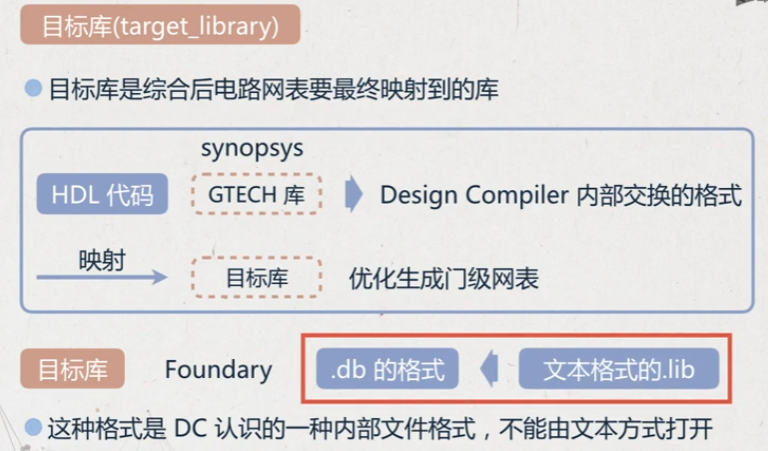

转译:DC将Verilog代码描述转化为DC自己内部的一个数据库,该数据库与工艺库是独立无关的

优化:DC根据设计者施加的约束(工作频率、面积、功耗等)对读取的代码进行优化,从而推断出满足设计指标的门级网表

映射:将该门级网表映射至晶圆厂给定的工艺库上,最终形成该工艺库对应的门级网表

三、设计对象

design:待综合的电路

port:整个design最外部输入或输出的端口

clock:时钟(单独处理)

cell:被例化的模块,原电路则成为references,自身的引脚称为pin

net:内部连线

四、时序路径

在逻辑综合过程中,其内部会有一个静态分析引擎,能够将电路划分为不同的时序路径,起点为input port和clock,终点为寄存器(数据)D端和output port。依据起点和终点,将电路划分为四种不同的时序路径(具体划分方法参考之后的静态时序分析专题)

指标:

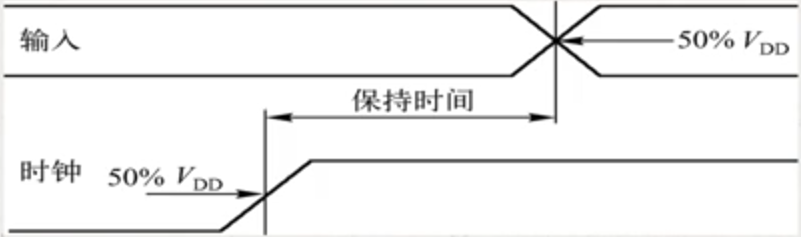

建立时间(setup time):时钟上升沿之前数据需要稳定的时间

保持时间(hold time):时钟上升沿之后数据依然需要稳定的时间

五、DC综合流程

1.DC启动

四种方式:

dc_shell:命令行方式

dc_shell-t:命令行方式,以tcl方式为基础

design_analyzer

design_vision:图形界面方式

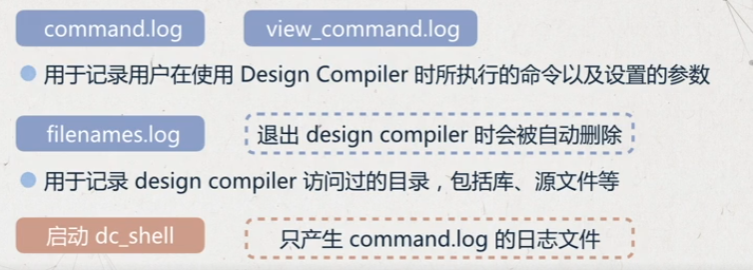

DC在启动时会自动在启动目录下创建日志文件:

2.读入设计文件

三种命令的区别:

3.link链接

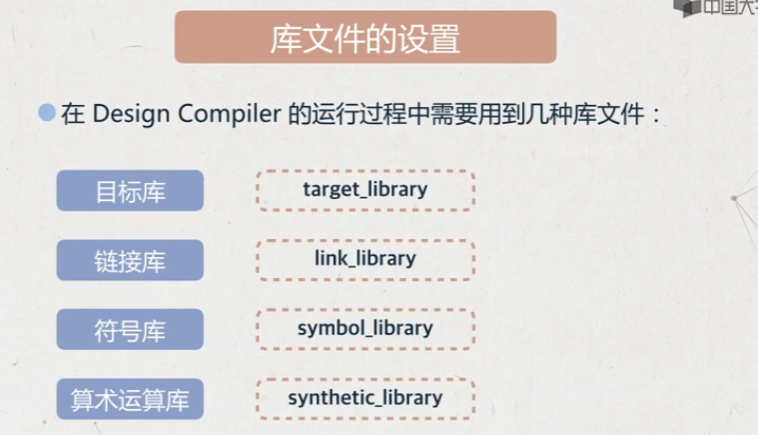

4.工艺库设置

/*****************************************************************************************************/

目标库与链接库的区别:链接库主要对应的是IP(购买的付费IP、存储器、IO、PAD等),目标库更多的指的是标准单元

/*****************************************************************************************************/

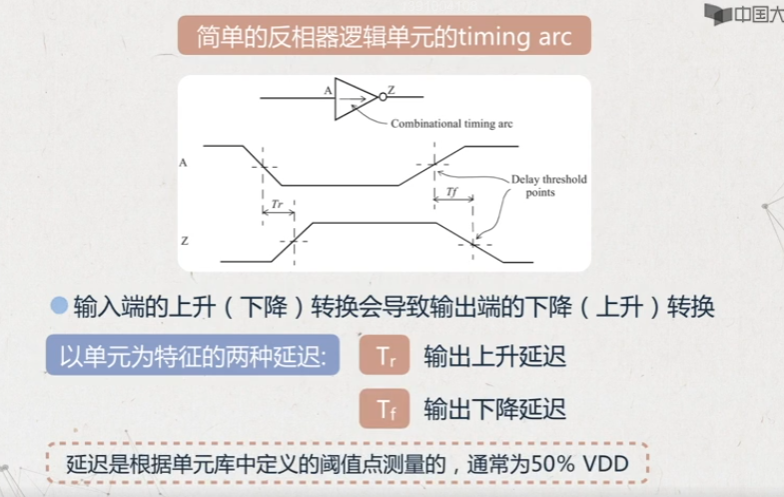

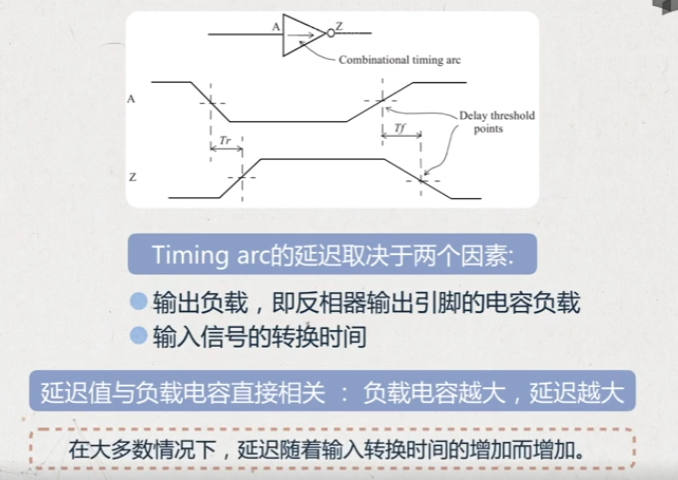

工艺库中标准单元的时序模型:

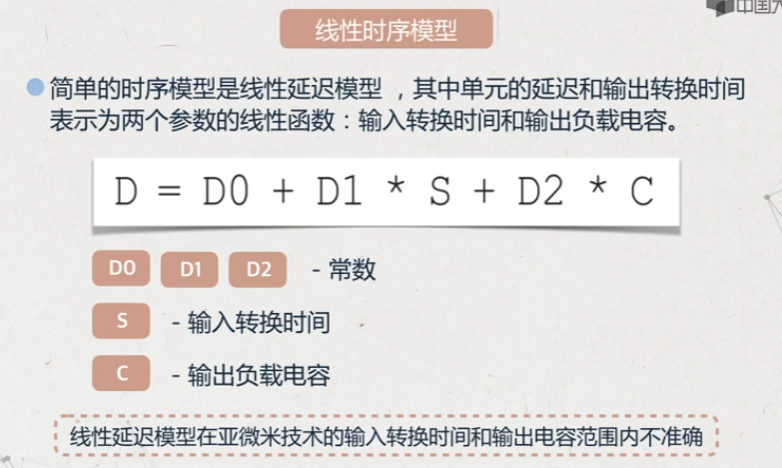

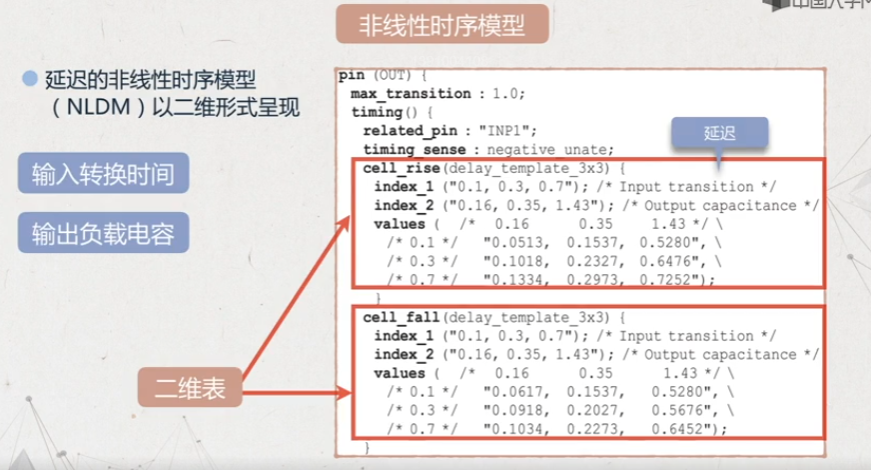

标准单元的时序模型分为线性与非线性两种:

描述了从引脚INP1到输出out的上升延迟cell_rise与下降延迟cell_fall模型,以及引脚out上的max_transition允许时间

此查找表模版指定的第一个变量是输入转换时间,第二个变量是输出负载电容。每个单元有3个条目,因此对应一个3x3的查找表

如果索引不在表中,则通过插值的方法计算延迟

附:

该课程所讲的dc更多的还是理论,本人建议大家还是实际安个虚拟机去实际操作一下,这里推荐一个入门教程:

综合工具-Design Compiler使用(从RTL到综合出各种报告timing\area\critical_path) - 哔哩哔哩 (bilibili.com)