(11.3)iic串口读写EEPROM实验:程序设计

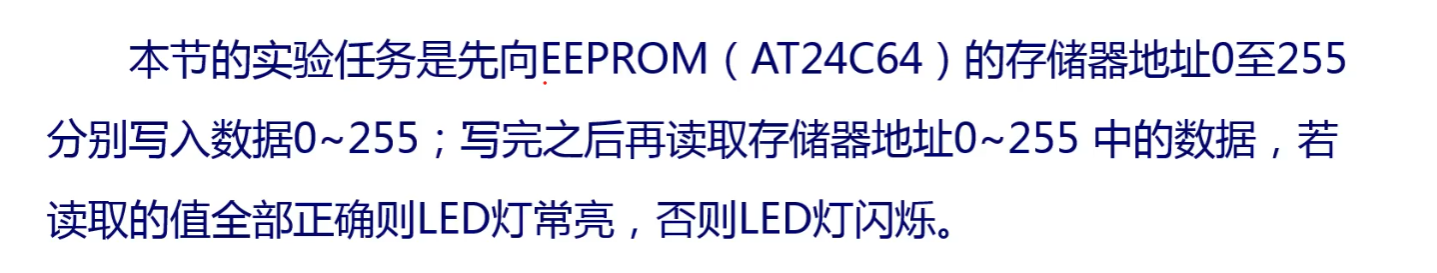

一、实验任务

二、架构框图

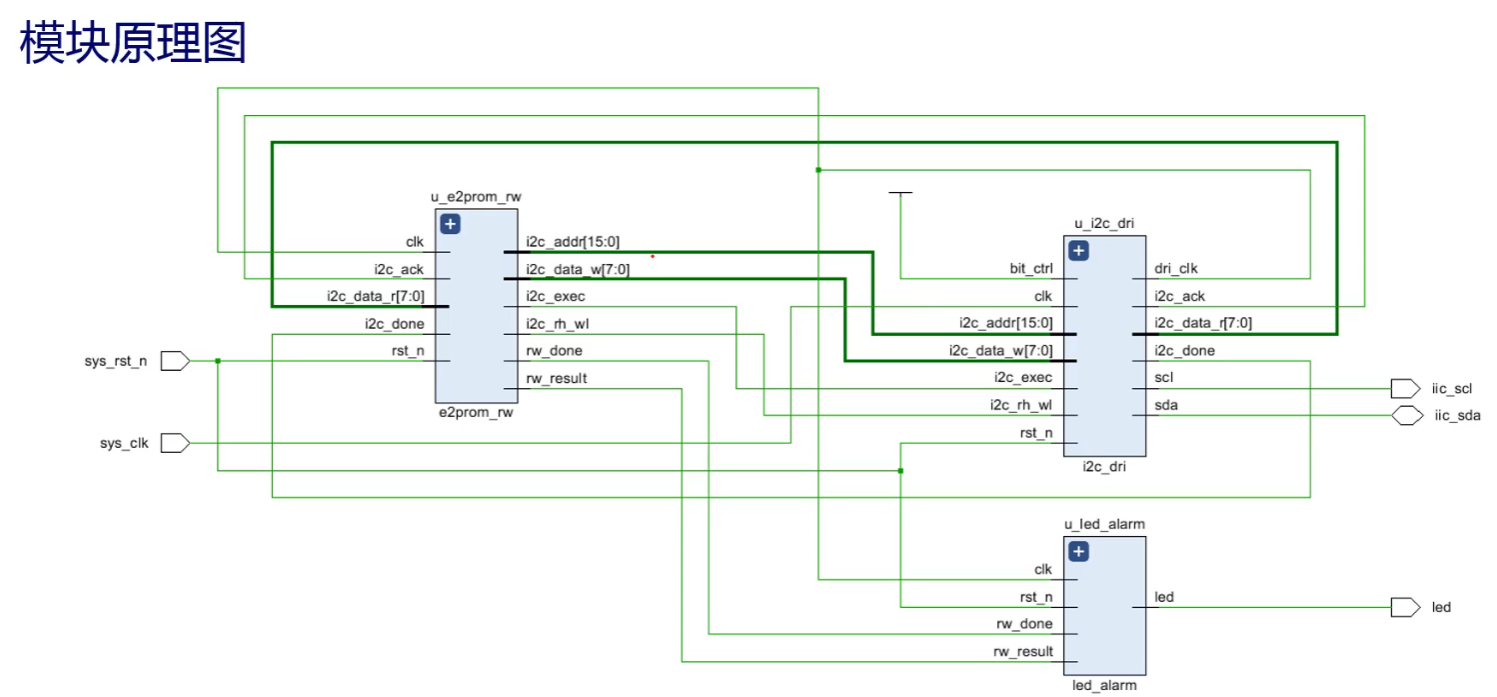

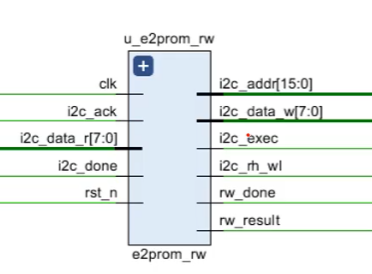

其中:

i2c驱动模块:

bit_ctrl:0代表发送8位字节地址;1代表发送16位字节地址(本实验采用)

i2c_addr[15:0]:16位字节地址,当bit_ctrl为0时只有低8位是有效的

i2c_data_w[7:0]:向EEPROM写入的8位数据

i2c_exec:拉高代表当前进行一次i2c的读操作或写操作

i2c_rh_wl:i2c_exec拉高之后,若为高电平则进行一次读操作,低电平则进行一次写操作

dri_clk:输出的一个低频时钟

i2c_ack:应答信号,用于指示i2c器件有没有应答(在读写器件,必须所有要求的应答位都应答,最终输出的ack才为0)

i2c_data_r[7:0]:EEPROM读出的8位数据

i2c_done:当前信号操作完成后信号拉高

scl、sda:连接到从器件的两根引脚

用于控制u_i2c_dri模块,在读取的过程中会判断读取的值和写入的值是否一致,输出rw_done(读写操作完成)与rw_result(读写操

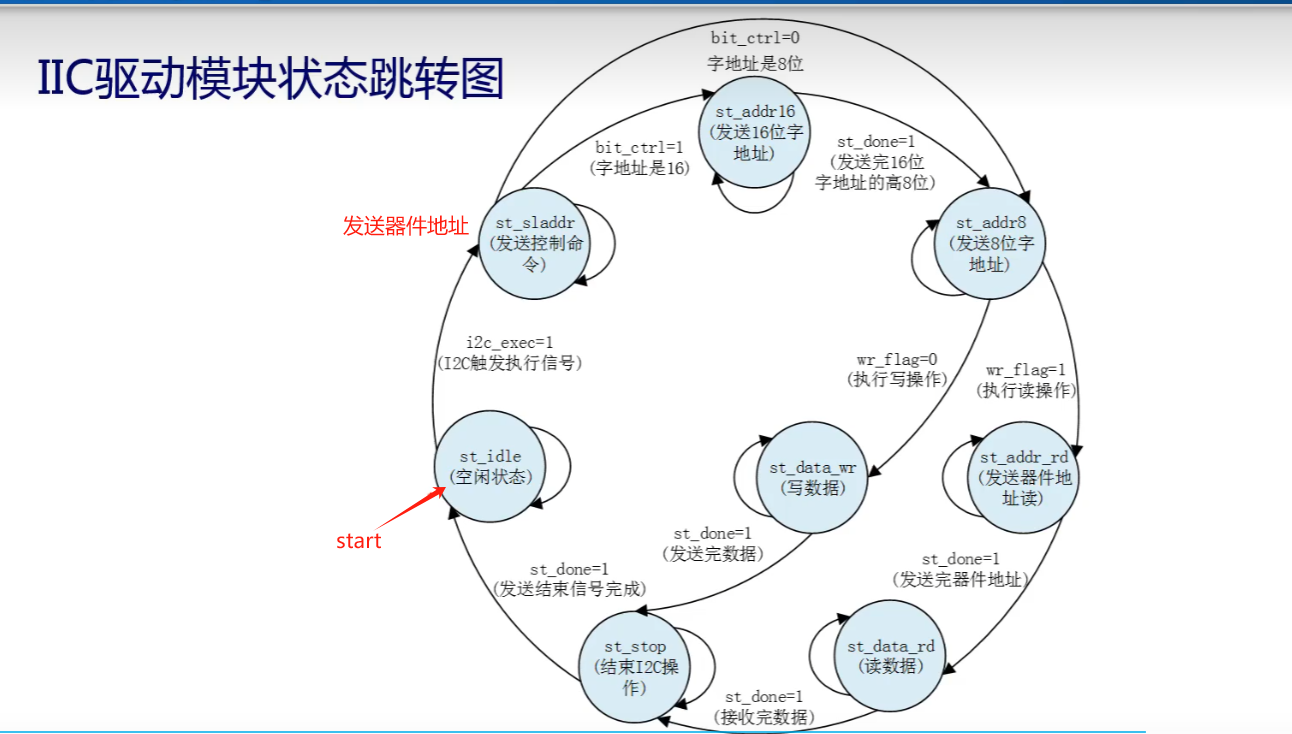

三、状态机图

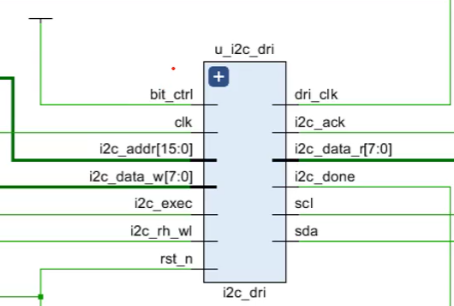

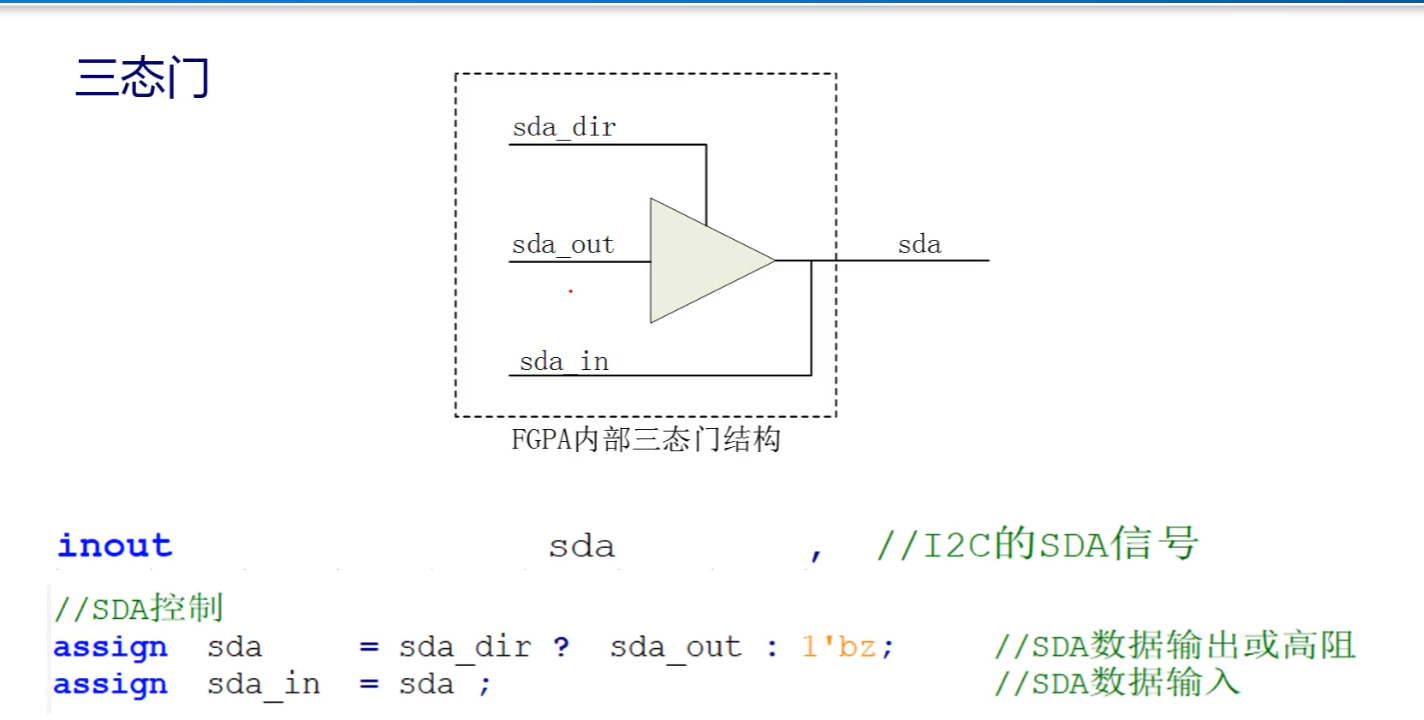

四、FPGA内部三态门

当sda_dir为高电平时,sda_out与sda信号直连;为低电平时,代表将sda信号作为输入,不让sda_out信号驱动,此时sda_out与sda之间是一个高阻的状态,相当于断开了,断开之后可以通过sda_in引脚读取sda的信号

因此,sda_out用于主机向EEPROM从机写入数据;sda_in用于主机从从机EEPROM读取数据

五、代码

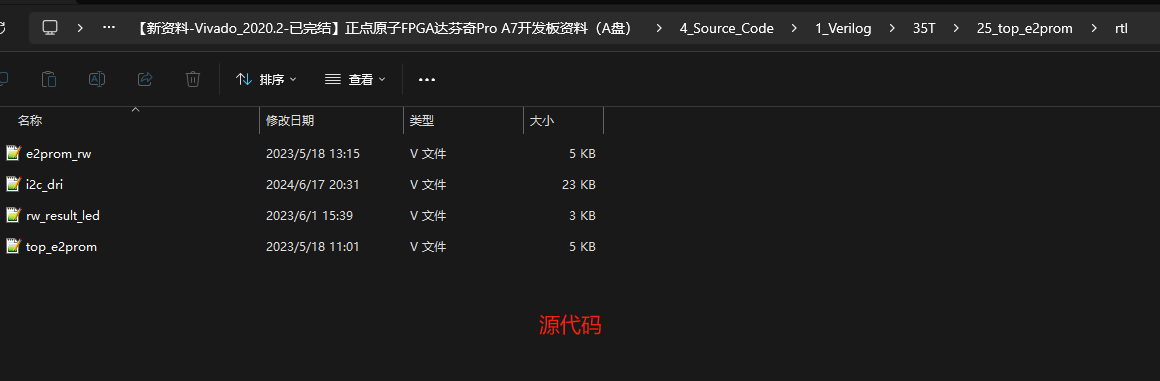

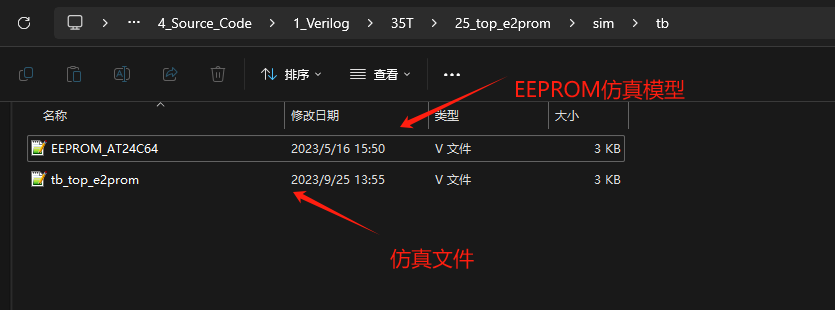

略,位置位于资料目录“F:\【新资料-Vivado_2020.2-已完结】正点原子FPGA达芬奇Pro A7开发板资料(A盘)\4_Source_Code\1_Verilog\35T\25_top_e2prom”

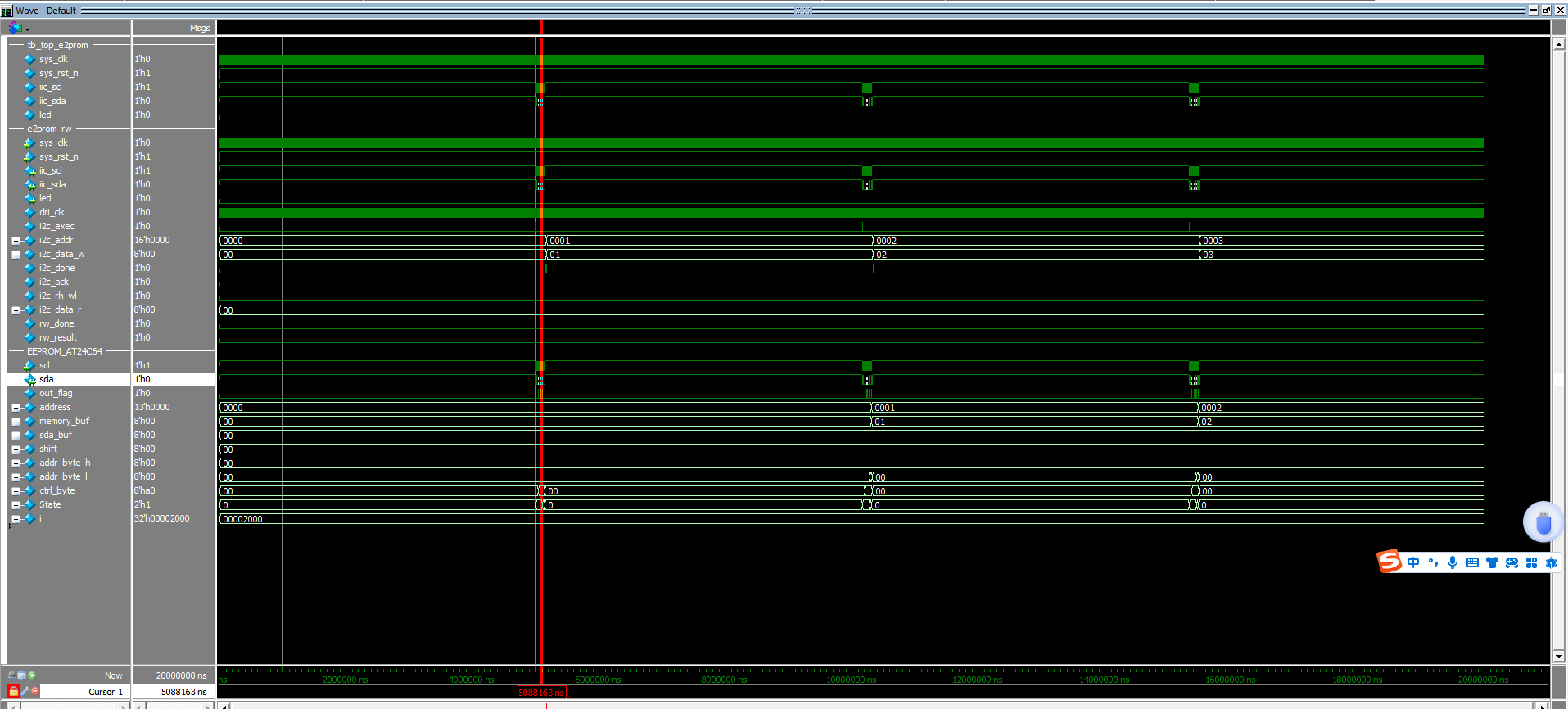

六、波形仿真