(2)高质量Verilog HDL描述方法

一、Verilog HDL概述

Verilog HDL的功能之一是描述可综合的硬件电路,与c相比,HDL语言具有以下特点:

- 互连:wire型变量描述各个模块的端口与网线的连接关系

- 并发:有效描述并行的硬件系统

- 时间:定义了绝对和相对的时间余量,可综合操作符具有物理延迟

通常不可综合的关键字用于书写testbench

二、在RTL书写中如何考虑延迟、功耗和面积?

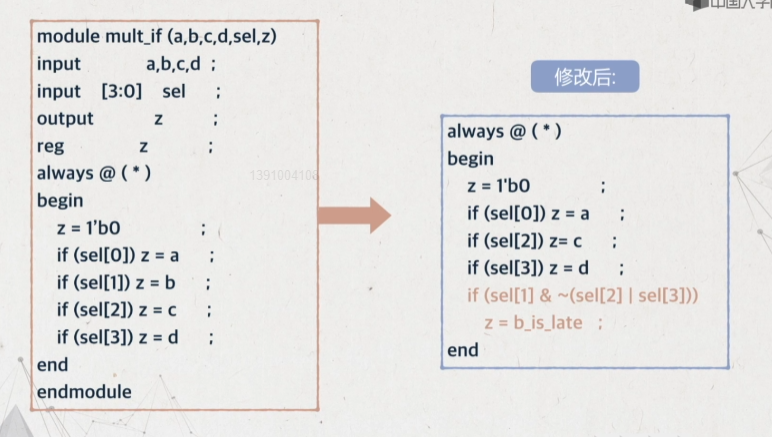

- 多路选择器如果个别信号到来比较晚,则将延迟较大的分支单独拿出来放在,放在离出口最近的选择器中

当b信号延迟时,将b所在的分支放在后面,但若仅仅把这条语句置后,那和原逻辑是冲突的,因此需要把满足z=b的所有条件都考虑到

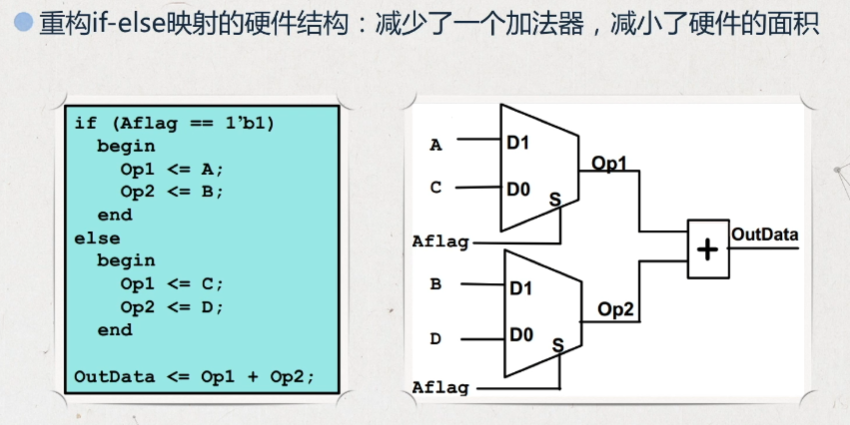

- 注意“先加后选”和“先选后加”对数据通道的影响

但这样并不意味着第二个电路好:在第一个电路中,数据通道是一个加法器和一个选择器,控制通道只有一个选择器;在第二个电路中,数据通道是一个加法器和一个选择器,而控制通道变为一个加法器和一个选择器之和,因此第二个电路的控制通道延迟较大,如果控制信号Aflag到来较晚,则第二种电路性能就会比第一种差。因此,在实际设计中要根据需要选择

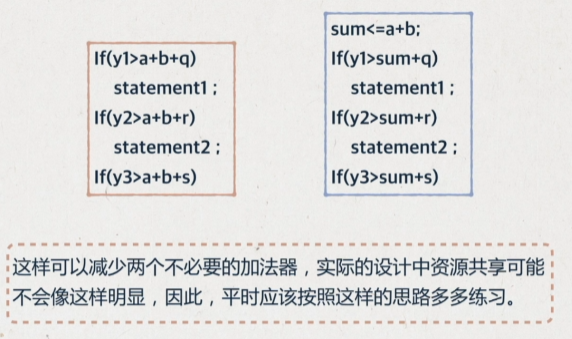

- 重点关注加法器、乘法器等较为复杂的逻辑单元,尽量减少使用

- 在编写RTL代码时尽量考虑资源共享(尽管综合工具在综合时也会采取这种方式进行优化)

对功耗的措施:

电路使能和门控时钟的区别:前者只是使电路内的信号不再变化,时钟信号依旧翻转,而门控时钟则是直接关掉了整个时钟

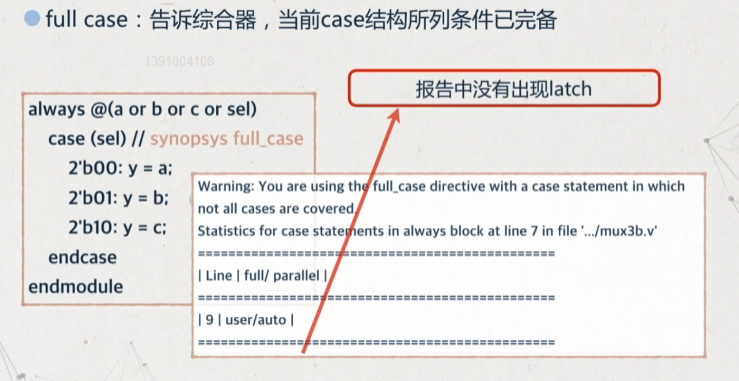

- 使用综合器指令full_case和parallel_case指令(具体可参考文章:"//synopsys full_case parallel_case"综合指令的用法_synopsys full case-CSDN博客):

三、RTL设计指导原则

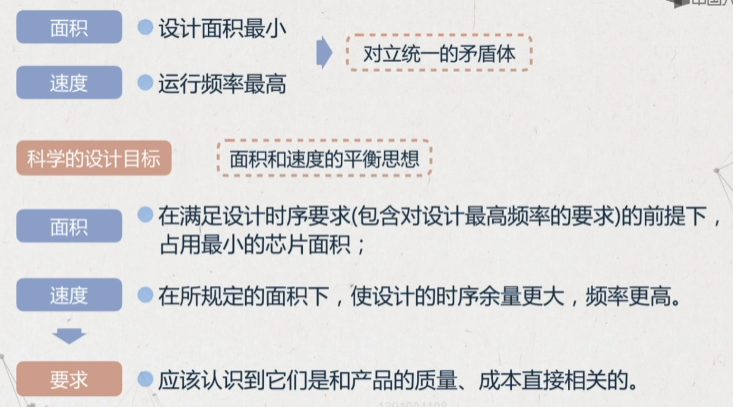

1.面积与速度互换

二者的地位是不一样的,相比之下,满足设计的工作频率和时序更重要一些,因此发生冲突时,速度要比面积更加优先

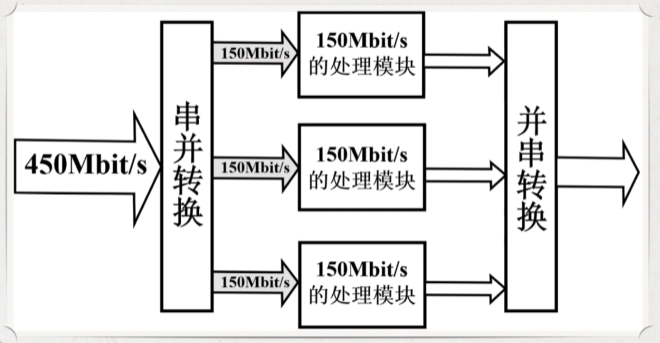

技巧一:串并转换

输入数据流的传输速率为450Mbit/s,在FPGA上设计的数据处理模块的处理最大速度为150Mbit/s,因此至少复制三个模块,同时利用串并转换完成

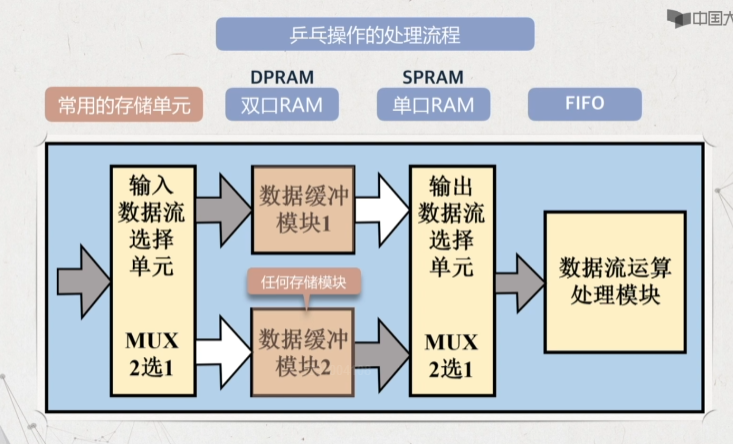

技巧二:乒乓操作

输入数据流选择单元与输出数据流选择单元按节拍相互配合进行切换,将经过缓冲的数据流没有停顿的送入处理模块,具体的操作不再赘述

常用于流水线式算法,完成数据的无缝缓冲与处理

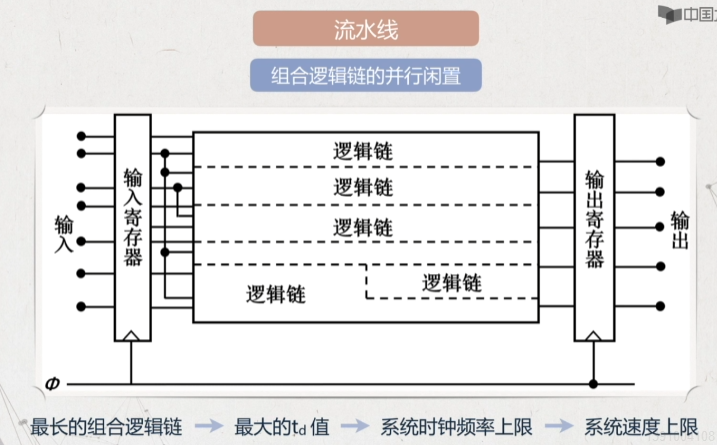

技巧三:流水线设计

Reference

12.1 面积与速度的平衡与互换 · FPGA使用笔记 · 看云 (kancloud.cn)