(1)概述

一、芯片设计制造的五个环节

- 晶圆厂foundry:从事半导体晶圆生产,接受其他设计公司的委托制造芯片,代表公司:TSMC、UMC、SMIC

- 设计公司fabless:fabrication+less,没有制造业务专注于设计的公司,代表有博通、高通、英伟达、华为海思

- EDA软件公司:自动化软件生产厂商,主要为集成电路设计提供软件支持,代表有三大家,国内有华大九天

- Design Service设计服务公司:提供芯片后端设计服务,包括芯原、alchip国芯微等

- IP供应商:由于ip研发成本高且复用性强,一些设计公司为其他公司提供ip服务,代表有arm、s家、c家

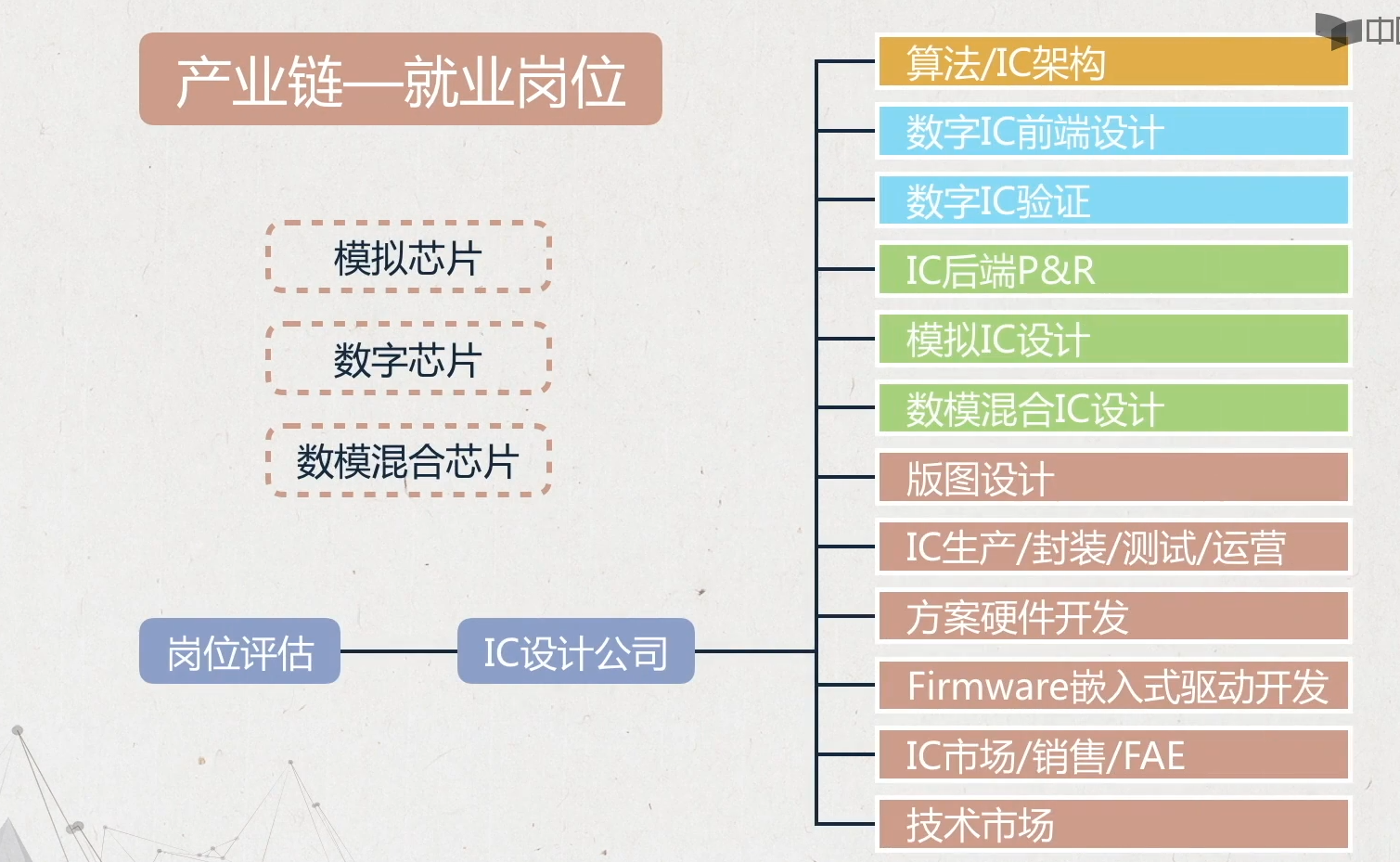

二、ic相关就业岗位

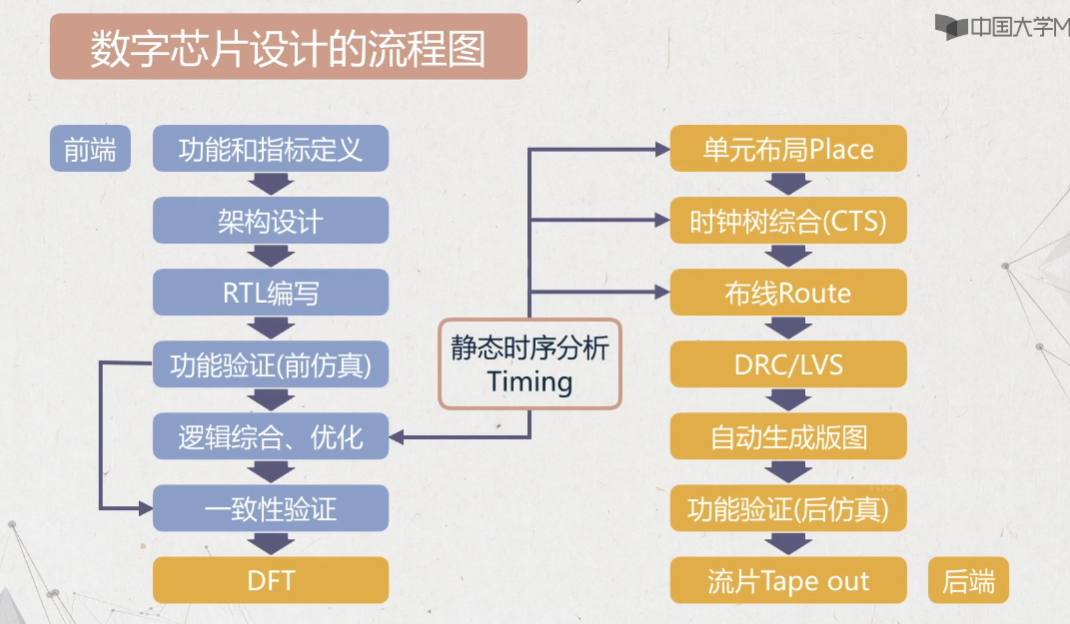

三、数字芯片设计流程

1.算法和架构设计

完成数字芯片中高层次算法或架构的分析和建模,为硬件提供一个正确的软件模型,通过大量高层次的仿真和调试,为RTL的实现提供总体性的设计和指导。

工具:matlab(数字信号处理)、c\c艹、system c、system verilog

2.RTL实现

依据第一步的描述,完成高层次到verilog HDL的实现过程

工具:vim、emac

3.功能验证

通过大量的仿真,发现在电路设计中人为或非人为引起的bug,主要指标是功能覆盖率

工具:modelsim、vcs、nc-verilog

语言:c\c艹、system c、system verilog、基于UVM的方法学等

4.逻辑综合

将RTL代码映射为工艺库相关的网表

工具:DC、RTL compiler

特点:整个逻辑综合是在人为约束下进行的,因此逻辑综合可以看做是一个多目标(面积、频率、性能)多约束的工程优化问题,该步骤通常会插入DFT、clock gating、加入memory、各种ip等,该步骤也可加入PLL、I\O接口等

5.静态时序分析

目的:相对于动态仿真的类穷举式验证而言,从静态分析的角度,保证设计中的所有路径满足内部时序单元对setup time和hold time的要求,即无论起点是什么信号都可以被及时的传递到路径的终点,并且在电路正常工作的必要时间段保持恒定

工具:PT、tempus

特点:从逻辑综合开始,基本上每做一次大的调整,都需要进行一次STA分析,以保证每步都能时序收敛,通常设计中会存在大量的时序违例路径,STA需要修改大量的setup time和hold time,如何修改这些体现了工作经验的重要性。此外,如果是前端修timing违例,一般修的很快,但代码被前端修改后是否还存在新的bug需要重新进行仿真验证,仿真会消耗数以月计的时间,所以不到万不得已,不会找前端去修timing

6.一致性验证

目的:RTL代码和逻辑综合后的网表都可以抽象为由节点和边构成的图,一致性验证采用了类似直接对比两幅图是否一致的方法,来确定逻辑综合生成的网表是否正确

工具:formality、conformal

输入:RTL代码、netlist、约束

输出:match(两张图节点是否一致)和verify(两种图功能是否一致)的报告

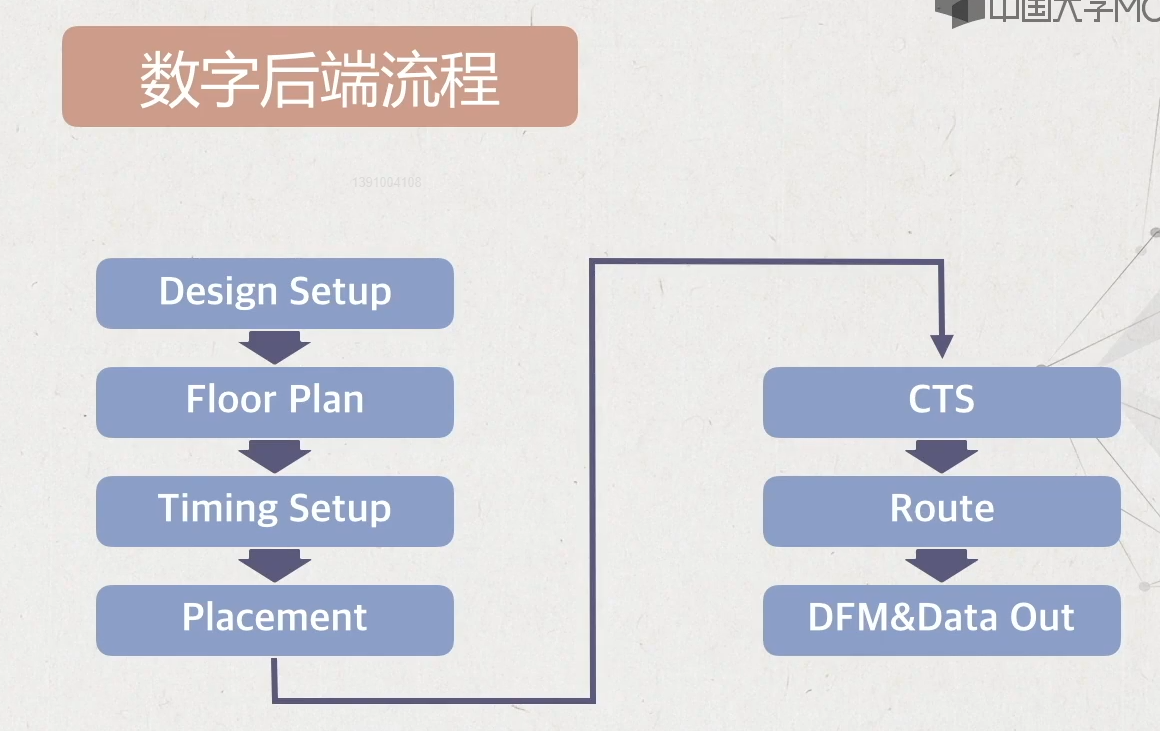

7.数字设计后端

数字后端设计又称物理设计,将网表格式的文本转化为一个个有物理大小和位置的单元、连线,并且在实现过程中要满足面积、性能、功耗的要求

其中

floorplan:将design导入后端工具后检查输入是否缺少或有无错误,确保design正常initial后就可以调整floorplan,目的是确定design的大小、出pin的位置以及所有macro(宏单元)的摆放

placement:将std cell 放入core area的过程,并且满足congestion和timing的要求,简单来说可以分为两步:global和detail pllace:global不考虑cell放的位置是否legal,detail place会将cell放到附近legal的位置上,在place的时候为了得到更好timing的结果会将关键路径进行逻辑重组,删掉buffer trees

preCTS:发生在place之后CTS之前,对setup timing进一步优化,只优化setup是因为clock tree还没做,所有的clock都是ideal的

CTS:芯片中的始终网络要驱动电路中所有的时序单元,因此时钟源端门负载很多,其负载延时很大且不平衡,因此需要插入缓冲器减小负载。时钟网络及其上的缓冲器构成了时钟树

Route:CTS之后整个芯片的大体结构已定,需要信号线通过金属连接起来,绕线过程主要完成以下几个目标:考虑DRC和LVS、绕线完成后不会有DRC和LVS的violations、绕线过程不会导致timing变差、考虑DFM(集成电路可制造性设计),如multi-cut via(互连线通孔)、线宽、线距

8.时序仿真

与功能仿真类似,只是将RTL代码替换为网表,然后加载SDF文件和工艺库模型,目的在于观察芯片在延迟等近似实际工作条件下是否还能正常工作

四、课程参考书目