(7)ram ip使用

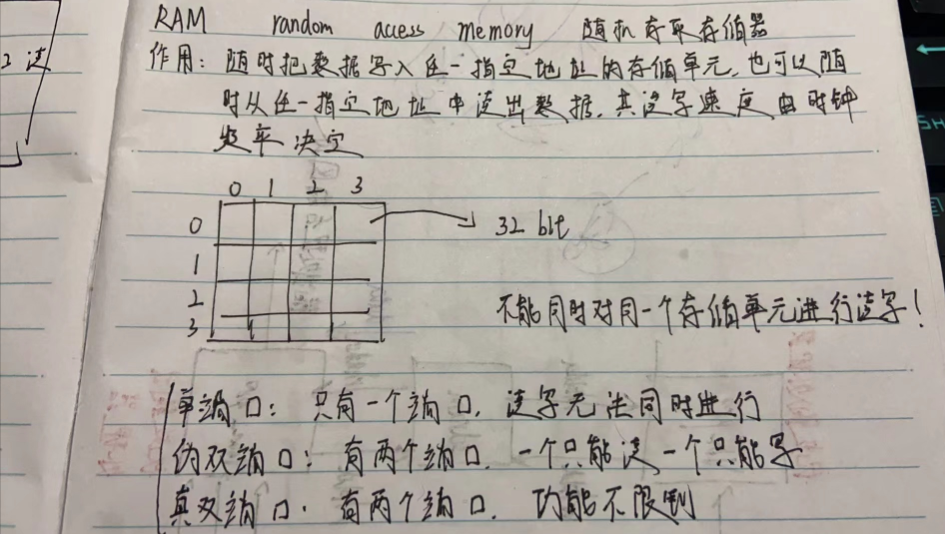

一、ram相关介绍

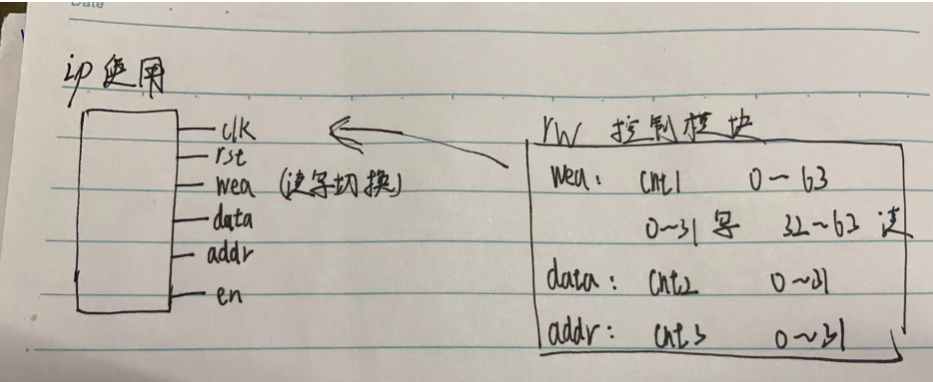

本实验使用一个控制模块对ram ip进行控制(本质上是三个计数器)

二、ip使用

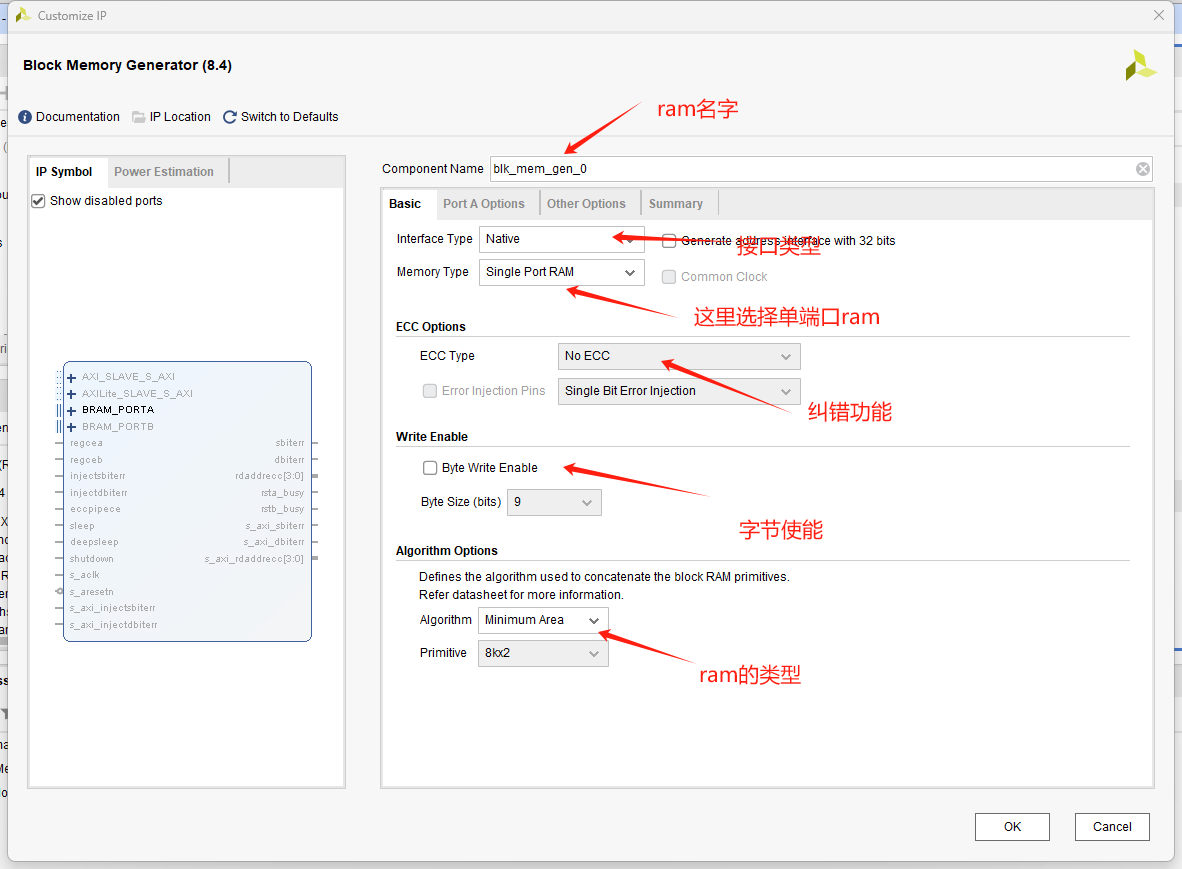

在界面中选择IP catalog,搜索block,选择底下这个,双击即可生成ram的ip

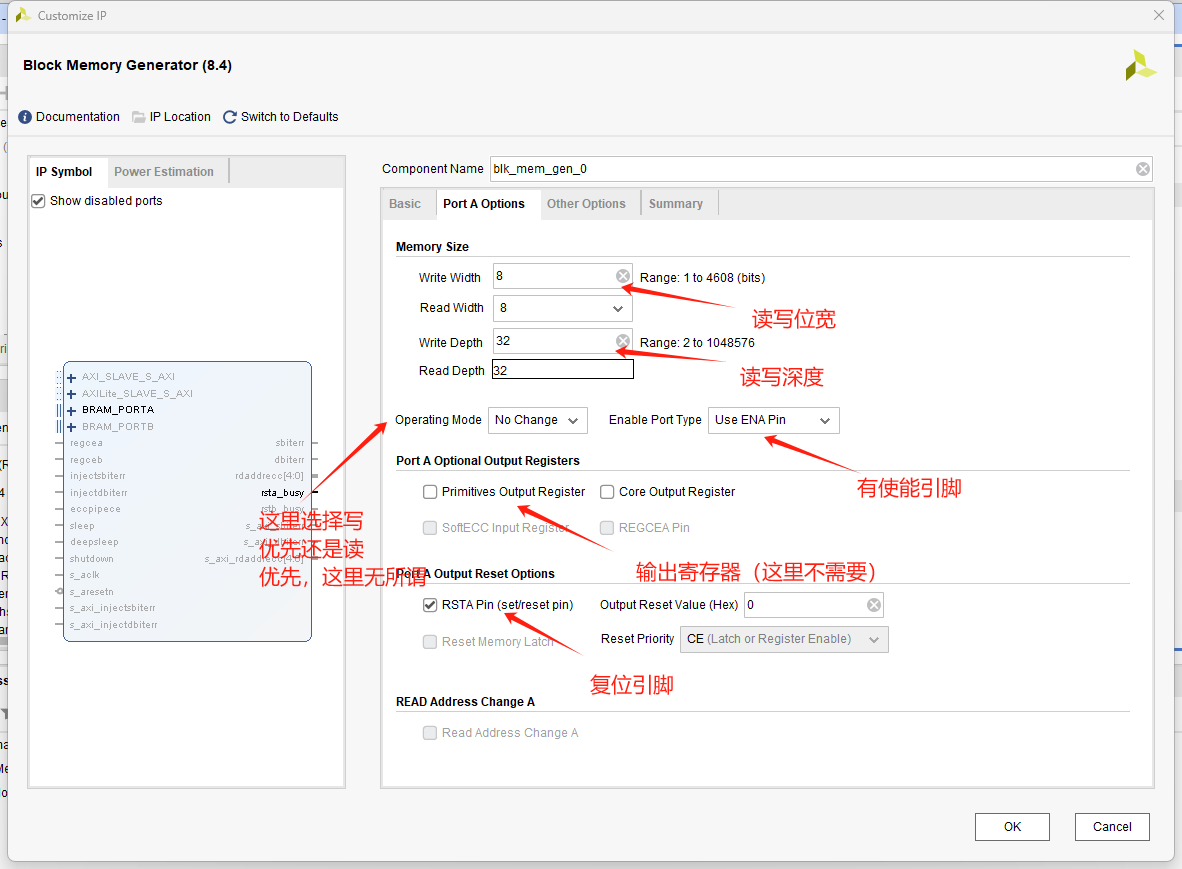

下面进行一些ram资源的配置

配置好后点击ok,生成ip,可以在这里看到已经生成好了:

这里点开这个.veo文件,里面的东西可以当做模版使用

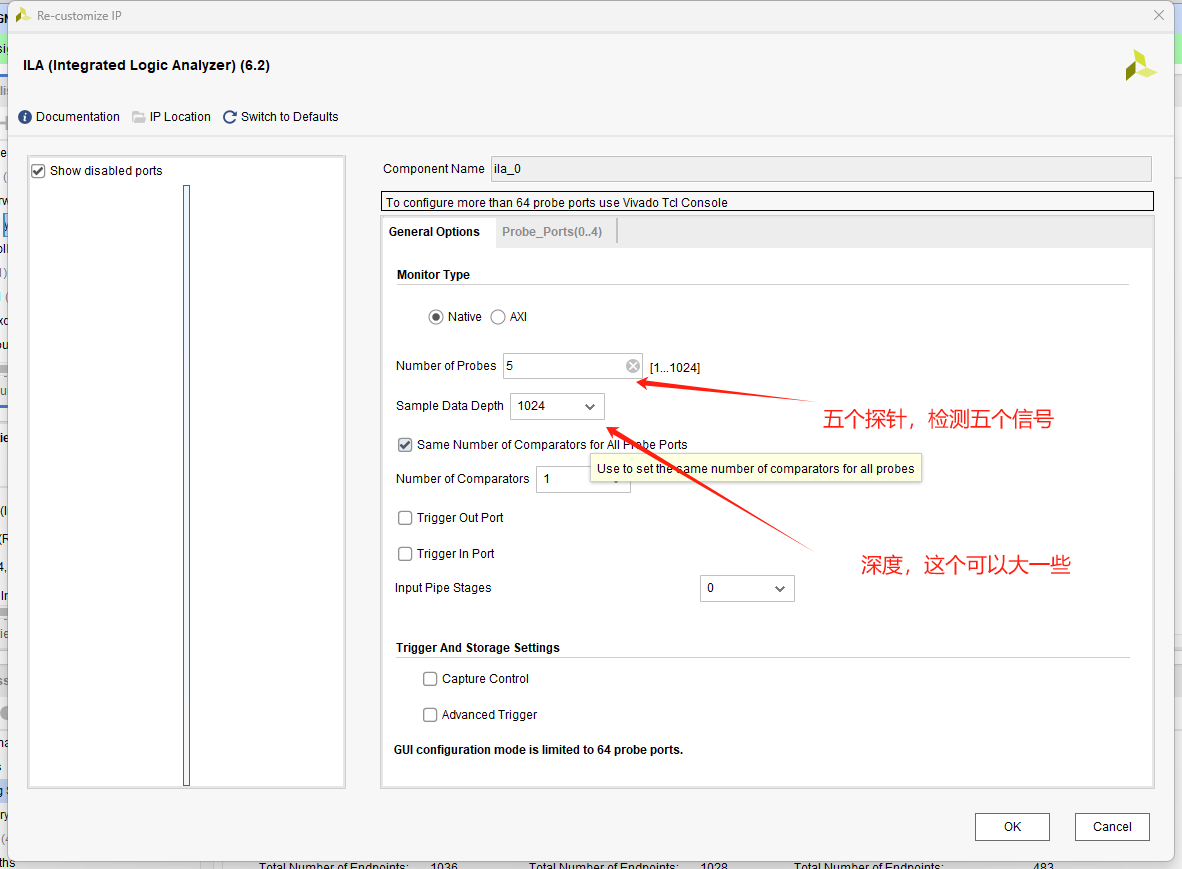

在实验中,我们也使用了ila的ip,就相当于探针一样观察信号的变化,本实验使用的如下(在IP catalog中搜索ila)

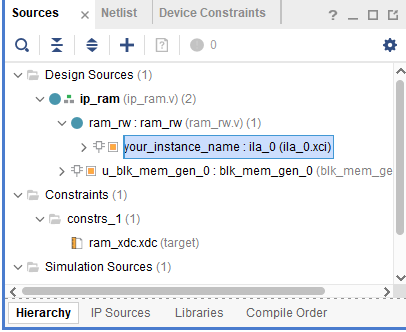

在控制模块(即ram_rw中例化ila即可)

仿真部分:

为时钟和复位(Y18和F15)配置引脚后,生成比特流下载到板子上,ila会自动跳出来,观察到ram读写数据正确(wea高为写,低为读)

注意:

由于所使用的板子的复位信号常高,因此这里需要取反

附:工程

ip_ram.v

`timescale 1ns / 1ps module ip_ram( input sys_clk, input sys_rst_n ); wire ram_en ; wire ram_wea ; wire [4 : 0]ram_addr ; wire [7 : 0]ram_wr_data ; wire [7 : 0]ram_rd_data ; ram_rw ram_rw( .clk (sys_clk), .rst (sys_rst_n), .ram_en (ram_en), .ram_wea (ram_wea), .ram_addr (ram_addr), .ram_wr_data (ram_wr_data), .ram_rd_data (ram_rd_data) ); blk_mem_gen_0 u_blk_mem_gen_0 ( .clka(sys_clk), // input wire clka .rsta(!sys_rst_n), // input wire rsta .ena(ram_en), // input wire ena .wea(ram_wea), // input wire [0 : 0] wea .addra(ram_addr), // input wire [4 : 0] addra .dina(ram_wr_data), // input wire [7 : 0] dina .douta(ram_rd_data), // output wire [7 : 0] douta .rsta_busy() // output wire rsta_busy ); endmodule

ram_rw.v

`timescale 1ns / 1ps module ram_rw( input clk, input rst, output ram_en, output ram_wea, output reg [4 : 0] ram_addr, output reg [7 : 0] ram_wr_data, input [7 : 0] ram_rd_data //从ram读取出来的数据 ); reg [5:0] cnt1; //读写转换 assign ram_wea = (cnt1 <= 31)?1:0; assign ram_en = rst; //读写转换计数 always @(posedge clk or negedge rst) begin if(!rst) cnt1 <= 0; else begin if(cnt1 == 6'd63) cnt1 <= 0; else cnt1 <= cnt1 + 1; end end //生成数据 always @(posedge clk or negedge rst) begin if(!rst) ram_addr<= 0; else if (ram_addr <= 6'd31) ram_addr <= ram_addr + 1; else ram_addr <= 0; end //生成地址 always @(posedge clk or negedge rst) begin if(!rst) ram_wr_data <= 0; else if (ram_wr_data <= 6'd31) ram_wr_data <= ram_wr_data + 1; else ram_wr_data <= 0; end ila_0 your_instance_name ( .clk(clk), // input wire clk .probe0(ram_en), // input wire [0:0] probe0 .probe1(ram_wea), // input wire [0:0] probe1 .probe2(ram_addr), // input wire [4:0] probe2 .probe3(ram_wr_data), // input wire [7:0] probe3 .probe4(ram_rd_data) // input wire [7:0] probe4 ); endmodule

在这份工程最底下就是例化的ila

视频来源:

28_实战篇:RAM IP核(第二讲:程序设计)_哔哩哔哩_bilibili