MultiBoot SPI

对于7系列FPGA来说,计算器件启动时间按照以下公式:

Config time = Bitstream size / (Config clk freq * Config interface width)

- Bitstream size为实际文件的大小,如果开启了compression,按照压缩后的尺寸计算

- Config clk freq是CCLK或者EMCCLK的频率

- Config Interface width取决于启动模式,比如SPIX4则位宽为4

接下来用启动时间去换算Watchdog timer数值:

Watchdog timer = Config time / Watchdog clk period

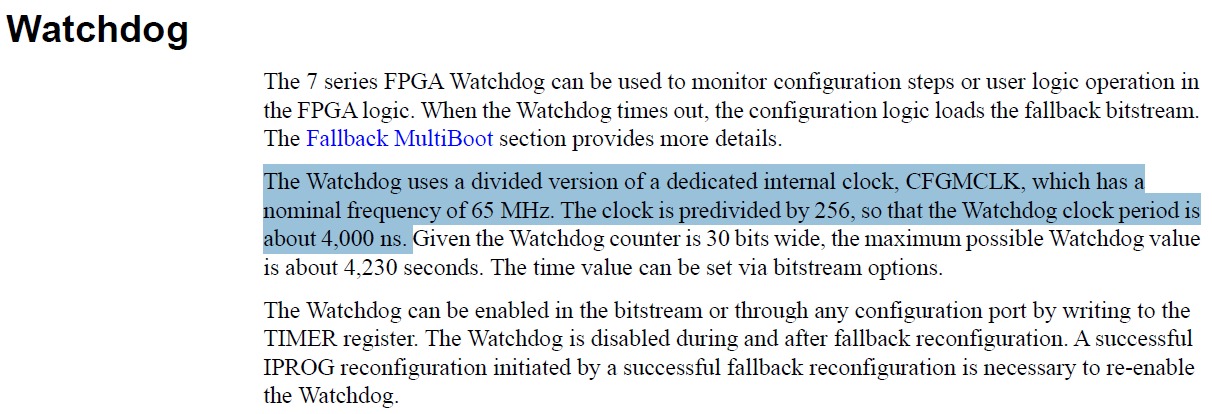

- Watchdog clk period对于7系列FPGA是4000ns,FPGA内部有个65MHz时钟,经过256分频系数得到大约为250KHz的时钟,这个时钟用于驱动watchdog timer。

需要以上两个步骤来计算watchdog timer的具体数值

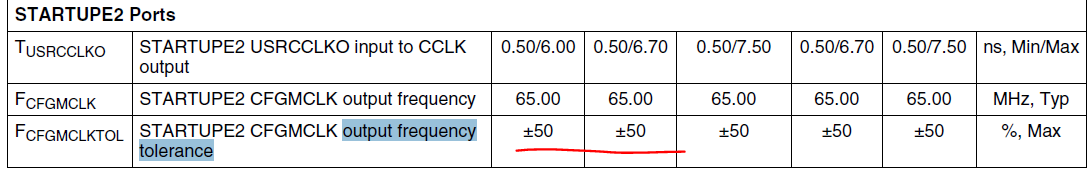

这里再解释一下为什么UG470 Table 5-37中说Watchdog timer的时钟大概是125KHz-380KHz。这是因为FPGA内部的时钟tolerance范围比较大,可以达到+-50%,经典值是65MHz,因此可以忍受的范围在37.5MHz-97.5MHz,经过256分频后,范围正好是125KHz-380KHz左右。

关于watchdog的描述,见ug470 P140。

Tolerance在DS182,因为这个时钟源是芯片内部的,时钟源频率不是很稳,所以频率范围比较大。

对于US/US+系列FPGA来说,计算方式和7系列也不一样,主要是watchdog的时钟设计变化,统一改为CCLK。

以7K325T为例,Master SPI X1方式加载。

配置bit文件92M bits,CCLK 100Mhz, Config time = 92M bits/(100Mhz *1) = 0.92s

watchdog period = 1/250Khz = 4000ns

则watchdog timer = config_time/watchdog period = 0.92s/4000ns = 23000 = 0x3_8270

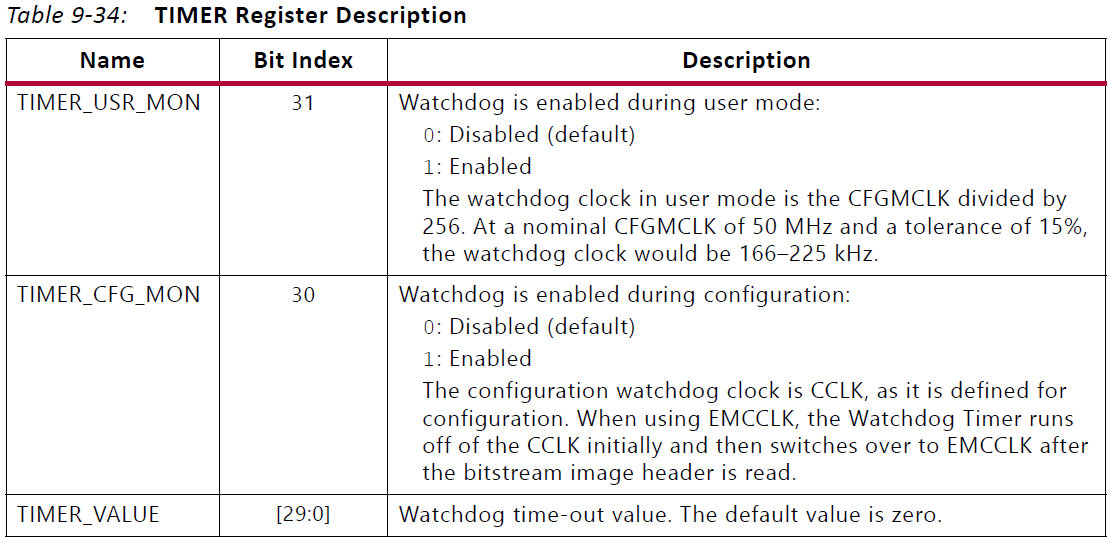

因此,Watchdog Timer Register (10001)的配置为0x4003_8270

以KU5P为例,Master SPI X1方式加载。

配置bit文件128M bits,CCLK 125Mhz, Config time = 128M bits/(125Mhz *1) = 1.024s

watchdog period = 1/125Mhz = 8ns

则watchdog timer = config_time/watchdog period = 1.024s/8ns = 128*10^6 = 0x7A1_2000

因此,Watchdog Timer Register (10001)的配置为0x47A1_2000

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通