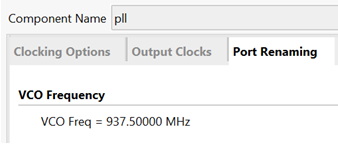

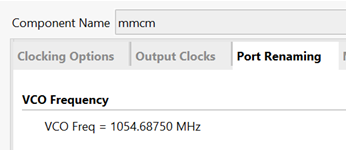

MMCM/PLL VCO

输入输出时钟频率,input 322.265625Mhz, output 312.5Mhz

对于使用MMCM与PLL的不同情况,虽然输入输出频率是一样的,但是,分/倍频系数是不同的,不能使用同一套参数(M/D/O)。

原因:VCO不一致。这个应该是vivado工具计算出来的输出时钟jitter最小的VCO。

根据这个VCO,由ug472中的公式,可以算出,M/D也是不一样的。

碰到的故障:

因为设计原因,MMCM不够用,因此部分模块使用了PLL。

时钟单元的代码,是纯verilog HDL代码,没有使用GUI,CBB模块调用了底层MMCM/PLL原语,使用宏控制。

考虑到输入输出频率一致,使用了同一套M/D/O参数。

测试时发现,使用PLL的channel,功能不对,FIFO有溢出。仔细定位后发现,PLL输出的频率与预期的不完全一致。

通过GUI重新生成PLL IPcore,发现verilog手动例化的PLL与IPcore的PLL代码,M/D/O不一致。

更新使用GUI生成代码中的M/D/O值,问题解决。

Takeaway:

如果确实需要手动例化MMCM/PLL代码,建议先在GUI中根据配置产生IP,然后将底层代码copy到所用的模块。切记不要想当然认为MMCM/PLL功能差不多,相同的输入输出频率,分/倍频系数也是相同的。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通