Accurate SerDes LineRate

测试现象:(单板A板载7A series,单板B板载7K series)

1. 单板A板载2个type C接口,通过线缆自环,GTP near-end loopback, OK.

2. 2块单板A,使用线缆通过type C接口互联,GTP far-end loopback, OK.

3. 单板B板载2个type C接口,通过线缆自环,GTX near-end loopback, OK.

4. 2块单板B,使用线缆通过type C接口互联,GTX far-end loopback, OK.

5. 单板A和单板B,使用线缆通过type C接口互联,SerDes far-end loopback, NO link,无法正常通信测试.

现象分析:

1. 通过现象5,怀疑是插损过大导致信号无法识别。但是现象2/4又排除了插损的猜测。

2. 相同的单板能互通,不同的单板则无法互通,怀疑板间差异导致的。而理论上,7A series与7K series确定可以SerDes互通,与竞争对手的SerDes都能互通,所以不存在不同系列的SerDes互通上的疑问。

3. 重点排查SerDes与type C的PN线序是否颠倒,时钟是否正常等等硬件参数连接是否正常。

ROOT CAUSE:

单板A GTP的refclk与单板B GTX的refclk有差异,不是预期的相同时钟,从而导致了实际SerDes LineRate不一致,无法正常通信。

预期refclk为125Mhz,时钟源由时钟芯片输出,该时钟芯片由板上ARM芯片配置(RK3566)。实际发现单板A的refclk与预期的频偏相差较大,最大相差5M,即恶劣时,refclk=120M。具体原因时ARM配置的问题,ARM操作系统的负载差异,会导致配置程序的结果与预期不符,细节未知。

(频偏:是指实际时钟频率相差较大,target frequence = 125M, 实际输出120M 或者 130M;

抖动: jitter,是指实际时钟频率以中心频点来回抖动,正态分布)

改进措施:

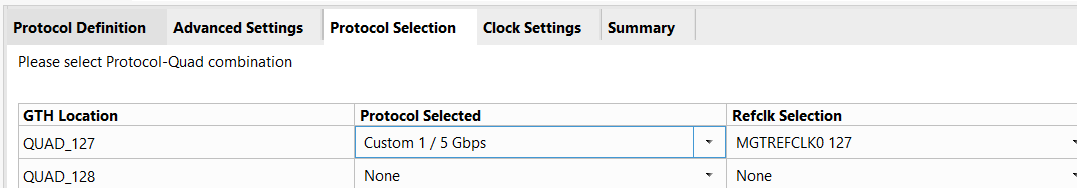

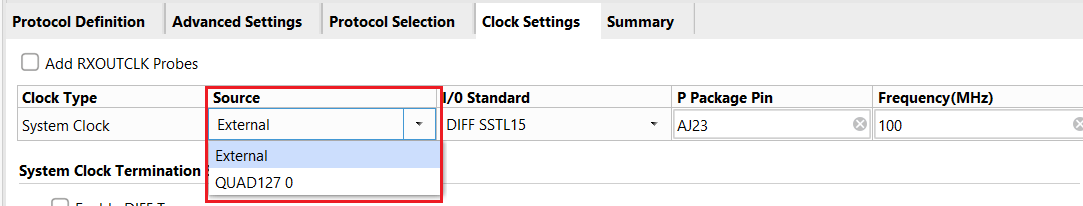

如下截图,IBERT设置时,System Clock不建议选择与SerDes REFCLK相同的时钟源。

原因:

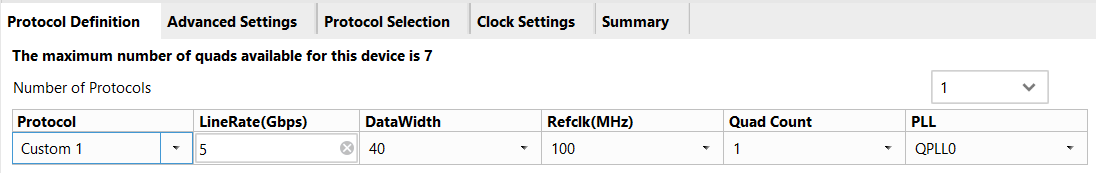

1. 假设target refclk = 125Mhz, LineRate = 5Gbps。如果实际输入的refclk频偏大,130Mhz,实际的LineRate就超过5Gpbs。

2. 如果System Clock选择与SerDes REFCLK相同的时钟源,则相当于自己测试自己。IBERT GUI界面虽然仍然显示5Gpbs速率,但是实际不准确,调试时无法及时发现。

3. 如果System Clock选择独立的External时钟源,则使用另外一个晶振时钟来监测SerDes功能。IBERT GUI界面显示数据为独立晶振时钟的检测结果,若因为SerDes时钟不准确导致的问题,方便及时发现问题。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通