MMCM and PLL Dynamic Reconfiguration

Reconfiguration is performed through the DRP.

The DRP provides access to the configuration bits that would normally only be initialized in the bitstream. This allows the user to dynamically change the MMCM or PLL clock outputs without loading a new bitstream.

The MMCM or PLL must be held in reset during dynamic reconfiguration or must be reset after the dynamic reconfiguration changes have completed. Frequency, phase, and duty cycle can all be changed through the DRP port.

The MMCM has six user-accessible configuration bit groups that allow reconfiguration of individual clock outputs. The six groups are the divider group, the phase group, the fractional group, the lock group, the filter group, and the power group. These configuration bit groups are internal to the MMCM primitive and clarify the operation of the MMCM_DRP reference design module.

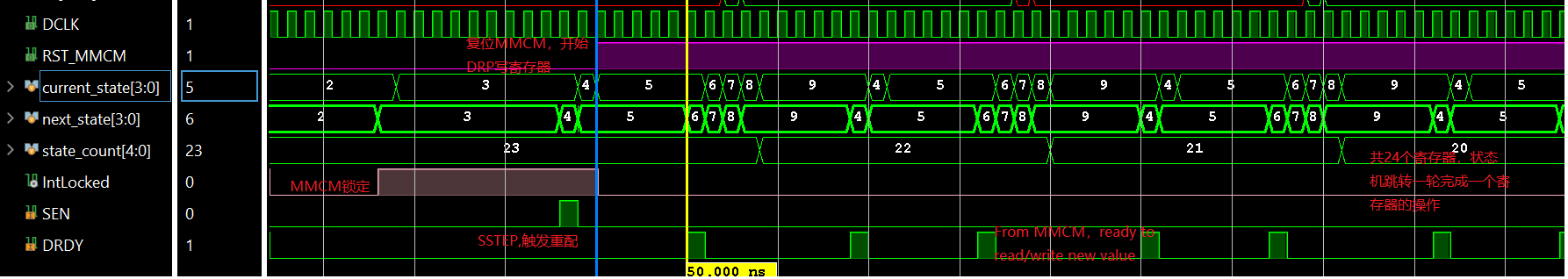

Below is the reconfiguration timing from simulation.

Please refer xapp888 and ug472 for more detailed informations.

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通