SystemC中文教程一

SystemC是什么

首先, SystemC不是一门新的语言,而是基于C++开发的library;因此,你所熟悉的C++知识都可以在SystemC建模时使用;理论上来说,SystemC library和常见的boost库没有任何本质差别。此外,这也告诉我们只需一个支持C++的环境,我们就可以进行SystemC建模和仿真,无需任何其他工具,这相比其他软硬件建模语言来说,所需环境极其简单。

注:最常见的硬件描述语言Verilog,它的仿真需要仿真工具支持,如VCS、modelsim等,它们都是价格昂贵的EDA工具,且使用复杂。

其次,SystemC是由Accellera组织拥有的开源库,它使用Apache 2.0开源协议;Apache2.0协议是一种对商业应用友好的许可,所以,不论用户用之开发的产品是否商用,都可以放心使用,不用担心侵权行为。

但是,SystemC是干什么用的呢?SystemC的命名已经表明了它的用途,它是一种系统建模语言;我们常常用系统来形容复杂的东西,一台电脑、一块芯片、一个公司都可以称之为一个系统。系统有很多特征,如模块化、并行性、通信机制、规则下办事等等。以电脑为例,CPU、GPU、内存、显示器等都是一个个独立的模块,各自完成各自的任务;它们总是并行工作,同时又通过接口相互通信。如何为一个系统建模呢?原生的编程语言都是串行执行的,无法建模并行系统;即使你建模了一个系统,但最终都要在CPU上跑仿真,而CPU总是串行执行的。我们知道,硬件是大量并行运行单元的组合,必须能够支持对并行操作的模拟;SystemC正是为此而生,为软硬件系统建模提供了强有力的支持。

总结:SystemC是一个支持系统建模的开源的C++ library;

SystmeC的作用

现代的芯片总是包含硬件和软件,软件部分可以是固件或者驱动;芯片市场是一个充满竞争的市场,几乎所有的芯片公司对产品都有严格时间规划;如何让产品尽快面市,如何减少产品bug几乎是所有芯片公司都需要面对的难题。SystemC可以让软硬件并行开发,加快产品面市时间。

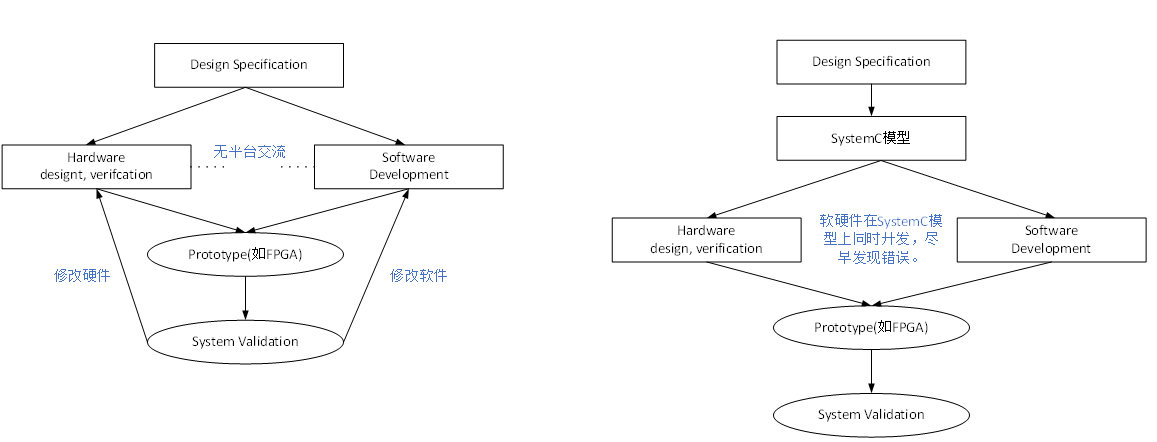

如下左图所示,传统的设计流程中在FPGA原型出来之前,硬件和软件开发之间几乎没有交流;只有在经过漫长的“设计-验证-综合”流程后(一般几个月),软件才能在FPGA平台上测试自己的代码,由于软件设计时没有平台测试,此时测试必然有很多错误,这种错误需要修改硬件或软件,并重新迭代,这将浪费大量的时间。在计算机领域,有一个至理名言:越早发现bug,损失就越小。显然,传统的设计流程与此目标不符。

如下右图所示,在软硬件设计之前,先开发抽象SystemC模型(如TLM模型),然后硬件部门将此模型转化为RTL,软件部门在此模型上开发软件。如此一来,软硬件的任何错误都能尽早被发现并修改,大大节省了开发时间。

常见疑问1:开发SystemC模型不也增加了设计流程时间吗?

答:是的,开发SystemC模型确实需要时间;不过由于C++是高级语言,而且这里的模型不需要精确到clock级别,只需要达到TLM级别,所以开发难度相比与硬件设计验证和软件开发来说非常低,所耗时也是可以忽略的。

常见问题2:为什么不在RTL上开发软件呢?

答:首先,等到一个能运行的RTL出来需要很长的时间;其次,RTL的仿真速度比TLM模型速度慢至少100x倍;所以RTL平台开发软件是不现实的。

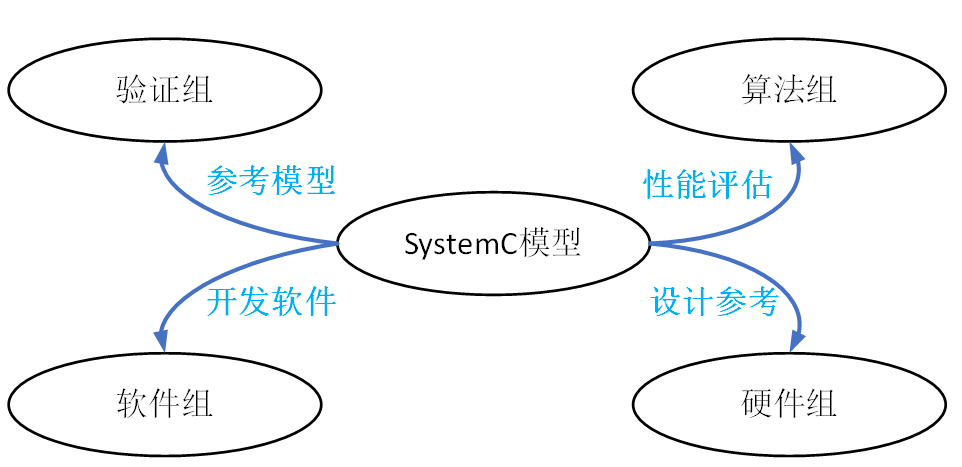

其实SystemC的用途远不止如此,下面大致总结下SystemC的用途:

- 硬件架构探索,建立算法、性能模型;

- 验证工程师作为参考模型(通过DPI接口调用);

- 设计工程师将其作为design spec,设计RTL;

- 软件工程师作为软件开发的硬件模型;

- 使多种提前测试成为可能;

总结:SystemC模型在芯片前端流程中重用度非常高,几乎可以作为各个部门(架构组,算法组,设计组,验证组,软件组)之间的桥梁,使得部门之间的沟通合作更加有效,大大增加工作效率。

几种使用SystemC模型的灵活测试案例:

- 验证人员可以提前搭建测试平台(使用SystemC model做DUT);

在RTL可用之前,将SystemC model封装于System Verilog内,然后作为DUT搭建测试平台,并编写test cases。现在,如VCS等仿真软件已经内置了对SystemC的支持,无需使用DPI接口,就能将SystemC模型封装成System Verilog module。

- 混合仿真

按照上述方法搭建测试平台后,随着一个个模块或IP的RTL设计完成,逐渐用它们替换测试平台中相应的SystemC模型,然后运行测试用例,即可测试真实的RTL。

- 在FPGA平台上使用

虽然SystemC模型仿真速度要比RTL仿真快100x-1000x,但是依然没有FPGA速度快;因此在FPGA平台稳定之后,在FPGA平台上继续开发软件会更加高效。不过FPGA平台昂贵,面积有限,想将整个SOC放进FPGA是不可能的,但是驱动开发往往需要整个SOC的平台,这时可以将SOC的SystemC模型中自己关注的IP模型替换成FPGA实现,其他部分依然使用SystemC模型。

SystemC的优势

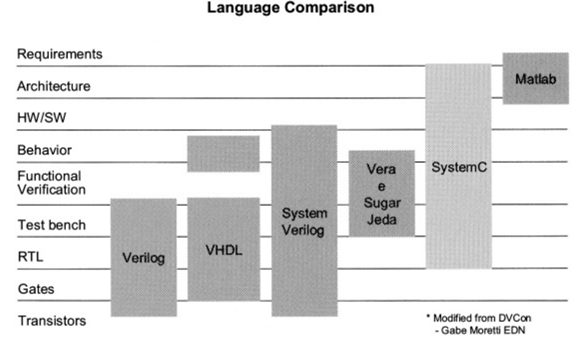

芯片设计前端的流程很长,和芯片前端相关的语言也很多,比如Verilog、VHDL、System Verilog、SystemC、Matlab、C/C++等等,但没有一个语言能够做到适合于整个前端流程,包括本文所说的SystemC也不行;每种语言都有适合使用的领域,只有在整个前端流程的不同节点上选择最合适的语言工具,并加以整合,才能加速产品开发。

注:本图引用自《SystemC: From the Groud Up》

如上图所示,它显示了各种语言工具适合使用的场所,其中:

- Verilog、VHDL主要用于RTL建模,并用来综合生成数字电路;

- System Verilog吸收了Verilog,既能够用于RTL建模,也能用于功能验证,基于System Verilog开发的UVM更是现如今最流行的验证方法学。

- Verie和e语言主要用于对ASIC进行功能验证;

- SystemC则主要用于架构级建模、软硬件建模、行为级建模;

- Matlab则主要用于算法设计、架构设计等。

我们熟知的Verilog/VHDL/System Verilog是最常见的硬件建模语言(更准确的说是硬件描述语言,即HDL),但是众所周知,HDL的开发难度大、故障率高、运行速度慢、与软件语言兼容性差,HDL用于开发RTL非常合适,但是用于抽象程度更高的建模就显得难堪大任。

C++属于高级语言,开发速度快、运行效率高(仅次于C)。考虑到几乎所有的底层软件都是用C/C++开发的,使用C++进行硬件建模,使得软硬件可以在同一种语言开发,从而让软硬件协同仿真更加方便高效。

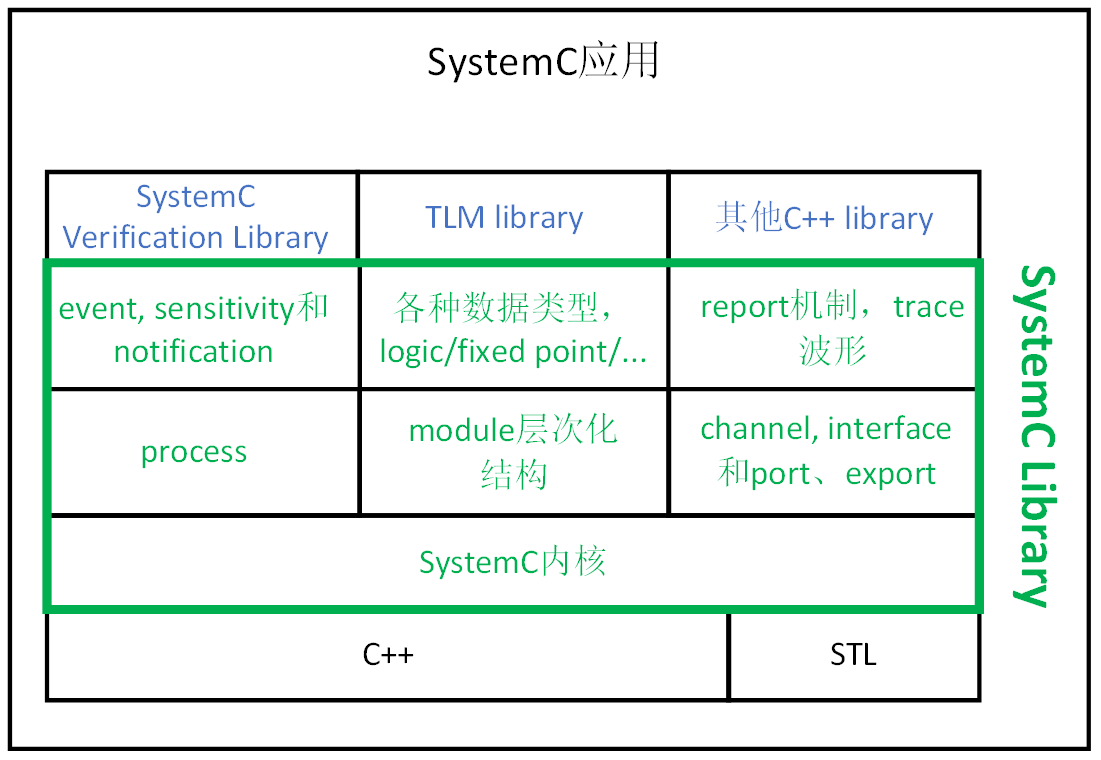

SystemC library

下图是SystemC的框架图; SystemC的底层是C++及其标准库,当然也可包括其他的C++库,如boost库。

SystemC library包含多种功能,最核心的有如下几项:

- SystemC内核

SystemC内核用于调度SystemC process,其功能和Verilog和VHDL仿真内核非常相似;如果你不了解Verilog仿真内核,也可以认为它和Linux内核相似,只不过比Linux内核简单地多。

- SystemC process

SystemC process是由用户定义的,用来模拟硬件和软件的行为。Process是并行运行的,由SystemC内核调度执行。

- SystemC event

和Verilog仿真内核一样,SystemC内核是事件驱动型内核,所以理解event非常重要;SystemC event是指在特定时间点发生的事件。

- SystemC module

SystemC module用于将建模对象模块化、层次化;

- SystemC channel/interface/port/export

SystemC channel/interface/port/export用于实现模块间的通信;

SystemC中文教程安排

我们将分成6个部分来讨论SystemC,每个部分又包含2-6个课程。

第一部分 SystemC简介

第二部分 SystemC Object和Module

第三部分 SystemC process

第四部分 SystemC通信

第五部分 SystemC其他

第六部分 TLM2.0简介

浙公网安备 33010602011771号

浙公网安备 33010602011771号