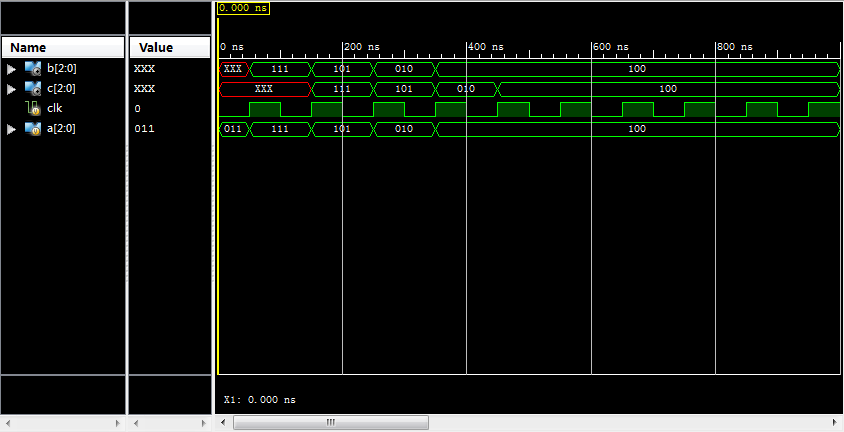

输入信号与时钟变化一致时,非阻塞方式内部信号变化分析

程序:

module non_block( input clk, input [2:0] a, output[2:0] b, output[2:0] c ); reg[2:0] b,c; always@(posedge clk) begin b <= a; c <= b; end endmodule

激励:

module tb_block; // Inputs reg clk; reg [2:0] a; // Outputs wire [2:0] b; wire [2:0] c; // Instantiate the Unit Under Test (UUT) block uut ( .clk(clk), .a(a), .b(b), .c(c) ); initial begin clk = 0; forever #50 clk = ~clk; end initial begin a = 4'h3; // $display("____________________________"); # 50 a = 3'h7; // $display("____________________________"); # 100 a = 3'h5; // $display("____________________________"); # 100 a = 3'h2; // $display("____________________________"); # 100 a = 3'h4; // $display("____________________________"); // # 100 $display("____________________________"); //$stop; end endmodule

仿真结果: