2018-2019-1 20165321 《信息安全系统设计基础》第五周学习总结

2018-10-28 17:19 Ze6Pui3Loeng4 阅读(285) 评论(0) 收藏 举报教材学习内容总结

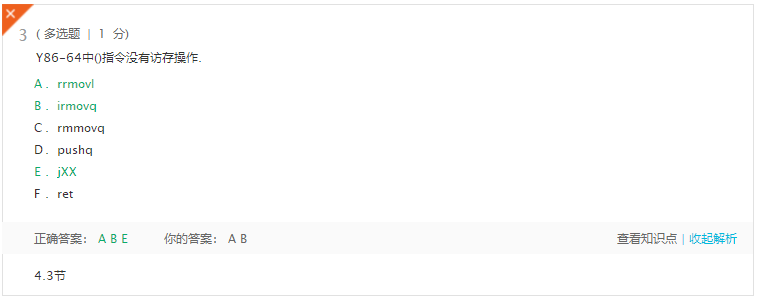

- 随机访问存储器

-- SRAM 将每个位存储在一个双稳态的存储器单元里,只要有电,它就会永远地保持它的值。

-- DRAM 将每个位存储为对一个电容的充电,内存系统必须周期性地通过读出,然后重写来刷新内存每一位。

-- SRAM 和 DRAM 存储器的特性。

![]()

- 传统的 DRAM,DRAM 中的单元(位),被分成 d 个超单元,超单元被组织成一个 r 行 c 列的长方形阵列。信息通过称为引脚的外部连接器流入/流出芯片,每个引脚携带一个1位信号。每个DRAM信号被连接到称为存储控制器的电路,电路每次传输量为8位。行地址i,RAS请求;列地址j,CAS请求。

- 增强的DRAM

-- 快页模式,允许对同一行连续地访问可以直接从行缓冲区得到服务。

-- 扩展数据输出,各个 CAS 信号在时间上靠得更紧密一些。

-- 同步,与内存控制器通信使用一组显式的控制信号。

-- 双倍数据速率同步,使用两个时钟沿作为控制信号。

-- 视频 RAM ,用在图形系统的帧缓冲区中。输出是通过依次对内部缓冲区的整个内容进行移位得到的,并允许对内存并行的读和写。 - 非易失性存储器,断电后仍保存着信息的存储器。

-- PROM, 只能被编程一次。

-- EPROM, 紫外线清零,重写次数达到1000次。

-- EEPROM, 特定电压可擦除,被编程次数达到 100000 次。

-- 闪存,包含固态硬盘。 - 访问主存

-- 读事务,从主存传送数据到CPU。

-- 写事务,从CPU传送数据到主存。

-- 总线,一组并行的导线,能携带地址、数据和控制信号。

-- 系统总线,连接总线接口和I/O桥。

-- 存储器总线,连接I/O桥和主存。 - 总线按内容分为地址总线、数据总线、控制总线。

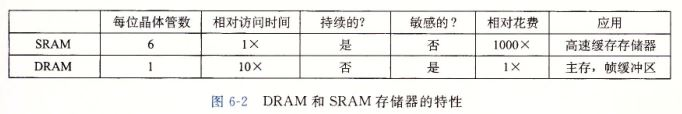

- 磁盘

-- 磁盘>盘片>磁道>扇区,每个扇区包含相等数量的数据位。

![]()

- 磁盘以扇区大小的块来读写数据。

- 连接 I/O 设备,PCI总线(Intel)。

- 固态硬盘

-- 固态硬盘结构:闪存翻译层与磁盘控制器作用相同,一个闪存由 B 个块序列组成,每个块由P页组成。

-- 数据是以页为单位读写的。只有在一页所属的整个块被擦除后(有效内容拷贝到其他块)才可写这一页。通常页的大小是 512~4KB ,块由 32~128 页组成。 - 局部性,倾向于引用邻近与其他最近引用过的数据项的数据项,或者引用最近引用过的数据项本身(步长尽量小)。

- 存储器的层次结构,对于每个 k,位于 k 层的更快更小的存储设备作为位于 k+1 层更大更慢的存储设备的缓存。层次结构中每一层都缓存来自较低一层的数据对象。

- 存储器的层次机构示意图:

![]()

- 缓存命中,找 k+1 层的数据,在第 k 层的缓存内容中找到了,可以直接读取第 k 层数据,称为缓存命中。

- 缓存不命中,第 k 层没有要找的数据,第 k 层的缓存要从第 k+1 层中缓存中取出包含对象的块,若第 k 层满,则需要覆盖一个现有的块。冷不命中,第 k 层没东西,所以不命中。

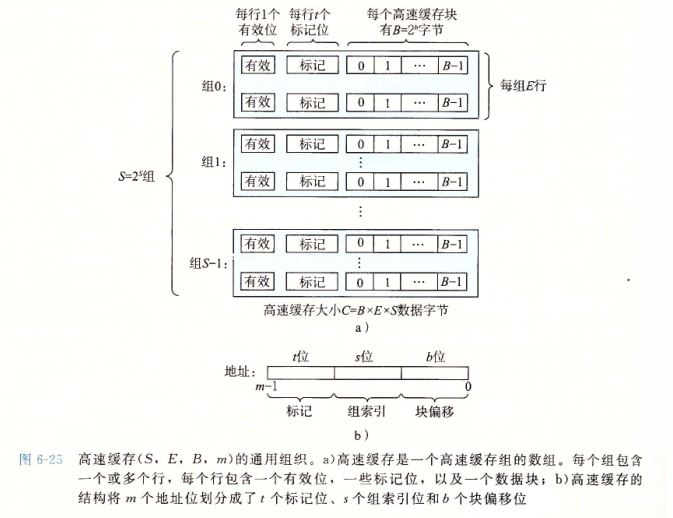

- 高速缓存存储器,主要是大小(P426)和概率(P431)

![]()

上周测试错题总结

浙公网安备 33010602011771号

浙公网安备 33010602011771号