【P0】Logisim部件级实验/有限状态机

课上

过得十分狼狈。经鉴定孩子可能脑子拗

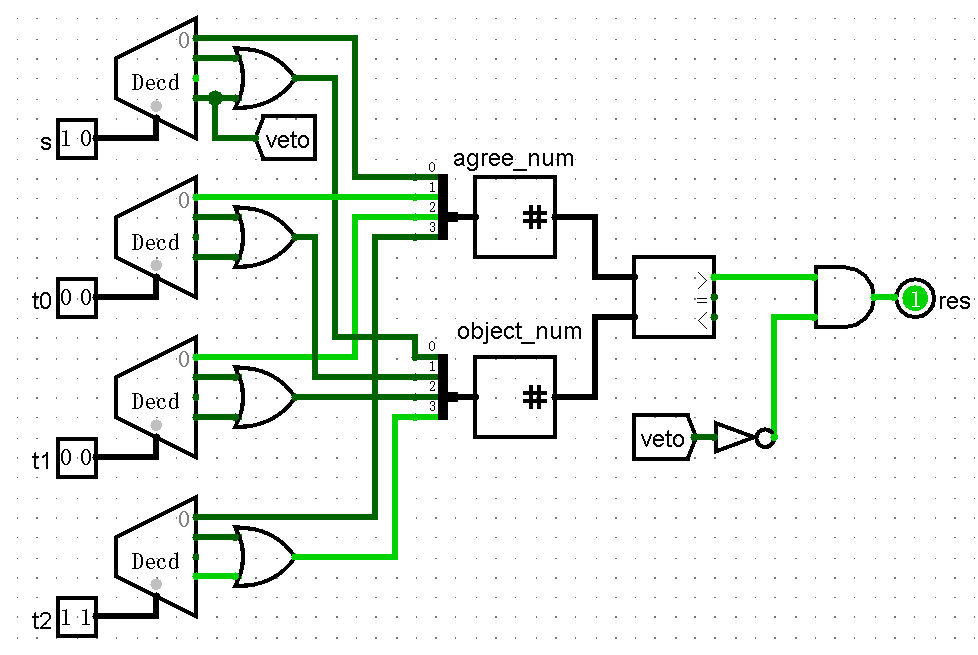

T1 投票决议

组内投票,赞成>反对,则通过;组长拥有一票否决权。

| 信号名 | 方向 | 描述 |

|---|---|---|

| [1:0] s | Input | 2'b00 赞成 2'b01 反对 2'b10 弃权 2'b11 一票否决 |

| [1:0] t0 [1:0] t1 [1:0] t2 |

Input | 2'b00 赞成 2'b01 2'b11 反对 2'b10 弃权 |

| res | Output | 1 通过;0不通过 |

三种状态,天然没法被2进制表示存储计算。考察多状态表示处理。

- 单独处理一票否决:在最后通过

&解决 - 统一处理三种状态:通过子模块逻辑区分出3种状态,分别统计构造“赞成数”、“反对数”(位合成);“赞成数”大于“反对数”则出1

然而其实根本无需特设子模块!目标就是状态码,那么独热码首当其冲:Decoder为2'bxx分配独热码,0001赞成,0010和1000反对,所以Decoder输出:第0位1对应“赞成”,第1、3位1对应“反对”

当时就对三状态的统一区分无头绪,慌张中想着通过三态Demultiplexer(DMX)分配0、1、 x(高阻态)实现。然而高阻态显然不是什么稳定的第三状态,多数元器件断然是不支持的。

人家5minAC,咱搭了近1h,心态整得做过山车一样,可能是真蠢。

然事后回看,可能是对“多状态的状态码分配”这普遍的方法论没有概念。Decoder没厘清应用本质,长久没用属于灯下黑了。

T2 字符自动机:2021或2011

- 注意状态机跳转设置

- “0 + 独热码”最适合Combinational Analysis自动生成;注意公式别打错(多打、漏打、顺序反)

基础mealy机,没什么好说的

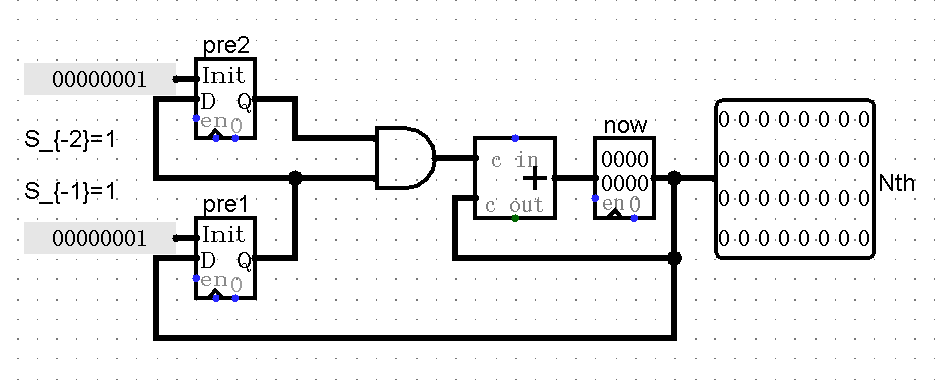

T3 三元递推式求指定项

| 信号名 | 方向 | 描述 |

|---|---|---|

| [4:0] N | Input | 求第N项的值\(S_{N}\) |

| [31:0] Nth | Output | \(S_{N}\)的值 |

时序电路,在64个周期内完成计算

\(

\begin{equation}

S_n=\left\{

\begin{aligned}

& 0 &,& n=0 \\

& 1 &,& n=1,2,3 \\

& S_{n-1} + S_{n-2} \wedge S_{n-3} &,& n \ge 4

\end{aligned}

\right.

\end{equation}

\)

吐槽:

\(\wedge\) 是“合取”而不是“异或”,要不然就全是1了,而且S0,S1,S2便不能按通项推出S3

\(+\) 是“相加”而不是“或”。符号系统混杂火死。

和Fibs那道题一模一样

//递推转移

now += pre1 & pre2;

pre1 = now;

pre2 = pre1;

其中  为自己建的可初始化寄存器

为自己建的可初始化寄存器

Logisim处的缺陷

1.很多元件直接unsigned处理了,感觉用到signed话很可能会混乱