mach_msg收到的exception message中的subcode表示什么?

2021-02-08 17:40 l4y 阅读(349) 评论(0) 编辑 收藏 举报问题来源于 KSCrash 中两个针对 mach exception message 中 code、subcode 类型、取值的 PR。

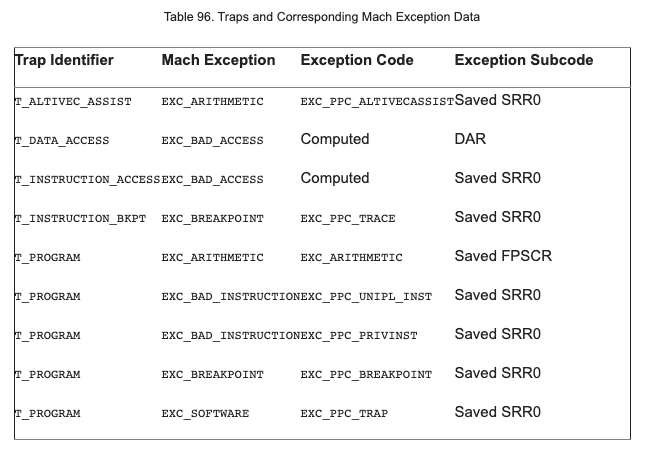

在 Mac OS X Internals: A Systems Approach 一书的 Section 9.7. Mach Exceptions 中,有对 code、subcode 取值的解释。

参考 https://flylib.com/books/en/3.126.1.109/1/

SRR0 是什么?

SRR0 全称是 Machine Status Save/Restore Register 0,即机器状态保存/恢复寄存器0。

SRR0 在 64 位实现中是 64 位寄存器,在 32 位实现中是 32 位寄存器。对于 32 位实现,SRR0 取低 32 位。 SRR0 寄存器用于在异常情况下保存机器状态,并在执行 rfid (或 rfi)指令时恢复机器状态。

当异常发生时,SRR0 被设置为指向一条指令,这条指令恰好满足之前的所有指令都已完成执行,没有后续指令开始执行。当 rfid(或rfi)指令被执行时,SRR0 的内容被复制到下一条指令地址(NIA),即下一条要执行的指令的 32 位 或 64 位地址。

根据异常类型的不同,SRR0 所寻址的指令可能没有完成执行。SRR0 对引起异常的指令或紧接着的指令进行寻址。寻址的指令可以通过异常类型和状态位来确定。

rfid、rfi 指中断返回指令。

DAR 是什么?

DAR 全称是 Data Address Register,即数据地址寄存器。

在 DSI 或 对齐异常(alignment exception)后,DAR 被设置为故障指令(faulting instruction)生成的有效地址。

更具体的解释,如果内存访问导致异常(如对齐异常),则内存访问指令生成的有效地址会被放在 DAR 中。如果异常发生在以32位模式运行的64位实现中,DAR的高 32 位被清除。

DSI 异常发生在因为某些原因不能执行数据存储器访问时。这种访问可以由 load/store 指令、某些内存控制指令、某些缓存控制指令产生。

SRR0、DAR 参考 http://www.csit-sun.pub.ro/~cpop/Documentatie_SMP/Motorola_PowerPC/PowerPc/GenInfo/pemch2.pdf

DSI 参考 http://www.csit-sun.pub.ro/~cpop/Documentatie_SMP/Motorola_PowerPC/PowerPc/GenInfo/pemch6.pdf

本文来自博客园,作者:l4y,转载请注明原文链接:https://www.cnblogs.com/xjshi/p/14389767.html