FPGA HLS Today Successes, Challenges, and Opportunities

Deep Learning

FINN

深度神经网络(DNNs)的底层算法结构简单,但是计算量、对数据的访问和模型参数的存储对内存的需求很大。一种可行的方法是将输入、激活和模型参数量化,来降低数值精度,通过设计方案使得增加的吞吐量和降低的能耗来补偿精度上的降低。

FINN项目集中在,利用FPGA的可重构性,将低精度的DNN映射到FPGA上。这种直接映射是通过三个组成部分完成的:

-

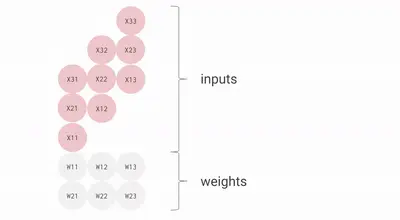

Sliding Window Units(SWUs):滑动窗口单元

将前一层的输出数据按照通道优先的方式,存储在缓冲区RAM的地址上,然后生成每个像素对应的地址,根据该地址从RAM上读取像素,生成图像矩阵,就可以将卷积运算转换为矩阵乘法。

(感觉是在滑动窗口内的矩阵转置?横着的数据变成竖着的。因为滑动窗口有重叠,为了不重复计算,所以增加了一个缓冲区用作地址的映射)

-

Processing Elements(PEs):处理单元

根据索引取出权值和输入的向量相乘和累加,取出阈值进行比较,生成输出向量

-

Matrix-Vector-Threshold Units(MVUs):

权值保存在PE的片上存储器上,每个PE都具有SIMD通道元素的输入。计算时,每个PE接收的输入向量相同,但是PE需要输入向量与不同的权值进行相乘累加,就可以同时计算得到多个输出。

(对权值矩阵还有参数划分的设计)

一个layer的可能组成:

DNN的所有层同时被实现为数据流风格,权值都存储在片上,不同的层可以实现不同的精度,也可以调整层的延迟或者吞吐量。

FINN的输入是PyTorch创建的量化神经网络描述,导出为ONNX,根据ONNX描述创建网络的数据流图模型。然后对图进行优化和转换,使得可以用核函数更好实现。

由于FINN的核函数具有对面积(量化操作)/吞吐量(流水线,并行计算)进行平衡的能力,使得FINN具有在一个数据流模型中同时优化多个进程的能力。

对于大型网络,FINN趋向于实现高吞吐量的量化网络。对于可以完全展开小网络,FPGA可以实现快速推理和纳秒级的延迟。

数据流架构

数据流架构的加速器中,网络每一层均对应专用的处理引擎,通过片上缓冲区进行连接,可针对每一层的处理引擎进行特定的优化。通过定制计算阵列参数,可以在面积和速度上优化每个卷积层的处理引擎。同时只有部分特征图保存在片上,既降低了片上内存需求也避免了频繁访问片外存储器。

由于此架构计算引擎实现了流水线化,因此可以最大化吞吐量,一旦前一层的计算引擎产生输出,后一层的计算引擎即可立即开始工作。因此与其它两种体系结构(部分重构架构,单个处理引擎架构 )相比,数据流体系结构是最为有效的加速体系结构。

FracBNN

之前的discussions主要集中高效实现现有的ML模型\网络在FPGA上。但是FPGA具有独特的优势,例如高效支持bit-level操作和可定制内存层次结构(customizable memory hierarchies)。除去之前讨论的量化技术,这些优势允许我们设计一个FPGA-specific的ML模型,作者提出了一个针对FPGA结构的,基于算法-硬件协同设计的ML模型。

BNNs(Binary neural networks)的权重和激活都是1-bit的,常见的操作比如说卷积可以简化为位运算。这种位运算在使用基于LUT逻辑的FPGA上能有效实现,也减少了内存要求。

现有的缺点:

- 现有的基于FPGA的BNN实现由于减少了数值精度,所以准确率较低。

- BNN模型通常在输入层使用浮点的权重和激活,使得资源的利用率降低,因为浮点资源不能重复被其他层利用。

解决的方式:

-

通过分数激活(fractional activation)去提高BNNs的精度。

FracBNN通过双精度激活方案,如果某个特殊的卷积层以一个重要的方式影响了最终的精度,就使用一个额外的binary卷积(2-bit conv)来计算

-

使用thermometer encoding二值化输入层保持高精度。为了在对输入层二值化的过程中减少精度的损失,FracBNN增加了输入层的通道数,通过对每个8-bit像素处理成8-dim二值向量。

实验结果:

在ImageNet上的top-1准确率提高了28.9%和减少了2.5倍的模型大小。

FracBNN加速结构

1-bit的weights存储在off-chip DDR内存,2-bit的feature map存储在on-chip上RAM上,减少访问延迟。

在获取feature map之后,FracBNN首先将2-bit的feature切割位MSB和LSB,然后沿着通道维度包装到B-bit的任意精确整数,这是因为存储在DDR上的W是B-bit的。然后将收集到的W和特征图送入Conv Engine。同时,获取BN中的阈值和权重等辅助参数;也从DDR中加载了激活函数和数据进行shortcut的残差连接。

单个处理引擎架构

不同网络层共享卷积运算引擎,卷积运算引擎通常是由大量的处理单元(PE)阵列构成,计算核心被不同层复用,因此需要逐层顺序计算各卷积神经网络层。不同层的特征图和权重存储在片外DRAM中

这种架构摆脱了FPGA中逻辑资源的限制,能够适应各种具有不同尺寸、不同输入输出通道数的网络层,以及更复杂的CNN。然而,由于大量特征图在片上和片外

存储器之间频繁传输,且权重也需要频繁地被重新加载,因此要占用大量的总线带宽,而且串行逐层计算的方式,将会导致性能大幅降低。

上海工程技术大学硕士学位论文 :基于FPGA的深度学习加速器设计与研究

HLS-Based DNN Compilers

脉冲阵列内的数据流:

先将权重矩阵的每个值取出存放在运算单元,作为一个乘数;再将例如3*3的输入矩阵特殊排列,“流动”地广播到各个运算单元,作为另一个乘数。矩阵流动完成后,就可以得到输出矩阵

Challenges

- 综合设计的验证方法:C/RTL联合仿真来验证HLS输出的功能,联合模拟计算密集型的DNN模型也是一个相当耗时的过程

- HLS工具对于结果质量(QoR)的报告不准确,LUT/FF计数的过高估计可能会误导设计人员选择一个并行化因子较低的次优架构

Video Transcoding

需要在不探索所有编码空间的情况下,设计算法平衡视频吞吐量、编码比特率、资源使用和视频质量。

介绍了一种由NGCodec构建的高质量编码器HEVC

Design Constraints

HEVC的基本结构是一个64×64像素的粗粒度块,称作编码树单元(Coding Tree Unit,CTU),CTU可以按照不同的粒度分解。

NGCodec通常处理4 × 4块像素作为一个单元,大多数组件的时钟速率为200 MHz,每个块25个周期,尽管一些组件被设计为运行在300或400 MHz,以减少资源需求。这个速率足以支持1080P60分辨率(1920 × 1080 × 60),

块处理方式的编码实现方式有两种:

简单编码风格,将II设置为25,适用于资源共享机会较少的功能

复杂编码风格,II设置为1,将每个块分解为许多步骤,显式描述了资源的共享

Architecture

编码器的设计有Vivado IP集成模块组成:

kernel 模块:主要为主机提供一个通信接口,用于配置编码器并与编码器同步

Video Interface Processor (VIP) modules,视频处理接口:负责读取输入视频数据,对传入的数据进行重新排序,将其作为64 × 64像素的CTU块进行处理,并将结果写回DDR

Lookahead modules:对输入内容进行粗粒度的运动估计。这种粗略的运动估计代表了传入视频的基本时间特性,可以用于检测场景变化。

Rate Control module,码率控制模块:实现大致恒定的输出码率,设计实现了一种反馈控制算法来调整编码结果帧所需的成本(即比特数)

Final Encoder module,最终编码模块:从DDR读取CTU和粗运动向量,并正确地编码它们。产生的压缩比特流被存储回DDR中。

这些模块通过DDR接口和shell中的PCIe,实现了AXI互连、AXI流、时钟和重置等功能

Challenges

- 项目的大小:庞大的代码库和许多独立的组件,NGCodec采用的分层设计流程,对单个组件的更改可以相互隔离。IP组件和top-level c++仿真模型之间的分离可能使得它们之间不一致,产生矛盾。即使使用了分层设计和相对快速的c/ c++仿真,仿真时间仍然是一个瓶颈。

- 不同组件有不同的计算和内存需求,不同模块组合在一起增加了布局约束,使整体设计的布局和布线难度增加

Graph Processing

由于较低的计算/内存比率和不规则的内存访问模式,图处理通常受内存限制。现代的服务器级fpga通常配备高带宽存储器(HBMs),多个HBM通道可以同时存取来提高图处理性能。

之前有大量基于fpga的图处理工作针对特定的图算法,如BFS、PageRank和最短路径。

ENIAD报告了在Green Graph500基准测试中使用硬件-软件协同设计方法对near-data处理的破纪录结果,展示了在实际工作负载下使用fpga进行图形分析的性能和效率优势。

基于fpga的图处理框架可以处理多种图算法:GraphGen, GraphOps, HitGraph, ThunderGP。其中,ThunderGP使用HLS在fpga上实现图形加速器;它采用集合-应用-散射(gather-apply-scatter)对各种图算法建模,并通过高效加速器模板实现模型

上述这些框架需要为不同的图算法生成单独的比特流。

GraphLily

GraphLily是在HLS中设计的图形线性代数覆盖层,可以在配备hbm的fpga上实现高效和实用的图形处理工作负载加速。

优势:

- 它将不同的工作负载转换为相同的底层计算模式。提供一个统一的位流来处理多个图算法,而不是为每个算法生成单独的位流

- 提供了高效的、内存优化的稀疏矩阵密集向量乘法(SpMV)和稀疏矩阵稀疏向量乘法(SpMSpV)

- 与CPU,GPU相比,GraphLily实现了更好的吞吐量和能源效率。

Customized Matrix Storage Format,自定义矩阵存储格式

- 采用了基于PE的体系结构,将矩阵向量乘的任务分配给多个PE并行处理。

- 传统的稀疏矩阵存储格式,如压缩稀疏行格式(compressed sparse row format, CSR)分配数据在内存中非连续的位置,不适合在基于pe的体系结构中挖掘并行性。

主要贡献:

提出一种新的存储格式,称为循环打包的行流(cyclic packed streams of rows,CPSR),专门为配备hbm的设备设计

下面是一个具有两个通道的HBM上的CPSR示例,目标是用于SpMV的4-PE加速器:

Accelerator Architecture

对于每个HBM通道,实例化一个PE群以饱和内存带宽。每个PE都是一个三阶段的管道:从输出缓冲区读取值,更新结果,并写回更新后的值

Runtime Support.

GraphLily构建了一层中间件,简化了加速器的编程。中间件将每个加速器作为硬件模块向用户公开。用户通过指定必要的模块和调度模块的执行顺序来构造图算法。

目前的问题:

-

在GraphLily设计中,较大的输出缓冲区导致了高扇出的广播结构。

-

利用多个超逻辑区域(super logic regions,slr)的大型HLS设计可以产生跨slr的数据和控制信号。由于缺乏物理布局信息,现有的HLS工具往往无法准确识别这种cross-slr连接。

Acceleration of Genome Sequencing

基因组测序加速:Overlap,Layout,Consensus.

Overlap重叠阶段确定哪些读段具有匹配的子序列。

Layout布局步骤使用重叠信息连接连续读取以构建结果序列。

最后,Consensus共识步骤选择最可能的核苷酸序列。

RESEARCH CHALLENGES AND OPPORTUNITIES

- 使用HLS实现高时钟频率设计

AutoBridge在HLS编译器件将粗粒度的层级步骤和流水线结合。首先,识别在HLS综合过程中的长线,特别是跨越块边界的线,其次,AutoBridge将pipline寄存器自动插入到这些长导线上,使下游实现工具可以在不降低可达到的最大频率的情况下跨越块边界放置这些导线。防止将逻辑打包到单个块,有利于减少局部阻塞,提高频率。

- 应对复杂的编译指令和代码转换需要实现高性能

pragma语法的插入进行代码优化,设计编译器例如Merlin Compiler对这个过程进行部分自动化转换。用以实现并行化和流水线。并行化指定使用多个计算单元实现空间并行,而流水线实现时间并行,在时间上进行重叠计算

- 遗留代码重构需要符合HLS标准

将原先写在CPU上的代码进行自动重构,使其可以运行在FPGA上。

挑战:

指针不支持,不支持动态内存管理(就是new,malloc不能用),递归,位宽、多态,异常处理,多线程

-

对开源HLS基础架构的需求

-

支持dsl(Domain-Specific Languages)特定领域语言

应用在ML、图像处理等领域的特定语言或编译器框架,用于简化工作和更高的定制化。

- 标准化

不同FPGA的供应商提供的HLS工具很难编译相同的代码,收到支持的特性、库等差异使得代码的可移植性很低。

本文来自博客园,作者:xiongyuqing,转载请注明原文链接:https://www.cnblogs.com/xiongyuqing/p/16843630.html

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

2019-10-31 洛谷11.20我想AC队训练计划之贪心篇