Verilog 大小写敏感,且所有关键字都是小写

1 寄存器

register = storage,是数据存储单元的抽象,可视为能够存储数值的变量 (variable that can hold value)

关键字 reg; 缺省值 x;

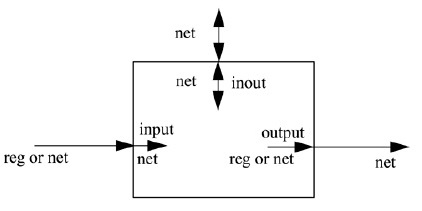

2 网络连接

net = connection, 表示寄存器之间的连接,只能采用连续赋值 (must be driven continuously)

关键字 wire; 缺省值 z;

2.1 D 触发器 (同步复位)

module dff(clk, rst, d, q); //dff with syn reset input clk, rst, d; output q; reg q; always @(posedge clk) begin if (rst) q <= 1'b0; else q <= d; end endmodule

2.2 D 触发器 (异步复位)

module dff(clk, rst, d, q); // dff with asyn reset input clk, rst, d; output q; reg q; always @(posedge clk or posedge rst) begin if (rst) q <= 1'b0; else q <= d; end endmodule

3 连续赋值 continuous assignment

assign data_left = data_right; // right drive left(net)

例:选择器 mux

assign data_out = select ? data_in1 : data_in0;

4 procedural assignment

1) 阻塞赋值 ("=")

execute sequential

2) 非阻塞赋值 ("<=")

read (right) -> schedule (left) -> execute (<=)

例: synchronizer

reg [1:0] data_sync; always @ (posedge clk or posedge rst) begin if (rst) data_sync <= 2'b00; else data_sync <= {data_sync[0], data_in}; end assign data_out = data_sync[1];

原文链接: http://www.cnblogs.com/xinxue/

专注于机器视觉、OpenCV、C++ 编程

浙公网安备 33010602011771号

浙公网安备 33010602011771号