基础008_定浮点转化[floating point IP]

作者:桂。

时间:2018-05-15 21:55:50

链接:http://www.cnblogs.com/xingshansi/p/9042564.html

前言

本文为Xilinx floating point IP的学习笔记,仅记录最基础的用法。参考文档:pg060-floating-point.pdf

一、IP核综述

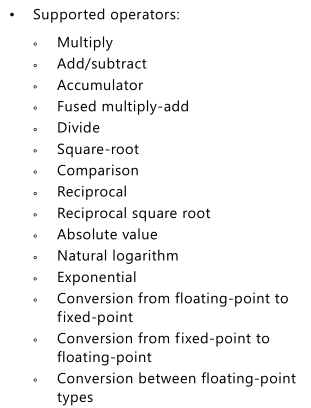

主要功能【基本思路是:1)输入接口:定点转浮点;2)各类浮点运算;3)输出接口:浮点转定点】:

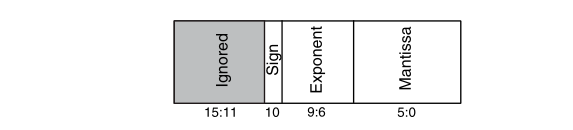

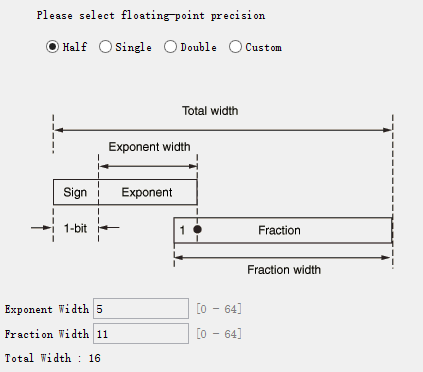

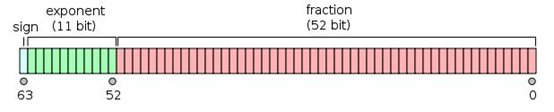

其中floating point涉及三种格式:

1)half:半精度,16位 = 1位符号 + 5 位指数 + 10位小数

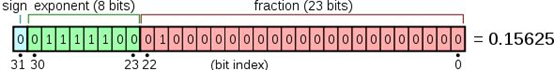

2)single:单精度,32位 = 1位符号 +8 位指数 + 23位小数

3)double:双精度,64位 = 1位符号 + 11 位指数 + 52位小数

举例:38414.4(10)=1001011000001110.0110011001100110011001100110011001100(2)

科学记数法为:1.001011000001110 0110011001100110011001100110011001100,右移了15位,所以指数为15。

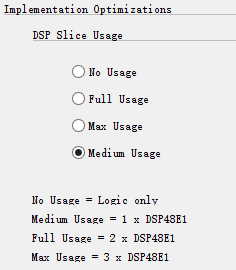

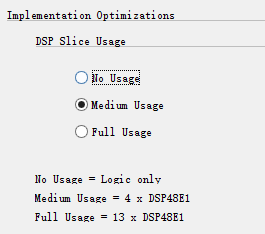

其中 DSP slice usage:

对应注解:

In short, it is generally best to use DSP slices if you have them avaialable. They are free, faster, and lower power. If you are running low on them, you can go back and balance speed with area to use DSP slices at the bottlenecks of the design and use fabric where you don't need the speed. 简而言之,DSP用的越多,时序可以越快。

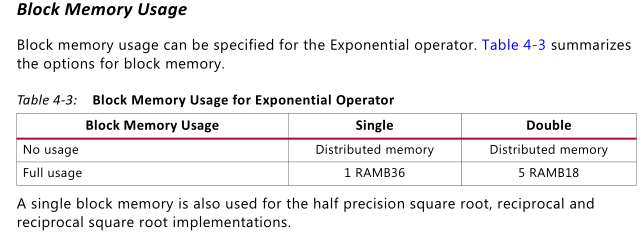

block memory usage:

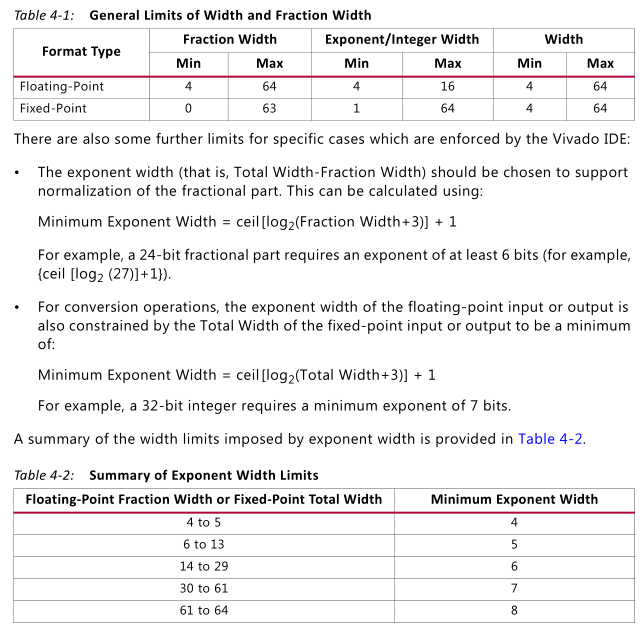

定点转浮点的对应关系:

二、仿真测试

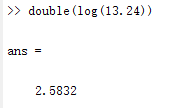

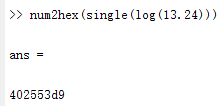

假设现在需要求:13.24的自然对数【对数也可以借助CORDIC直接进行定点计算】。

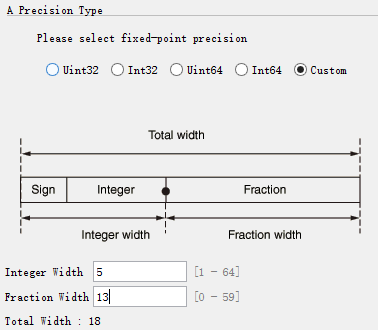

13.24设置定点数:

s_axis_a_tdata自动扩展为8的整数倍,如此处为18,则输出理论上为24bits,其余补零即可。

此处求对数使用medium usage:

testbench文件:

`timescale 1ns / 1ps /* Function: DPRAM for data aligned Author: Gui. Data: 2018年5月15日22:43:11 */ module ln_tb; //parameter //logic logic clk,rst; logic signed [17:0] data; //initial initial begin clk = 0; rst = 1; data <= 0; #8 rst = 0; #20 data <= 18'b011010011110101110;//+13.24 #1000 $stop; end always #2 clk = ~clk; //main logic s_axis_a_tready; logic m_axis_result_tvalid; logic [31:0] m_axis_result_tdata; //fix to float fix_to_float fix_to_float_inst ( .aclk(clk), .s_axis_a_tvalid(1'b1), .s_axis_a_tready(s_axis_a_tready), .s_axis_a_tdata({6'b0,data}), .m_axis_result_tvalid(m_axis_result_tvalid), .m_axis_result_tready(1'b1), .m_axis_result_tdata(m_axis_result_tdata)//output ); //float calculation: ln(outout) logic [31:0] result; floating_point_0 floating_point_0_inst ( .aclk(clk), .s_axis_a_tvalid(1'b1), .s_axis_a_tready(), .s_axis_a_tdata(m_axis_result_tdata), .m_axis_result_tvalid(), .m_axis_result_tready(1'b1), .m_axis_result_tdata(result) ); //float to fix , ignored endmodule

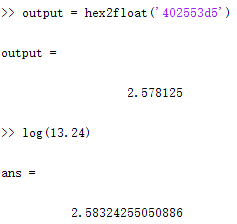

第一步定点转浮点:MATLAB输出

>> dec2bin(hex2dec(num2hex((single(13.24))))) %浮点的定点显示

%如果给了定点显示,计算对应的浮点值的指令?

这涉及到:浮点数与16进制数的转化,以32bit单精度为例:

- 浮点数转十六进制数:

num2hex(single(13.24))

- 十六进制转浮点数(正数为例,负数提取一个符号位即可,同时浮点->十六进制,只算绝对值):

functionoutput = hex2float(a)%convert hex to floatnum =dec2bin(hex2dec((a)));L =length(num);exppos = num((L-23):-1:1);expnum = 0;fori= 1:length(exppos)expnum = expnum +str2num(exppos(i))*2^(i-1);endexpnum = expnum - 2^7 + 1;fracpos = num(end-23:end);fracnum = 0;fori= 2:length(exppos);fracnum = fracnum +str2num(fracpos(i))*2^(-i+1);endfracnum = fracnum + 1;output = fracnum*2^expnum;从浮点角度对比FPGA与MATLAB输出:

二者非常接近。

对应VIVADO输出:

对数运算结果:

MATLAB结果:

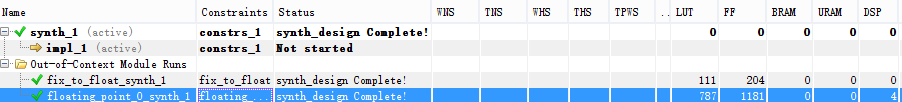

可以看出与MATLAB计算结果基本一致。另外,可写入module模块,综合后分析CLB、DSP等器件资源。

查看使用的器件资源:

定、浮点转化,消耗的仅仅是逻辑资源LUT、FF,求对数过程中,由于选择的是medium usage,对应四个DSP,仿真结果与理论一致,此为资源评估的依据。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语,封装的思维:从隐藏、稳定开始理解其本质意义

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 字符编码:从基础到乱码解决

2017-05-16 啸叫抑制(howling suppression)