Xilinx 常用模块汇总(verilog)【01】

作者:桂。

时间:2018-05-07 19:11:23

链接:http://www.cnblogs.com/xingshansi/p/9004492.html

前言

该文私用,不定期更新,主要汇总记录Xilinx常用的基本模块,列出清单,方便查阅。

关于原语,主要参考【原语时序为什么好,一个猜想是:我吃不同的食物,要去不同的餐厅,跑的路程自然多一些;而如果我有这些原材料,自己动手,费点功夫但跑的路少,路程长短对应时间长度、对应时序特性,这个是自己想当然,需要结合CLB特性。 此处待验证】:

一、模块汇总

- 1- adder

路径:印象笔记-1/0019/001

描述:三个数加、减混合运算

- 2- rtldelay

路径:印象笔记-1/0019/002

描述:数据延拍,延迟delayval-1拍

- 3- addsub_premitive

路径:印象笔记-1/0019/003

描述:两个数的加、减运算(实数)

- 4- abs

路径:*/003

描述:求绝对值(实数),与addsub_premitive类似,符号位作为标志位,正数x = 0 + x,负数x = 0 - x,输出即为绝对值。

- 5- selmax

路径:*/004

描述:求两个数据的最大值

- 6- amp_cal

路径:*/005

描述:复数幅度近似估计。

借助复数幅值近似估计一文的思路,进行复数幅度的近似计算,其中以上几个模块,此处被调用。

- 7- neg_primitive

路径:*/006

描述:求相反数-原语, 0 latency.

- 8- 常用延拍思路

路径:*/007

描述:4种常用延拍思路

- 9- 复数乘法

路径:*/008

描述:主要借鉴FFT节省资源的思路一文的思路,一个复数乘法需要3个乘法器。latency:0

乘法位宽的特性:

实数: 对于无符号数:n_bit x m_bit <= m+n_bit,有符号各添加1bit符号位

复数:有符号数,(n+1_bit x (m+1)_bit <= (m+n+2)_bit

output signed [2*width-1:0] outr; output signed [2*width-1:0] outi; assign outr = (ar-ai)*bi+(br-bi)*ar; assign outi = (ar-ai)*bi+(br+bi)*ai;

- 10- cplxmult_conj

路径:*/009

描述:复数共轭相乘,与复数相乘类似,bi换做-bi即可。直接处理内部也是调用DSP48,此处采用IP核(DSP48)进行硬件描述。 latency:4 clocks

关于DSP48,可参考:基础004_V7-DSP Slice,各IP核具体参数设置,参考印象笔记*/009截图。

- 11- cplxdelay

路径:*/010

描述: 复数数据移位,本质上:1)[实部, 虚部]拼成一个长数据,直接按实数移位的思路移位即可; 2)实部、虚部分别按照实数移位思路移位即可; 这里单独列出来,主要是改用shift_ram进行移位操作,思路上并无新意。 shift RAM参数设置可参考印象笔记*/010截图。depth即为延迟的拍数。

wire [datwidth*2-1:0] din = {din_i, din_r};

- 12- CORDIC

路径:*/011

描述:CORDIC计算幅度、相位,cordic原理可参考:Cordic算法简介。

主要分为:象限判定(-pi/2 ~ pi/2,因此根据xin符号位判定即可。)

其中(补码数据读取参考:FIR基本型仿真_03)

x_new = x+y*2^-i;%此处移位寄存器实现 y_new = y-x*2^-i;%此处移位寄存器实现可借助3- addsub_premitive模块求解,标志位由y符号位给出,generate迭代即可。

印象笔记目录:

二、原语简介

primitive 与 macro:

A primitive is the most basic FPGA element that can be instantiated with out any extra logic.

A macro is basically a combination of different primitives that requires logic beyond the most basic components. Primitives can be instantiated while macros cannot be instantiated in HDL.

We can add a macro to a schematic and generate the HDL so you can view combination of logic inside of the macro. We can then use this HDL in our design.

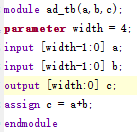

以一个基本的加法器举例:

查看schematic:

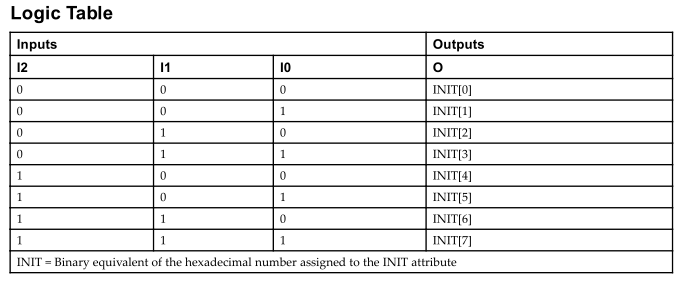

其中LUT为查找表,实现逻辑功能,由于LUT是基本单元,可调用原语,以LUT3为例:

原语在hdl.pdf或language template可查看: