AXI MCDMA 仿真与工作流程分析

说明

关于背景知识,可以先看 https://www.cnblogs.com/xingce/p/16386108.html

引用一段官方的说明,AXI MCDMA存在的主要目的是为了节约资源,我们想要使用这个模块的主要目的也是为了降低资源消耗,从而可以将系统部署在更小面积的FPGA芯片上,当然,具体的效果还需要进一步的测试,先对该IP做一些仿真和在线测试吧。

FPGAs have been providing DMA engines in the Programmable Logic for many years. To add to the existing DMA offering, Xilinx added a Multichannel DMA IP into the Xilinx IP Catalog to provide additional channels. Additional DMA channels provide a hardware segregation of data that ultimately provides more efficient management of data streams. This leads to an overall savings of Programmable Logic, while maintaining data movement throughput.

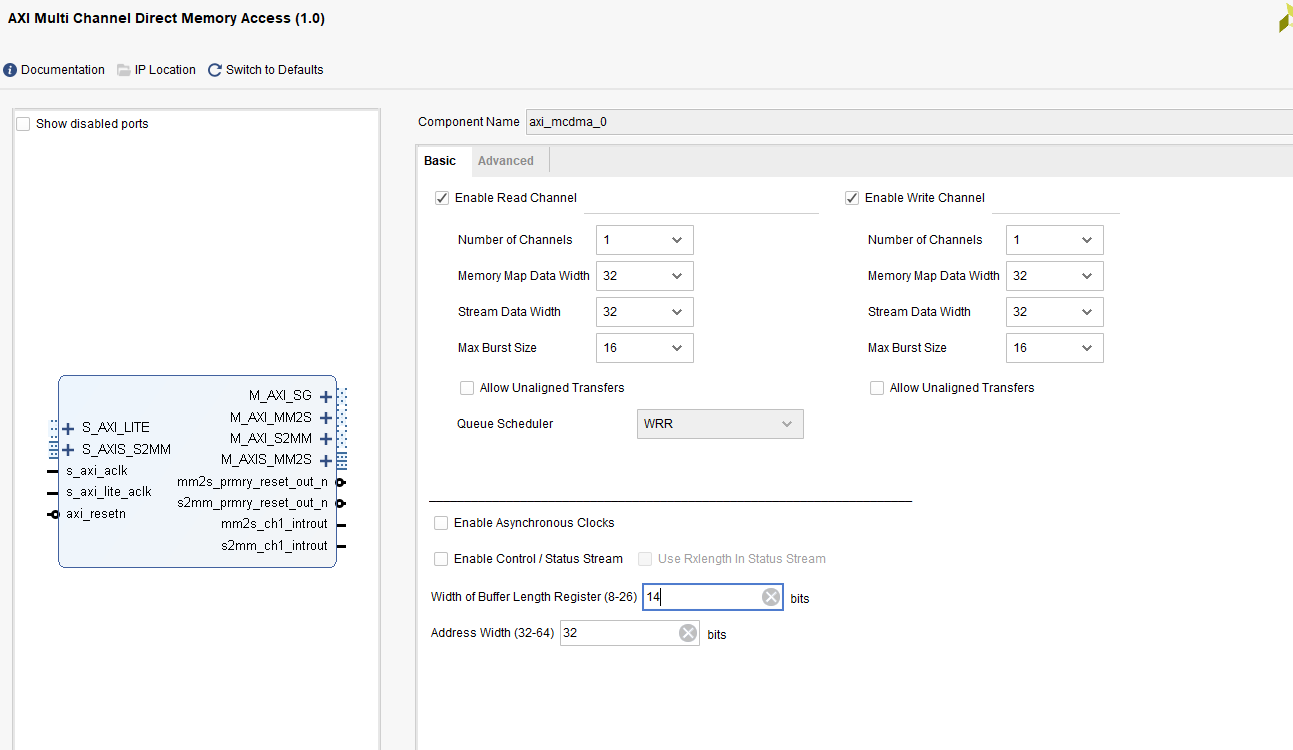

下图是IP的接口和配置界面,更详细的描述请移步官方手册 https://docs.xilinx.com/v/u/en-US/pg288-axi-mcdma

初步目标

在开始之前,先确定一个目标,我们希望通过该仿真的学习,搞清楚IP的基本配置、工作流程,然后去创建自己的仿真工程

官方仿真范例

选择打开IP的example design,查看其仿真工程

先来看看顶层的*tb.v 仿真文件,里面生成了1个200M的基准时钟,然后发送了start开始信号,并检测结束done信号与status信号,根据status的状态输出测试结论,核心的测试代码不在这个文件里面

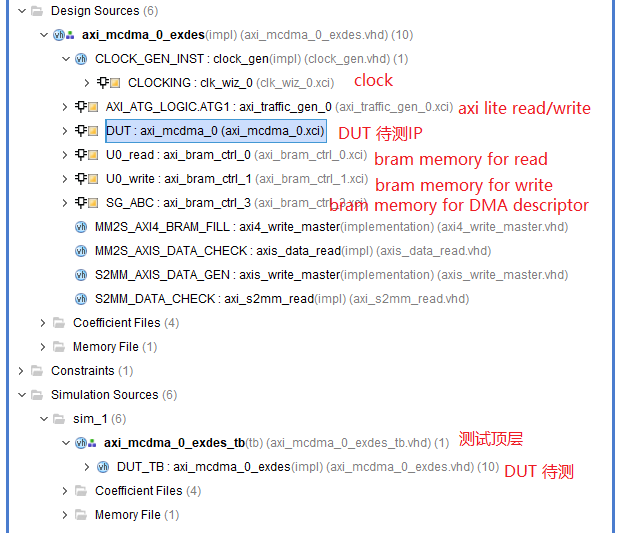

再来直接看DUT的顶层文件,先搞清楚对应的额层级关系

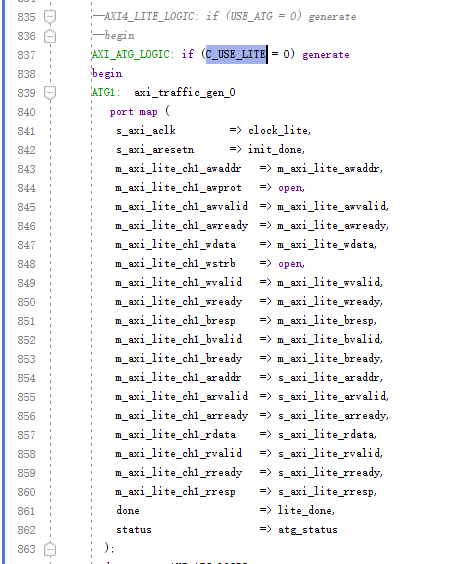

下图表明axi_traffic_gen_0 用作mcdma的axi lite master模块,完成对mcdma 寄存器的配置

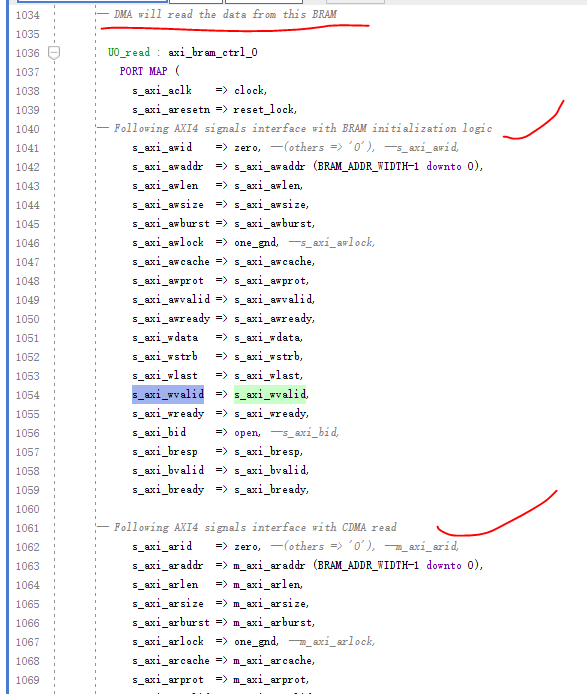

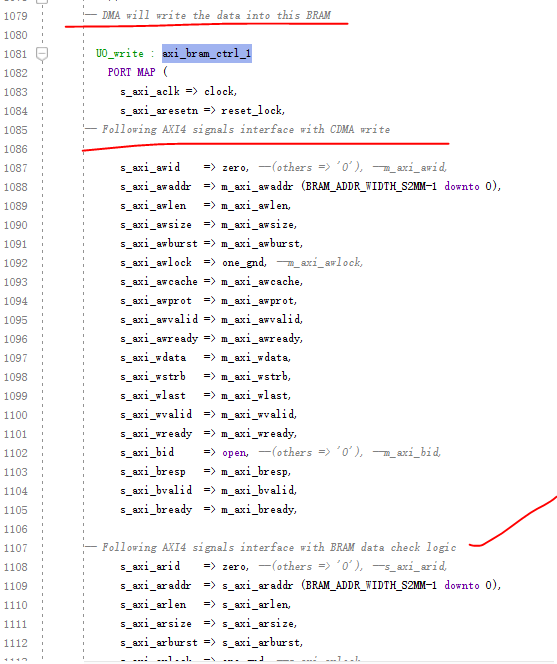

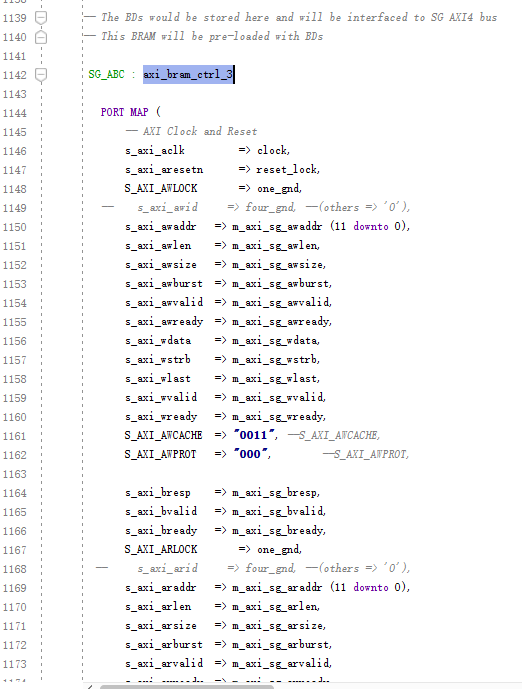

AXI MCDMA会读出BRAM_CTL_0 中的数据,那么BRAM 0中的数据怎么才知道是不是对的,又需要一个模块写入测试数据,这个测试数据由axi4_write_master.vhd模块完成,在系统复位解除后,就开始写入测试数据

与读出通道对应,AXI MCDMA会向BRAM_CTL_1写入测试数据,检查数据正确性的时候,测试逻辑是直接检查的写入信号,并不是将BRAM 1中写入的数据读出做校验,这一点需要查看仿真波形,有可能设计人员偷懒,所以这样写的

descriptor信息预先存储在BRAM_CTL_3中,由AXI MCDMA的AXI SG接口将对应的信息读出,对应的descripto信息存储在"sg_mem.mem" 文件中

从以上信息基本可以看清整个仿真逻辑了,接下来再结合仿真信号看看真实的工作流程。

仿真信号查看

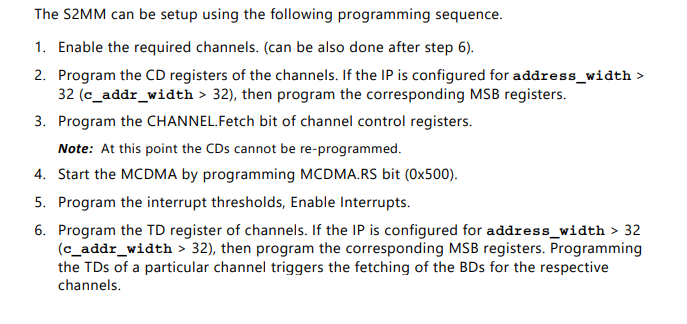

首先,根据IP手册,AXI MCDMA开始工作之前,需要配置对应寄存器

先看S2MM 写操作对应的流程,MM2S也是对应的流程,这里不介绍了,可以看仿真的时序和IP手册的说明

这是IP手册建议的流程

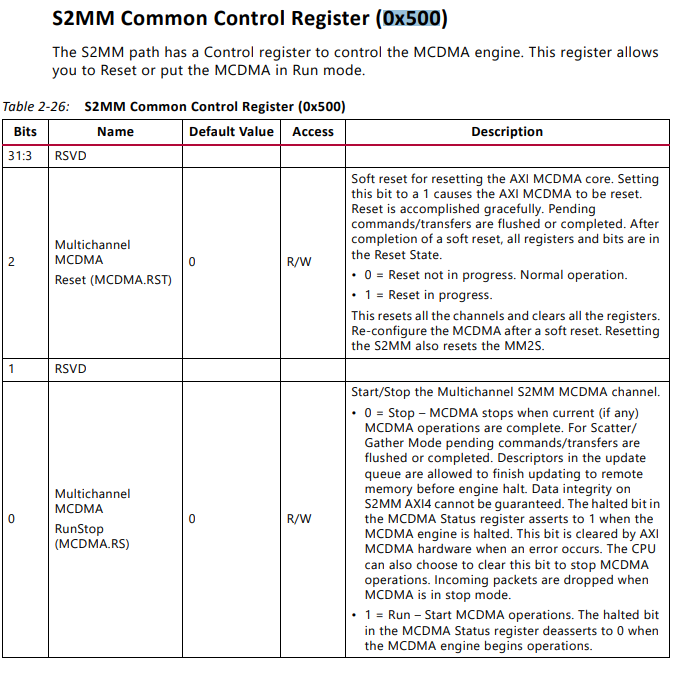

首先,需要先将MCDMA的S2MM 对应channels Run起来

向0x500 寄存器写入控制数据

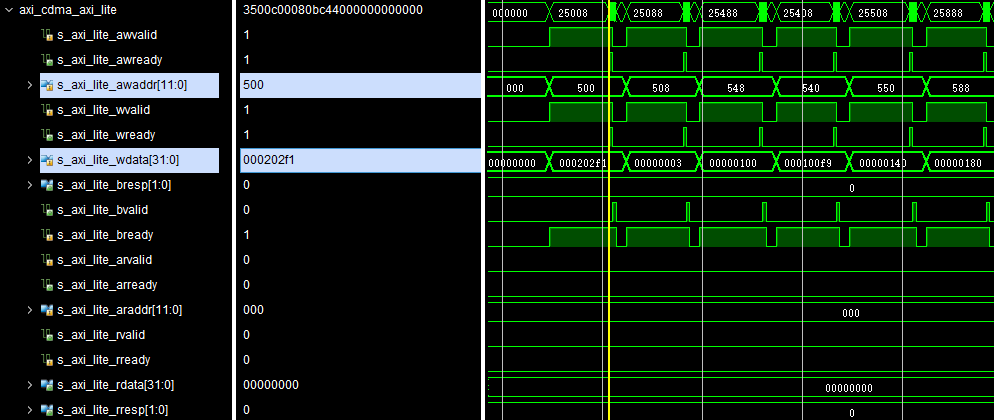

对应仿真时序图如下,其中基地址为0x500 ,写入数据为0x000202f1

使能对应通道

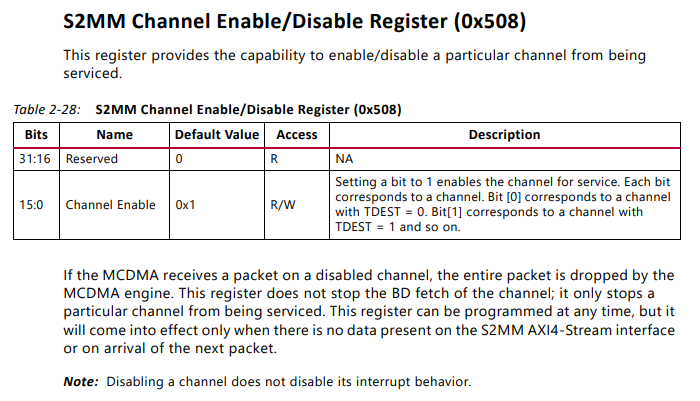

向0x508寄存器写入对应参数,当disable的时候,并非真的stop了,而是当descriptor 链表对应也执行到含EOF标志的链表时才真正停止。

(这里有个问题就需要注意,如果是读出操作,我们丢弃不需要的数据,如果是写入操作,如何结束呢?)

应该向0x008写入0x1 使能MM2S的channel 0,仿真实际写入的是0x3,这个是由于仿真代码是设定的2个通道,2个通道是合理的,因为只有这样才能体现出Multichannel DMA的意义

配置descriptor 对应的地址

IP根据配置的descriptor地址去memory中fetch对应的descriptor链表,然后执行对应的axi读写操作

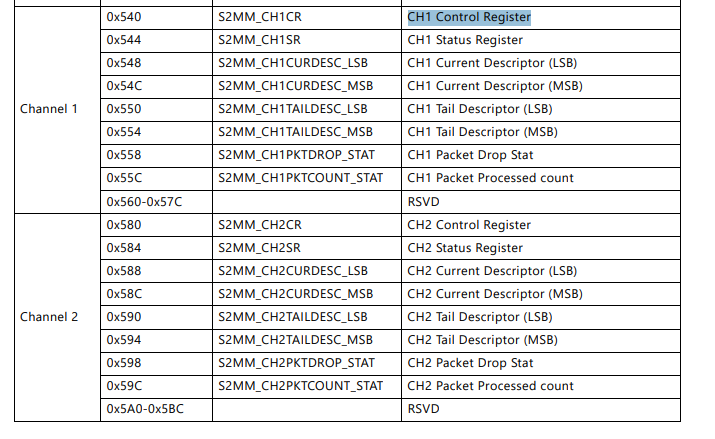

下面描述了对应channel 0 1的descriptor地址,由于我们是32bit 地址区间,所以只需要对应配置LSB 32bit地址即可,MSB 是在超过32bit地址空间的空间才有效

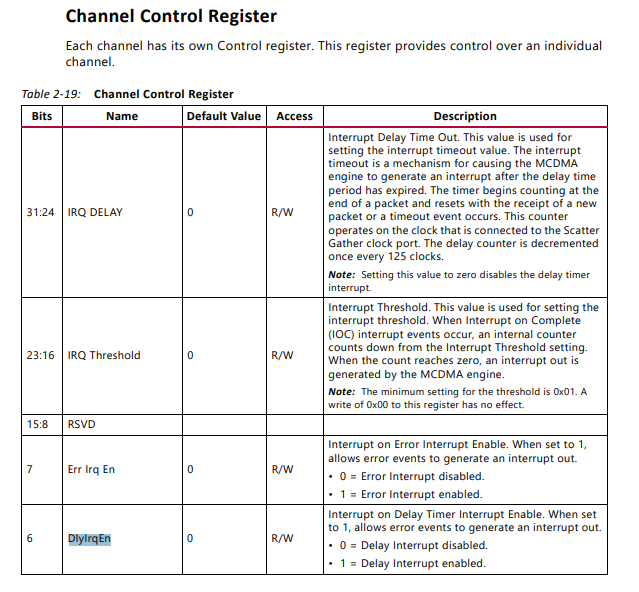

配置通道控制寄存器

每个通道都有自己的配置寄存器,这些寄存器第0个bit是开启descriptor的featch,其它bit基本都是和中断的产生相关的,仿真范例对S2MM和MM2S 通道进行了不同的设置,这个可以从仿真波形观察得到

BD descriptor的读取

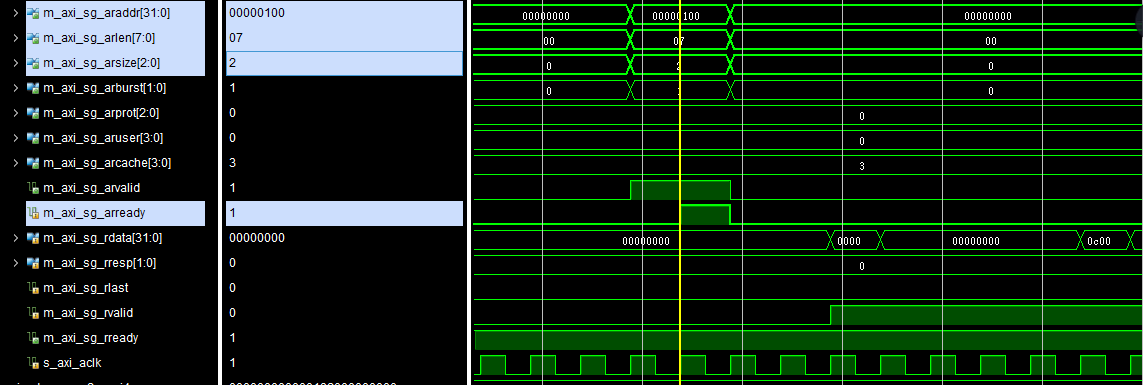

通过观察寄存器写入的值,可以看出S2MM 的channel 0 对应写入的current BD 地址为0x100 , nexr BD 地址为0x140

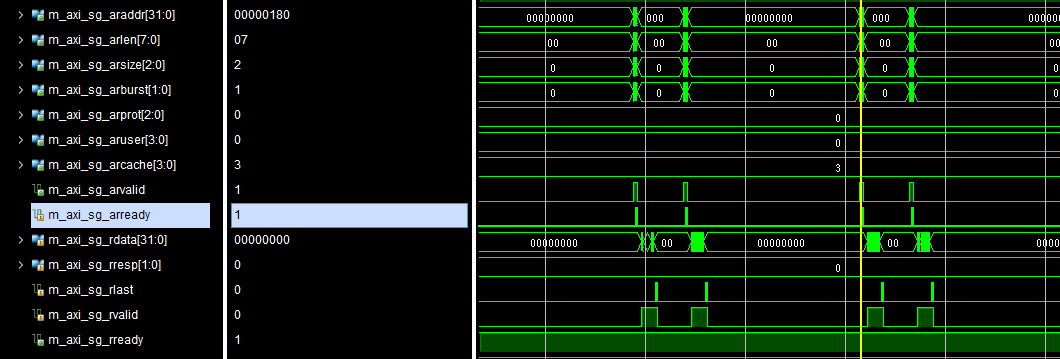

下图是对应的时序,图中不能看出具体的地址,如果想看的话可以自己仿真,然后放大观察

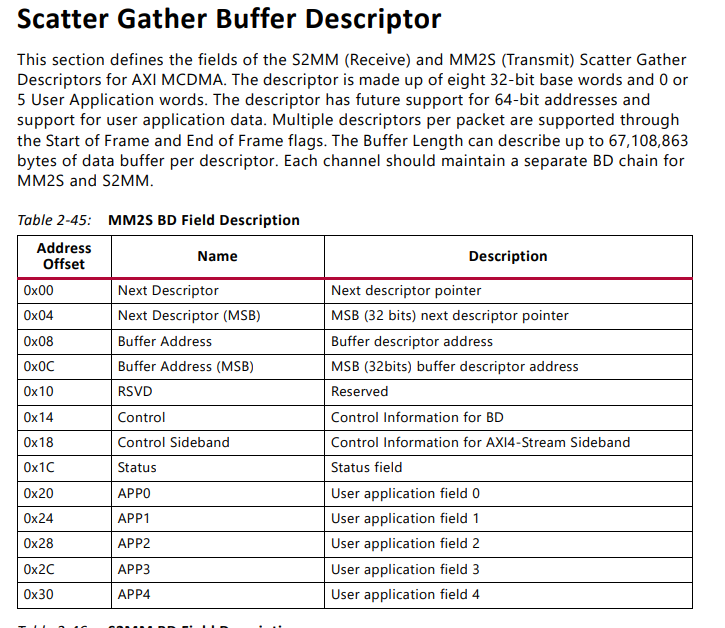

BD descriptor 描述,下图描述了MM2S对应的descriptor描述,S2MM也是类似的内容,AXI MCDMA对应的通道会根据这个descriptor完成对应的dma操作

在这个仿真范例中,我们看一下

SG从0x100地址读指定 8*32bit的descriptor数据,然后根据descriptor去读取数据

整体看下来,这个仿真demo是非常简易的,不能覆盖真实的工况,下一步需要上机测试才能更好的模拟真实工作场景

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 全程不用写代码,我用AI程序员写了一个飞机大战

· DeepSeek 开源周回顾「GitHub 热点速览」

· 记一次.NET内存居高不下排查解决与启示

· MongoDB 8.0这个新功能碉堡了,比商业数据库还牛

· .NET10 - 预览版1新功能体验(一)