【笔记】ARM Cortex-M0从这里开始

page 标注书本

pdf 标注(E:\kpan\Desktop\LPC\LPC1200_um_en.pdf )

page21

1.AHB Home Address Block,内部地址块

2.CC2530 f256 f256的意思是Flash配置为256KB.

page29

1.NVIC(Nested Vectored Interrupt Controller 嵌套矢量中断控制器

pdf8

1. Fig 2. LPC122x memory map 内存映射关系.

2013年3月26日 23:56:24

http://www.zlgmcu.com/nxp/lpc1000/lpc1200.asp周立功单片机

LPC12XX系列ARM特性

LPC1200系列ARM是基于Cortex-M0内核的微控制器,具有高集成度和低功耗等特性,可用于嵌入式应用。Cortex-M0是第二代ARM内核,它可为系统提供更高的性能,如增强的调试特性和更高密度的集成。基于Cortex-M0的优势,LPC1200可在相似应用中实现更低的平均功耗。

LPC1200系列Cortex-M0微控制器可在高达45MHz的CPU频率下运行,包含高达128KB片内Flash存储器和8KB数据存储器。较小的512字节Flash擦除扇区带来了多种设计上的好处,如更精细的EEPROM仿真,支持从任意串行接口启动加载,减少了对RAM缓存容量的要求,从而为现场编程带来便利。

LPC1200系列Cortex-M0微控制器的外设组件包括一个10位ADC(8通道)、两个带有输出反馈的模拟比较器、两个UART接口、一个SSP/SPI接口、一个带有快速模式的I2C接口、一个看门狗定时器、一个DMA控制器、一个CRC计算及校验模块、四个通用定时器、一个32位RTC和多达55个通用I/O引脚。

LPC12D00系列Cortex-M0微控制器:LPC12D27可驱动静态或复合LCD(高达4个背极和40段)可以很容易的级联多个LCD驱动器,最多驱动2560段,可应用在大型显示场合。

- 特性

- 处理器内核

- ARM Cortex-M0内核,运行速度高达45MHz

- 内置嵌套向量中断控制器(NVIC)

- SWD调试接口

- 系统节拍定时器

- 片内存储器

- 高达8kB SRAM

- 高达128kB片内Flash存储器

- 可通过片内引导装载程序软件实现在系统编程(ISP)和在应用编程(IAP)功能

- 时钟产生单元

- 晶体振荡器工作频率1MHz~25MHz

- 12MHz的内部RC振荡器精度为1%,可选择作为系统时钟

- PLL允许CPU在最大CPU速率下工作,而无需高频晶振,可从主振荡器、内部RC振荡器或看门狗振荡器运行

- 时钟输出功能可反映主振荡器时钟、IRC时钟、CPU时钟和看门狗时钟

- 实时时钟(RTC)

- 电源

- 3.3V单电源供电(2.0V~3.6V)

- 具有三种低功耗模式:睡眠模式、深度睡眠模式和深度掉电模式

- 12个拥有专用中断的GPIO可将CPU从深度睡眠模式中唤醒

- 掉电检测带三个独立阈值,每个阈值都可用于中断和强制复位

- 上电复位(POR)

- 集成了PMU(电源管理单元),可在睡眠、深度睡眠和深度掉电模式中极大限度地减少功耗

- 数字外设

- 21通道Micro DMA控制器

- 硬件CRC计算及校验模块

- 两个带有小数波特率发生器和内部FIFO的UART。其中UART0带RS-485并支持调制解调器,UART1为带IrDA的标准UART

- SSP控制器,带FIFO和多协议功能

- I2C总线接口,完全支持I2C总线规范和快速模式Plus,数据速率为1Mbit/s,具有多地址识别功能和监控模式

- 4个可编程的大驱动电流(16mA)引脚

- 多达55个通用I/O(GPIO)引脚,可编程为上拉、开漏模式,可编程的数字输入干扰滤波

- GPIO均可配置为边沿或者电平中断

- 四个通用定时/计数器,带有四个捕获输入和四个匹配输出(32位计时器)或两个捕获输入和两个匹配输出(16位计时器)

- 窗看门狗定时器

- 4×40段LCD驱动(LPC12D27)

- 模拟外设

- 一个8通道10位ADC

- 两个高度灵活的模拟比较器,模拟比较器的输出可以编程为定时器的匹配信号,也可模拟555定时器

- 封装

- LQFP100、LQFP64和LQFP48封装

page50

1.工程建立和编程规范

(1) 文件存储管理

*System

*source

*project

*out

*GPIO

*DOC

*Core

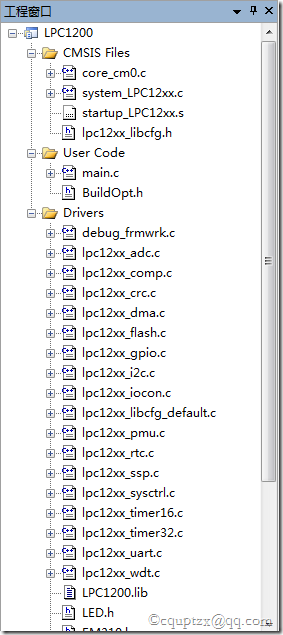

(2)实际工程窗口:

(3)代码分类

- H头文件:引脚定义,宏定义,全局变量,内部函数,外部函数.

- C文件中:尽量与硬件无关,只存放变量和代码

- 变量的定义:使用宏或者是typedef

(4)编程规范

- 注释://行后单行注释,/**/多行注释

- 文件头:a.文件名 b.版本. c参数 d.使用的工具 e.描述信息

- 函数头格式: 函数名 描述 参数 返回值

- 文件结束

- 变量命名

- 预编译 a宏定义 b数据类型typedef c条件编译

page57

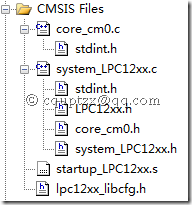

1.CMSIS

ARM Cortex™ 微控制器软件接口标准(CMSIS:Cortex Microcontroller Software Interface Standard)

2.CMSIS分层

- 核心外设访问层CPAL Core Peripheral Acess Layer

定义内部寄存器地址,功能函数(内部寄存器,NVIC,调试子系统的访问)

- 中间件访问层MWAL Middleware Acess Layer

通用API

- 设备访问层 DPAL Device Peripheral Acess Layer

定义 硬件寄存器的地址,对外设的访问函数,

3.CMSIS规范

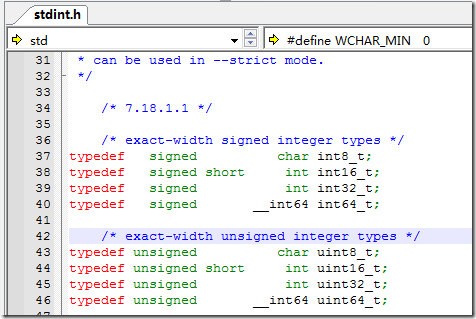

- stdin.h 包含了对8,16,32位等数据的指示符定义,用来屏蔽不同编译器的差异

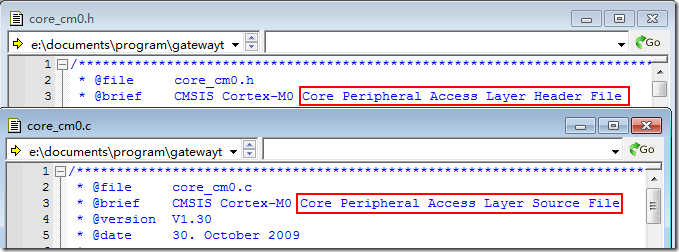

- core_cm0.h和core_cm0.c 包含了Cortex-Mx的全局变量的声明和 定义了一些静态功能函数

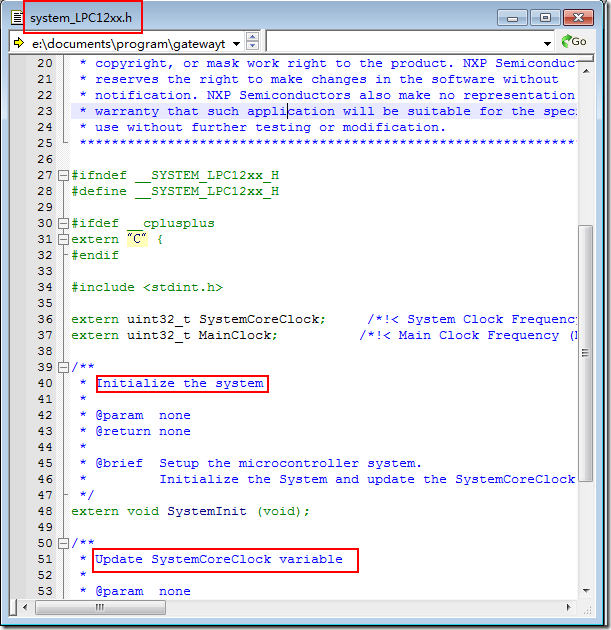

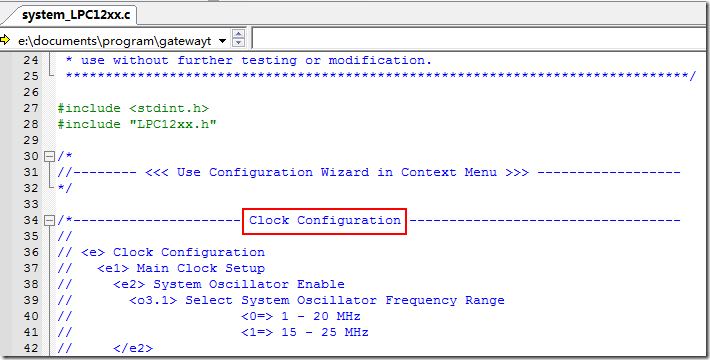

- system_LPC12xx.h和system_LPC12xx.c 定义的是

- 系统初始化函数

- 系统时钟的定义

- 时钟变量

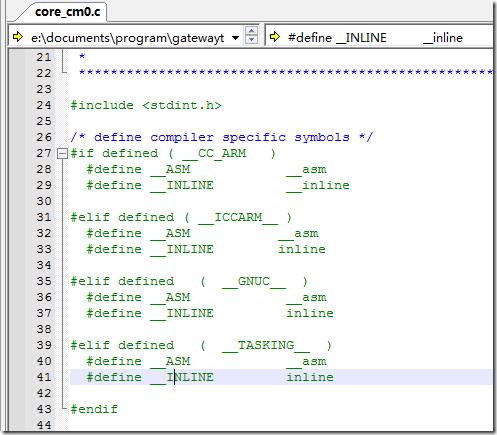

(1)工具链

CMSIS支持三大主流工具链:MDK,IAR,CNU,在core_cm0.c中的定义来屏蔽一些编译器的内置的关键字的差异:

1: #include <stdint.h>

2:

3: /* define compiler specific symbols */

4: #if defined ( __CC_ARM )

5: #define __ASM __asm /*!< asm keyword for ARM Compiler */

6: #define __INLINE __inline /*!< inline keyword for ARM Compiler */

7:

8: #elif defined ( __ICCARM__ )

9: #define __ASM __asm /*!< asm keyword for IAR Compiler */

10: #define __INLINE inline /*!< inline keyword for IAR Compiler. Only avaiable in High optimization mode! */

11:

12: #elif defined ( __GNUC__ )

13: #define __ASM __asm /*!< asm keyword for GNU Compiler */

14: #define __INLINE inline /*!< inline keyword for GNU Compiler */

15:

16: #elif defined ( __TASKING__ )

17: #define __ASM __asm /*!< asm keyword for TASKING Compiler */

18: #define __INLINE inline /*!< inline keyword for TASKING Compiler */

19:

20: #endif

(2)中断异常

- 系统异常 负数

- 设备异常 从0开始

异常和中断标识符必须加上后缀_IRQn

中断在LPC12xx.h中定义:

e:\documents\program\gatewayt0928\lpc12xx\lpc12xx.h

1: typedef enum IRQn

2: {

3: /****** Cortex-M0 Processor Exceptions Numbers ***************************************************/

4: NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */

5: HardFault_IRQn = -13, /*!< 3 Cortex-M0 Hard Fault Interrupt */

6: SVCall_IRQn = -5, /*!< 11 Cortex-M0 SV Call Interrupt */

7: PendSV_IRQn = -2, /*!< 14 Cortex-M0 Pend SV Interrupt */

8: SysTick_IRQn = -1, /*!< 15 Cortex-M0 System Tick Interrupt */

9:

10: /****** LPC12xx Specific Interrupt Numbers *******************************************************/

11: WAKEUP0_IRQn = 0, /*!< All I/O pins can be used as wakeup source. */

12: WAKEUP1_IRQn = 1, /*!< There are 12 pins in total for LPC12xx */