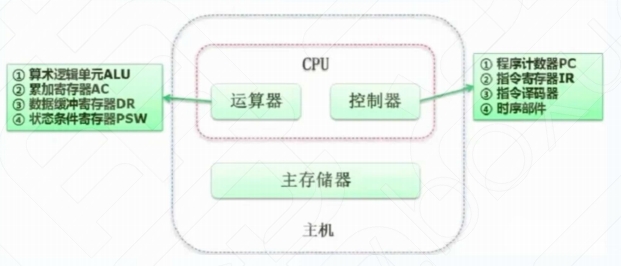

计算机组成与体系结构-CPU组成

CPU由控制器和运算器两大部分组成,在控制器的控制之下,运算器存储器和输入输出设备等部件构成了一个整体。

CPU的控制器

程序计数器(PC):存放下一条指令在内存的地址.在指令周期中,CPU首先将程序计数器中存储的地址送到地址总线上,以便从内存中读取对应地址的指令操作码。

指令寄存器(IR):存放即将要执行的指令

指令译码器(ID):翻译指令(操作码+操作地址)

地址寄存器(AR):保存当前CPU所访问的内存地址

时序部件:提供时序控制信号(计算机时钟)

寄(计数器)

存(指令寄存器)

遗(译码器)

址(地址寄存器)

时(时序部件)

CPU的运算器

执行算术运算(加减乘除等)和逻辑运算(与或非等)

算术逻辑单元(ALU):

实现对数据的算数和逻辑运算

累加寄存器(AC):

通用寄存器,为ALU提供一个工作区,暂存

数据缓冲寄存器(DR):

读写内存,暂存的指令或数据

状态条件寄存器(PSW):

存状态标志及控制标志

鸡(逻辑)

同(通用寄存器)

树(数据缓冲)

撞(状态PSW)

流水线

指令流水线的操作周期由最慢的阶段决定,以确保所有阶段都有足够的时间完成各自的操作。当四个阶段分别需要的时间分别是8ns、9ns、4ns、8ns.操作周期应至少等于最长的操作时间,即最长阶段的时间。在这里,最长阶段是取数阶段,重要9ns。因此,该流水线的操作周期应至少为9ns,以确保每个阶段都能在规定时间内完成,不会出现阻塞或延迟。

要使加速比和效率最大化应该对流水线各级采用相同的运行时间:为了最大化流水线的效率和加速比,理想情况下,每个阶段的运行时间应该相同,这样可以避免流水线停滞或过度填充

流水线采用异步控制会明显提高其性能:异步控制流水线(即每个阶段不依赖于统一的时钟信号)可能会增加复杂性,并且可能导致数据依赖性和同步问题,从而影响性能。通常,采用同步控制的流水线更容易管理,且性能更为稳定。

寻址方式

隐含寻址:隐含寻址是指操作数的地址隐含在操作码中,并不显式指出操作数的位置。

寄存器寻址:寄存器寻址是指操作数存放在寄存器中,指令中使用寄存器编号来访问

立即寻址:立即寻址直接将操作数的值嵌入到指令中。

直接寻址:直接寻址是指操作数的地址直接放在指令中,指令执行时直接使用这个地址访问内存。

考点

冯诺依曼计算机根据指令周期的不同阶段,来区分从内存中取出的是指令还是数据。

指令周期分为4个部分:取指周期,这个周期取出的是指令操作码,地址码

间接寻址周期,找到有效地址(内存物理地址)。

执行周期,这个周期取出的就是数据。

中断周期,检查有没有中断信号。

考点

从发出中断请求到开始进入中断处理程序:这段时间是指从外设发出中断请求到CPU开始执行中断处理程序之间的时间。它是CPU的中断响应时间中的关键部分,是开始执行中断处理所经历的延迟时间。

浙公网安备 33010602011771号

浙公网安备 33010602011771号