clock gating check

在 sta 分析时,经常会碰到 clock gating cell (一般是 ICG cell 或者 latch)引起的 violation,这种 violation 很常见,而且往往很难修。

为什么 gating cell 容易出问题?出了 violation 又该如何解呢?

首先,gating cell 容易出问题是因为其一般出现在 clock path 的中间,而且往往比较靠近 clock source,其latency 较小,当 tool 去check gating cell 的timing 时,其sink point 是在gating cell上,而 CTS 的sink point 是在 gating cell 后面的register, 所以对包含 gating cell 的 path 就会出现:launch clock 较长,而 latch clock 很短的情况,于是导致严重的 setup violation。

################## update 0321 #########################

以 ICG cell 为例,常见的 clock gating check 的 path 如下图:

图中 Reg1 产生 clock enable 信号,用来控制 ICG cell 的开关状态,

在 cts 阶段,tool 在图中会看到两个 sink 点: Reg1/CK, Reg2/CK ,

所以 tool 会对这两个点做 balance,那么做完 cts 后就有: T1 =~ T2 + T3 ;

但是在 sta 时,由于 enable 信号是由 CLK 采集的,所以需要 check 从 Reg1 到 ICG cell 的 timing,

此时 launch clock latency = T1 , capture clock latency = T2,

又因为 T1 =~ T2 + T3 , 所以可以认为 T1 >> T2,

这样 capture clock 就比 launch clock 短很多,很容易出现 setup violation !

那么这种 violation 该怎么解呢?

两种思路: 1) 缩短 data path 或者 launch clock, 2) 垫长 capture clock

首先,垫长 capture clock 不太可行,因为 gating cell 一般都比较靠近 source 点,后面 fanout 较多,影响可能比较大;

而缩短 data path 也不好做到,因为从 start register 到 gating cell 一般比较近,能够缩的余地不大;

所以综合考虑,缩短 launch clock path (即缩短T1)是最佳选择。

缩短 T1 可以用 float pin 来实现,

set_clock_tree_exceptions -float_pin Reg1/CK -float_pin_rise 0.5

甚至可以考虑 抓出所有产生 enable 信号的 register,让它们单独 cts,不要和 gated clock 做 balance

#######################################################

一般 clock gating cell 是 AND 、OR 、latch、ICG ,常见的的一种 gating 结构如下图:

图中的 register 是用于同步 EN 信号,防止出现亚稳态或毛刺

如果将这个 reg 和 AND 封装起来做成单个cell,就是一个简单的 ICG cell。

此外,用 AND 做的 gating cell 容易产生 clock glitch或 clipped clock,原因如下图:

##################################################################

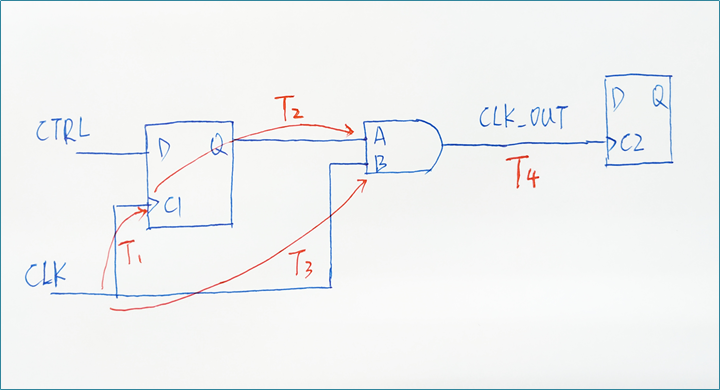

典型的 clock gating check timing path 如下图:

图中gating cell 的 B 端是clk,A 端是 enable,A 端的电平变化可以控制 B 端的 clk 是否送出去,以此控制gating cell 的开关

首先 CTS 是去 balance “从source 到 C1(就是T1)” 和 “从 source 到 C2(就是T3+T4)” 这两段clock,即 T1 =~ T3+T4;而 gating check 时,launch clock path 是 从source到C1(就是T1),而 latch clock path 是 从source到B(就是T3),又因为gate cell 一般靠近source,所以这里 T3 比 T1 小得多,skew 超大,于是 gating check 就会出现较大的 setup violation。

那么这种 violation 改如何解呢?

两种思路: 缩短 data path 或者 launch clock path, 垫长 latch clock path

首先,垫长 latch clock path 不太可行,因为 gating cell 一般都比较靠近 source 点,后面fanout较多,影响可能比较大;

而缩短data path 也不好做到,因为从 start register 到 gating cell 一般比较近,能够缩的余地不大;

所以综合考虑,缩短 launch clock path (即缩短T1)是最佳选择。

缩短 T1 可以用 float pin 来实现,

set_clock_tree_exceptions -float_pin C1 -float_pin_rise 0.5

其它与 clock gating 相关知识:

1. set_clock_gating_check -setup 0.2 开启 gating check 并预留 0.2 的 setup margin,设置这个margin 可以压短 data path

2. DC 综合时可以用 set_clock_gate_latency,在综合时就考虑到 gating path 的 timing 问题

3. gating cell 一般是 AND ,OR ,latch,ICG