SoC FPGA JTAG电路设计 要点

JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试布局紧凑的PCB板上元件的能力。边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据。

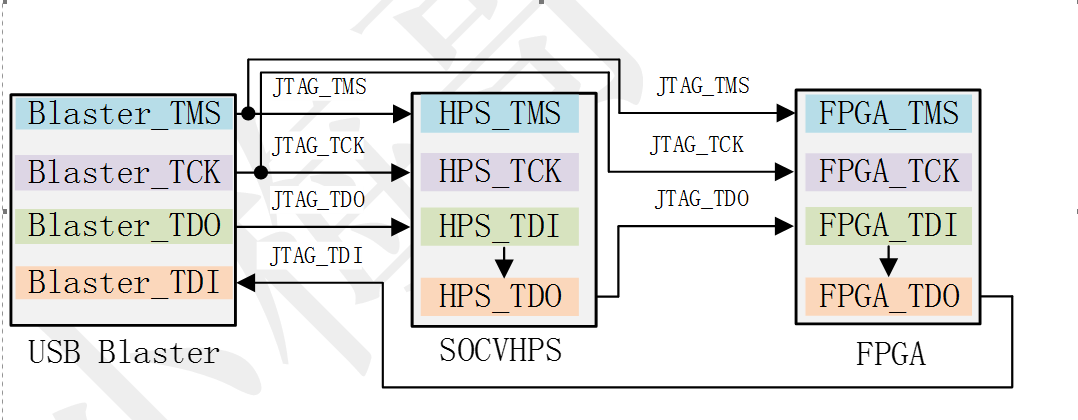

SoC FPGA作为在同一芯片上同时集成了FPGA和HPS的芯片,其JTAG下载和调试电路相较于单独的FPGA或ARM处理器都有一些差异,但是同时两者又有紧密的联系。AC501-SoC开发板上的JTAG链同时连接了FPGA和HPS。使用时,仅需一个JTAG链路,就能同时调试FPGA和HPS。FPGA和HPS各自有其独立的JTAG信号引脚,电路设计时使用了一种串行链的方式来将两者连接到一起,如图xxx所示:

以下为4个JTAG信号的功能说明:

|

管脚名称 |

管脚类型 |

说明 |

|

TDI |

测试数据输入 |

指令以及测试和编程数据的串行输入管脚的。数据在TCK 的上升沿移入。如果在电路板上不需要JTAG 接口,可以通过将此管脚连接至VCC来禁用JTAG。TDI 管脚具有内部弱上拉电阻(通常为25KΩ)。 |

|

TDO |

测试数据输出 |

指令以及测试和编程数据的串行数据输出管脚。数据在TCK的下降沿移出。如果数据没有从器件中被移出,此管脚处于三态。如果在电路板上不需要JTAG接口,悬空此管脚以禁用 JTAG 电路。 |

|

TMS |

测试模式选择 |

提供的控制信号输入管脚,控制信号用来控制TAP状态机的跳变。状态机跳变发生在 TCK 的上升沿。因此,TMS必须在 TCK 的上升沿之前被设置。 TMS 在 TCK 的上升沿中被评估。如果在电路板上不需要 JTAG 接口,JTAG 电路被禁用连接此管脚至 VCC。 TMS 管脚具有内部弱上拉电阻 (通常为25KΩ)。 |

|

TCK |

测试时钟输入 |

边界扫描电路的时钟输入脚。一些操作发生在上升沿,而其它的则发生在下降沿。如果在电路板上不需要JTAG 接口,JTAG 电路被禁用连接此管脚至 GND。 TCK 管脚具有内部弱下拉电阻。 |

使用JTAG配置或调试一个器件时,根据用户选定的器件,编程软件(Quartus Programmer或DS-5中提供的调试器)会旁路所有其它的器件。在旁路模式下,器件通过一个旁路寄存器将编程数据从 TDI 管脚传至 TDO 管脚,即通过TDI送入器件的配置数据会在一个时钟周期之后呈现在TDO上。而如果将TDO端口输出的数据再次接入另个器件的TDI端口,则能够直接对下一个器件进行调试了。而每一个器件都有其JTAG ID,通过JTAG ID能够辨识具体调试哪个器件。

在图xxx(上图)可以看到,由USB Blaster的TDO输出的数据首先是接入到了HPS的TDI端口,然后由HPS的TDO端口流出的数据又接到了FPGA的TDI端口上,最后数据再由FPGA的TDO端口流出,回到USB Blaster的TDI端口,形成了完整的数据回路。

当需要通过Quartus Programer来配置或调试FPGA部分时,会设置直接旁路HPS部分,由HPS的TDI端口流入的数据会在一个时钟周期后出现在HPS的TDO端口上,再进入HPS的TDO端口所连接的FPGA的TDI端口。从而向FPGA的各个寄存器中写入或读取出数据,通过FPGA的TDO端口输出,流入到USB Blaster的TDI端口,完成对FPGA的调试。

当需要通过DS-5中的仿真器来调试HPS部分时,会设置直接旁路FPGA部分,由HPS的TDI端口流入的数据直接作用在HPS上,对HPS的相应的寄存器进行读写,结果数据从HPS的TDO端口流出,再流入FPGA的TDI端口,由于此时FPGA的JTAG功能处于旁路状态,TDI端口流入的数据会直接由FPGA的TDO端口流出,进入USB Blaster的TDI端口,完成对HPS的调试。

浙公网安备 33010602011771号

浙公网安备 33010602011771号