基于FPGA设计10进制加法计数器

实验一,计数器的设计

环境:Quartus Prime 17.1 Standard Edition

FPGA型号为:Cylone 10 10CL55WF484C8

- 程序设计

`

--10进制加法计数器的VHDL程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT5 IS

PORT ( CLK,RST : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );

END CNT5;

ARCHITECTURE DACC OF CNT5 IS

SIGNAL Q : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

PROCESS(CLK,RST )

BEGIN

IF RST = '0' THEN Q<="0000";

ELSIF CLK'EVENT AND CLK = '1' THEN

IF Q<9 THEN Q<=Q+1; --计数小于9,继续累加

ELSE Q <=(OTHERS=>'0'); --否则计数回1

END IF;

END IF;

END PROCESS;

DOUT<=Q ;

END;

`

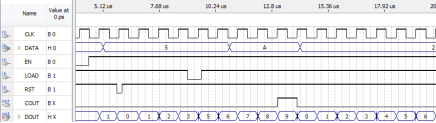

2.仿真结果

__EOF__

本文作者:xiaohu

本文链接:https://www.cnblogs.com/xiaohuzaixue/p/17331819.html

关于博主:评论和私信会在第一时间回复。或者直接私信我。

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

声援博主:如果您觉得文章对您有帮助,可以点击文章右下角【推荐】一下。您的鼓励是博主的最大动力!

本文链接:https://www.cnblogs.com/xiaohuzaixue/p/17331819.html

关于博主:评论和私信会在第一时间回复。或者直接私信我。

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

声援博主:如果您觉得文章对您有帮助,可以点击文章右下角【推荐】一下。您的鼓励是博主的最大动力!

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 提示词工程——AI应用必不可少的技术

· 地球OL攻略 —— 某应届生求职总结

· 字符编码:从基础到乱码解决

· SpringCloud带你走进微服务的世界