Jvm和CPU保证特定情况下不乱序

简介

CPU为了提高指令执行效率,会在一条指令执行过程中(比去内存读数据(慢100倍)),去同时执行另一条指令,前提是,两条指令没有依赖关系。

CPU保证不乱序

MESI--CPU缓存一致性协议(Inter的CPU)

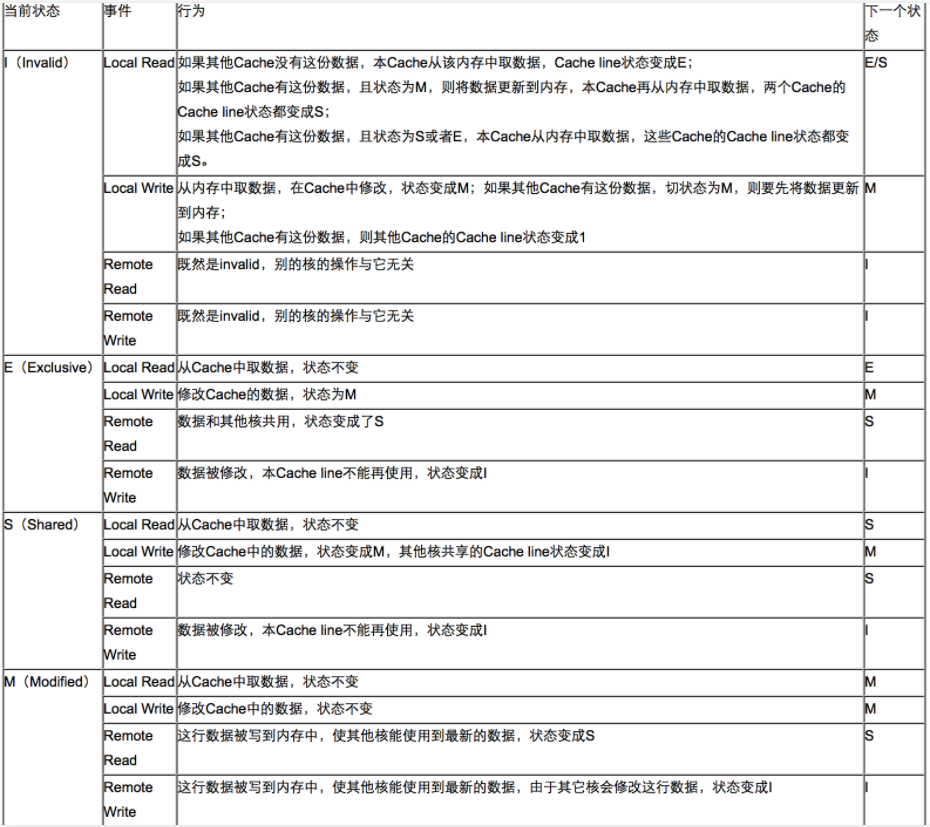

概念

- Modified(被修改)

该缓存行只被缓存在该CPU的缓存中,并且是被修改过的(dirty),即与主存中的数据不一致,该缓存行中的内存需要在未来的某个时间点(允许其它CPU读取请主存中相应内存之前)写回(write back)主存。

当被写回主存之后,该缓存行的状态会变成独享(exclusive)状态。 - Exclusive(独享的)

该缓存行只被缓存在该CPU的缓存中,它是未被修改过的(clean),与主存中数据一致。该状态可以在任何时刻当有其它CPU读取该内存时变成共享状态(shared)。

同样地,当CPU修改该缓存行中内容时,该状态可以变成Modified状态。 - Shared(共享的)

该状态意味着该缓存行可能被多个CPU缓存,并且各个缓存中的数据与主存数据一致(clean),当有一个CPU修改该缓存行中,其它CPU中该缓存行可以被作废(变成无效状态(Invalid))。 - Invalid(无效的)

该缓存是无效的(可能有其它CPU修改了该缓存行)。

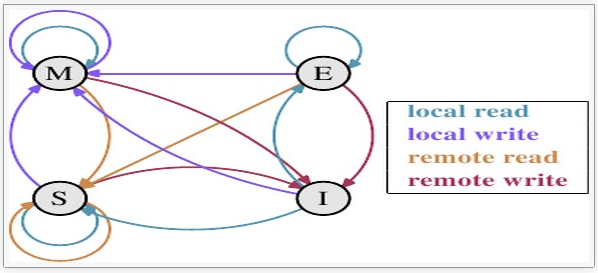

MESI状态转换图

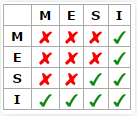

状态之间的相互转换关系也可以使用下表进行表示。

Jvm

- sfence(store)

在sfence指令前的写操作当必须在 sfence指令后的写操作前完成。 - lfence(load)

在lfence指令前的读操作当必须在 lfence指令后的读操作前完成。 - mfence(modify/mix)

在mfence指令前的读写操作当必须在 mfence指令后的读写操作前完成。

列子

- Load1; LoadLoad; Load2

在Load2及后续读取操作要读取的数据被访问前,保证Load1要读取的数据被读取完毕。 - Store1; StoreStore; Store2

在Store2及后续写入操作执行前,保证Store1的写入操作对其它处理器可见。 - Load1; LoadStore; Store2

在Store2及后续写入操作被刷出前,保证Load1要读取的数据被读取完毕。 - Store1; StoreLoad; Load2

在Load2及后续所有读取操作执行前,保证Store1的写入对所有处理器可见。

参考

XFS

分类:

JVM调优

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· 开发者必知的日志记录最佳实践

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· AI 智能体引爆开源社区「GitHub 热点速览」

· 从HTTP原因短语缺失研究HTTP/2和HTTP/3的设计差异

· 三行代码完成国际化适配,妙~啊~