计算机组成原理之组成篇

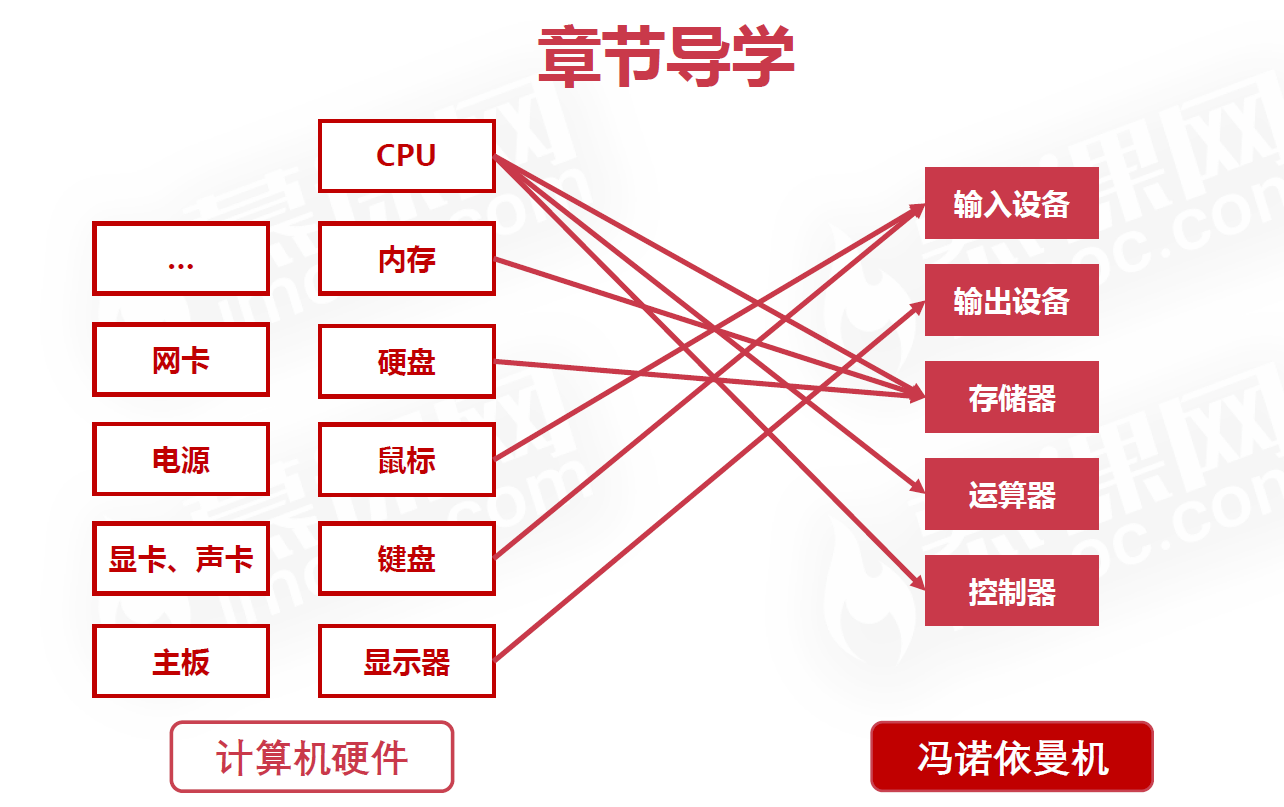

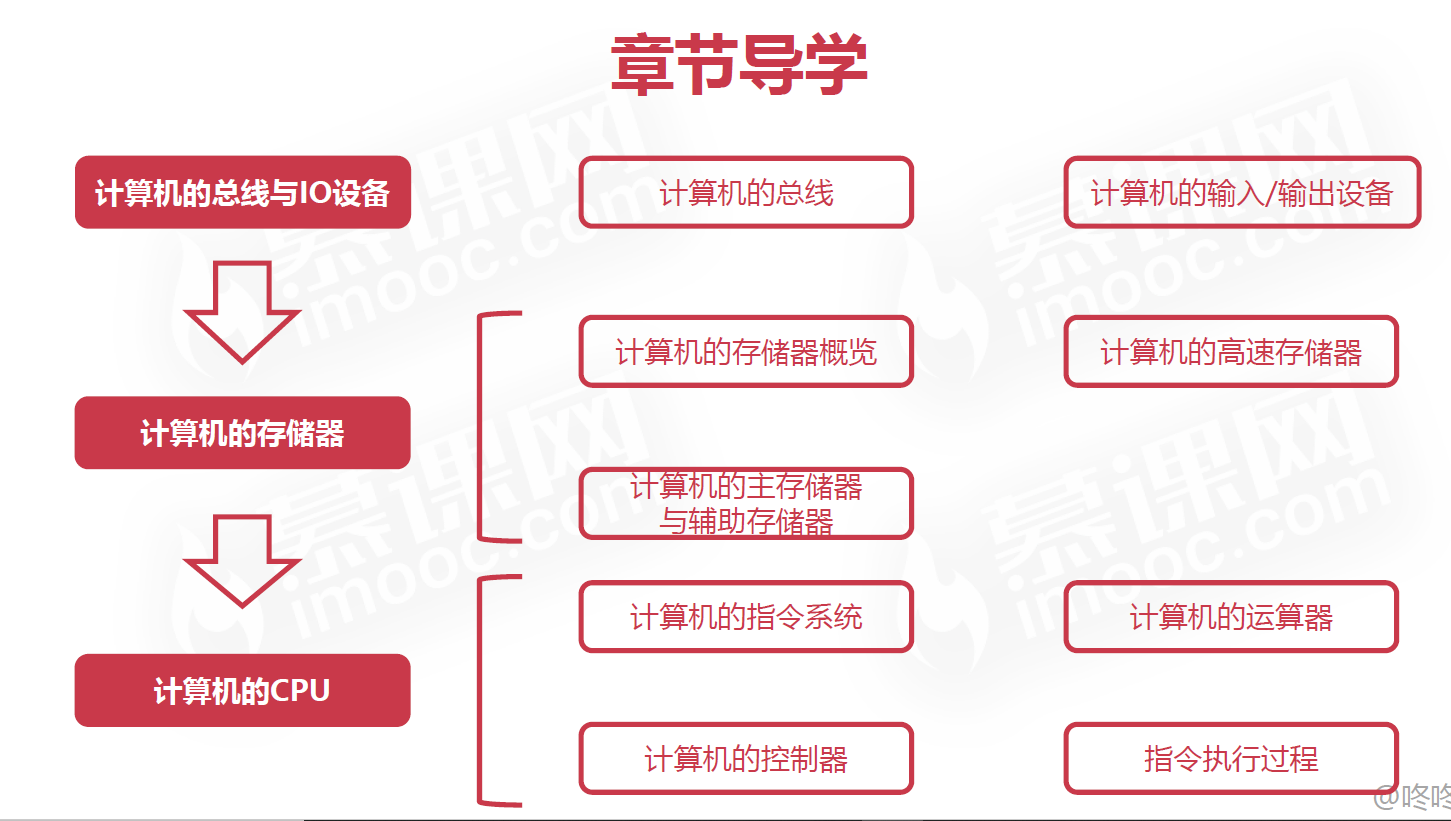

章节导学

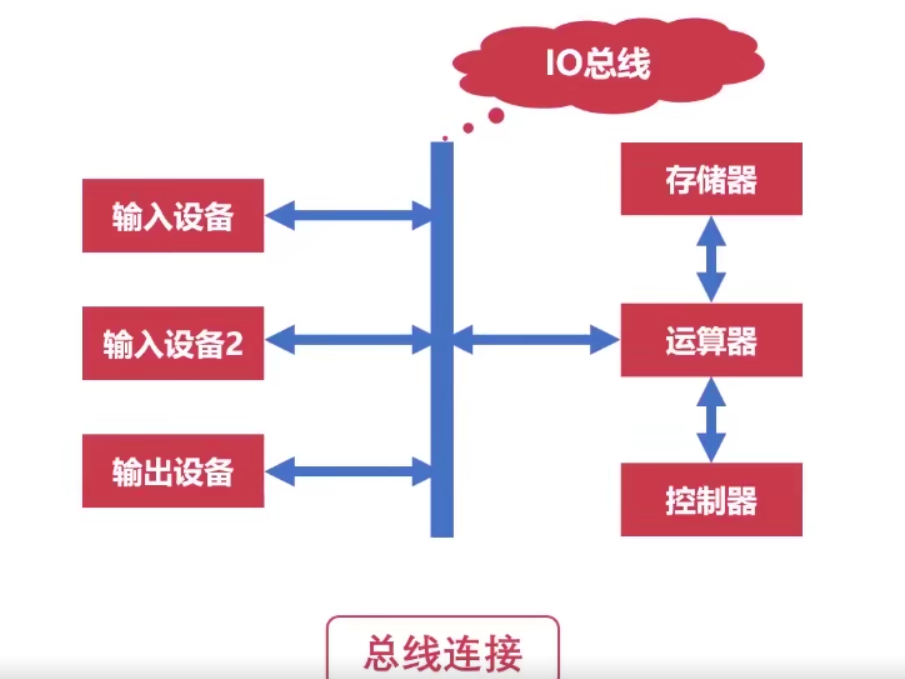

计算机的总线 连接各个设备的一条数据线

计算机的总线

- 总线的概述

- 总线的仲裁

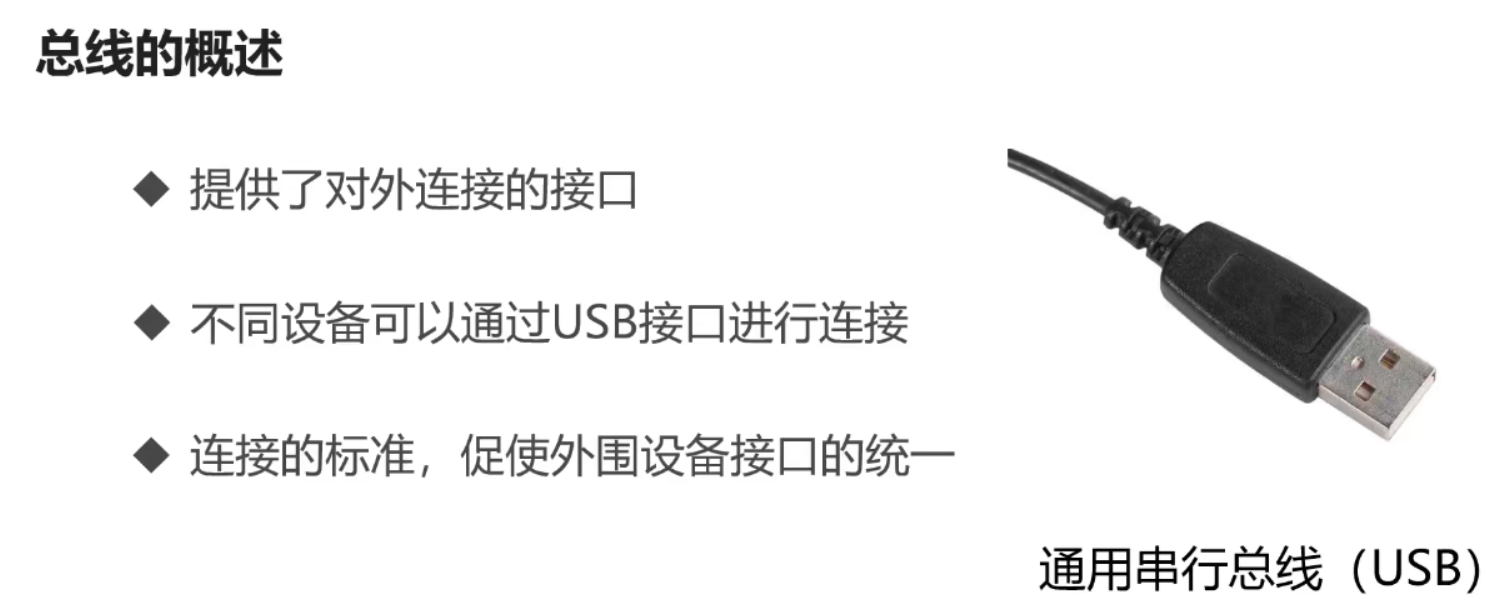

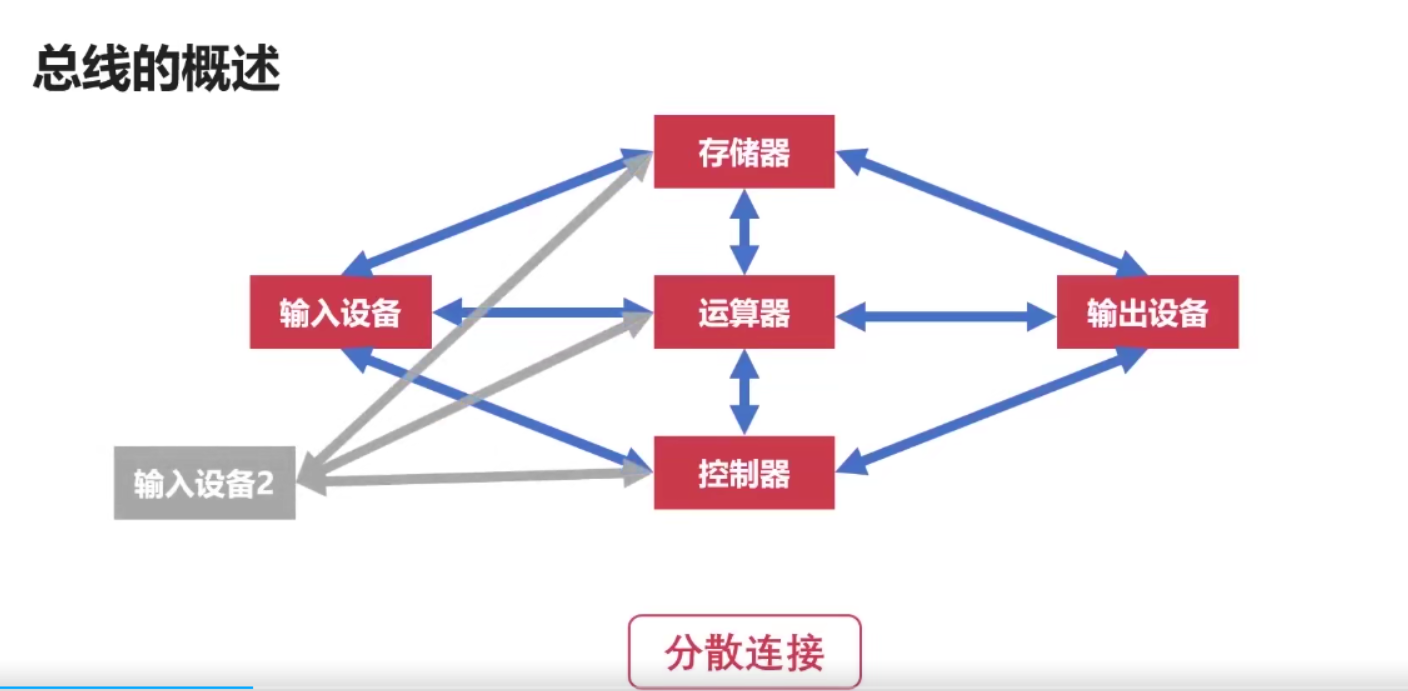

总线的概述

- 总线的概述(是什么、什么用)

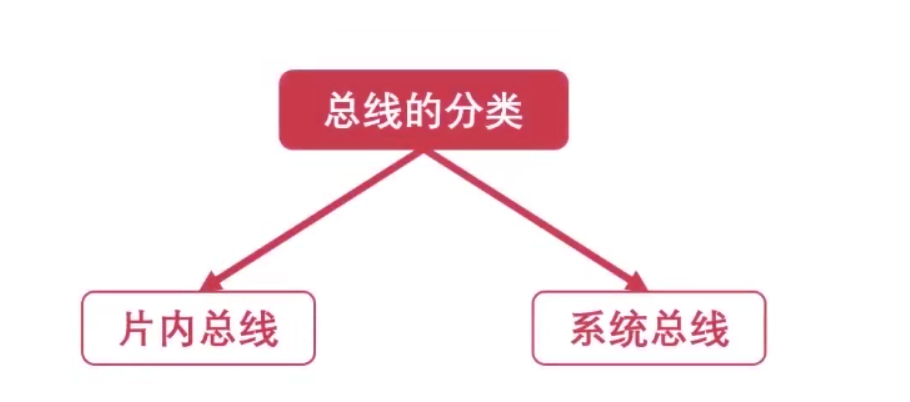

- 总线的分类

总线的概述

通用串行总线

总线的分类

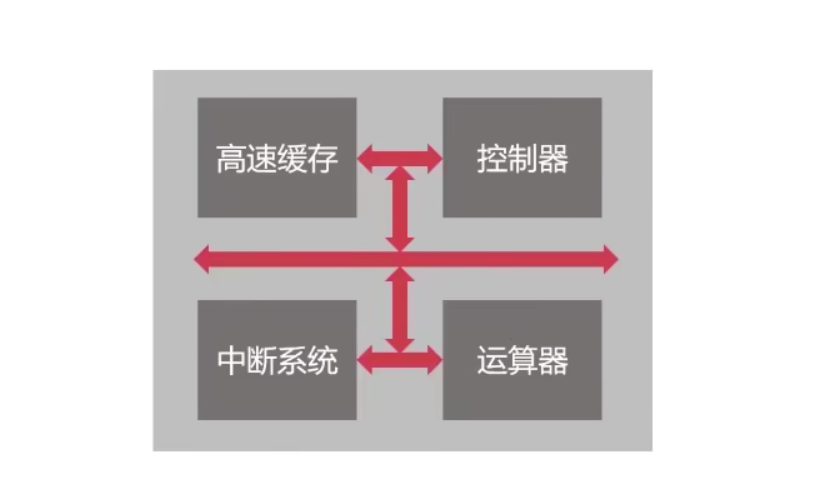

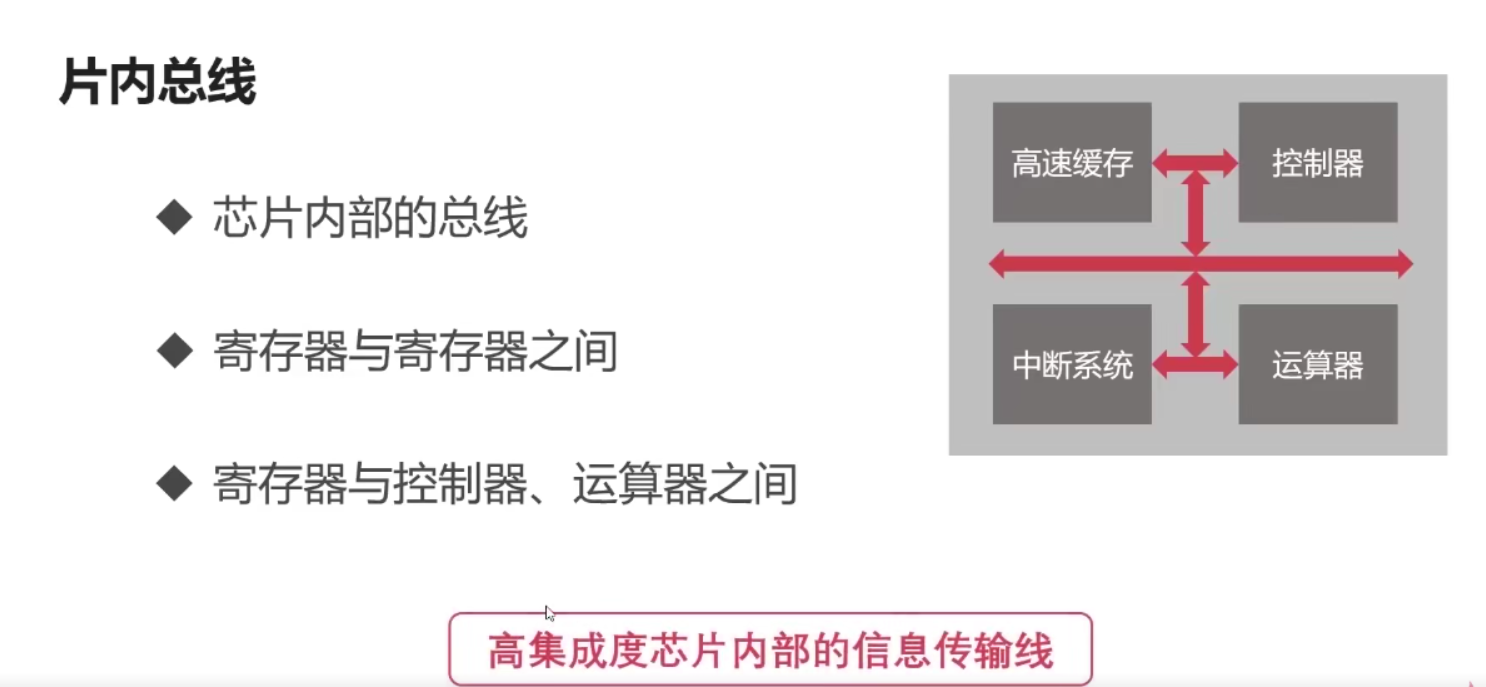

片内总线

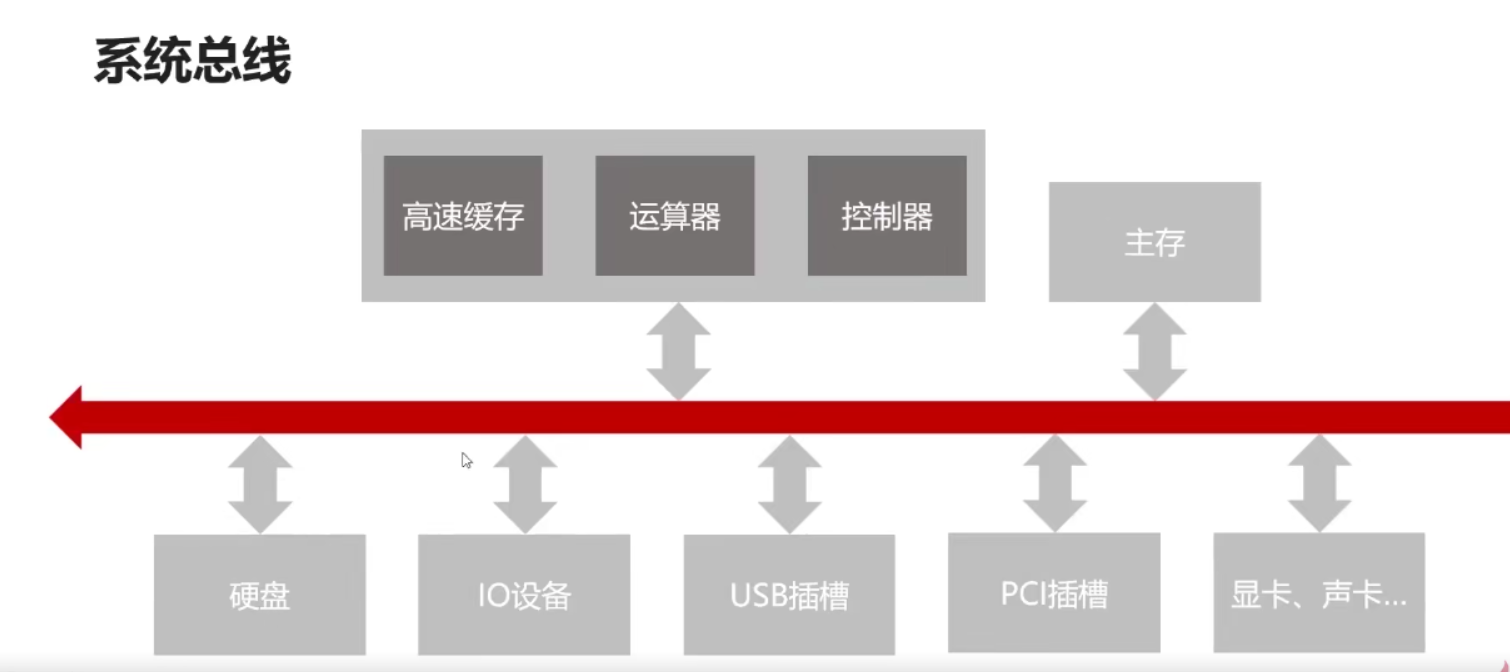

系统总线

、

、

数据总线

- 双向传输各个部件的数据信息

- 数据总线的位数(总线宽度)是数据总线的重要参数

- 一般与CPU位数相同(32位、64位)

地址总线

- 指定源数据或目的数据在内存中的地址

- 地址总线的位数与存储单元有关

地址总线位数=n,寻址范围:0~2n

控制总线

- 控制总线是用来发出各种控制信号的传输线

- 控制信号经由控制总线从一个组件发给另外一个组件

- 控制总线可以监视不同组件之间的状态(就绪/未就绪)

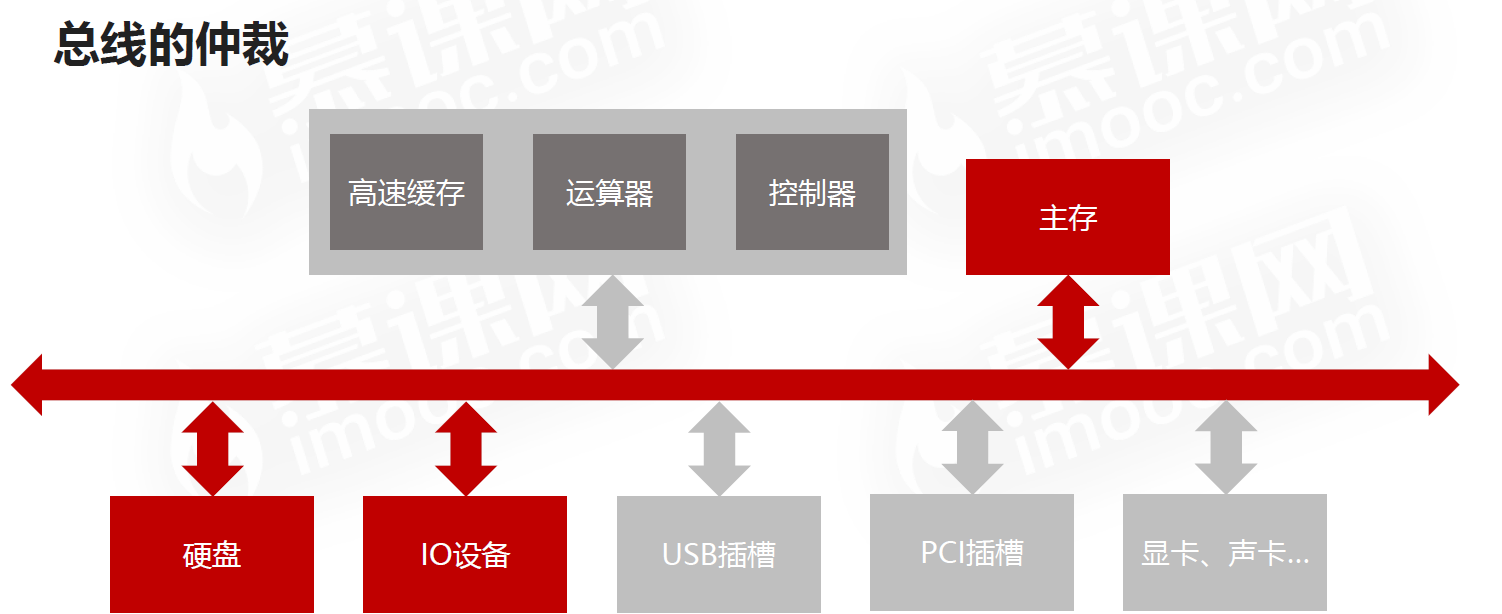

总线的仲裁

- 为什么需要总线仲裁

- 总线仲裁的方法

为什么需要总线仲裁

我们之所以需要总线仲裁,是为了解决总线使用权的冲突问题

总线仲裁的方法

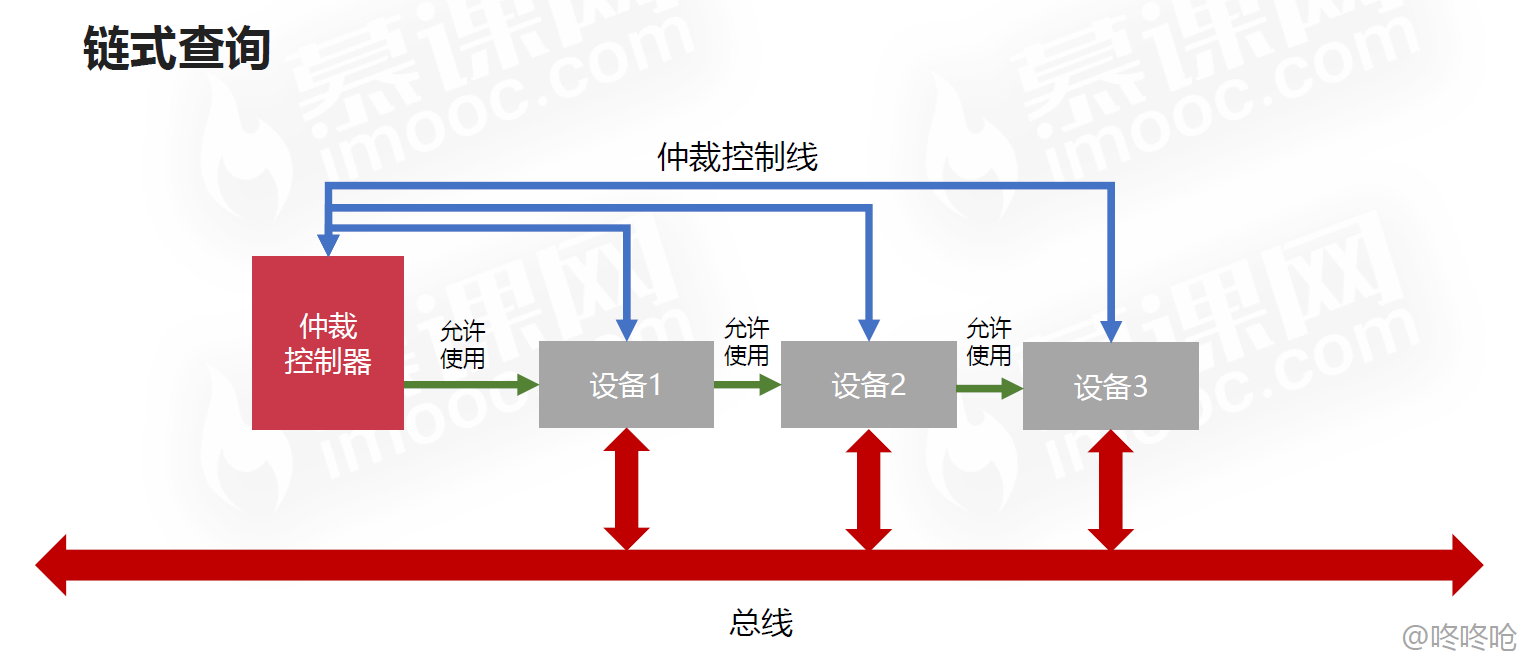

- 链式查询

- 计时器定时查询

- 独立请求

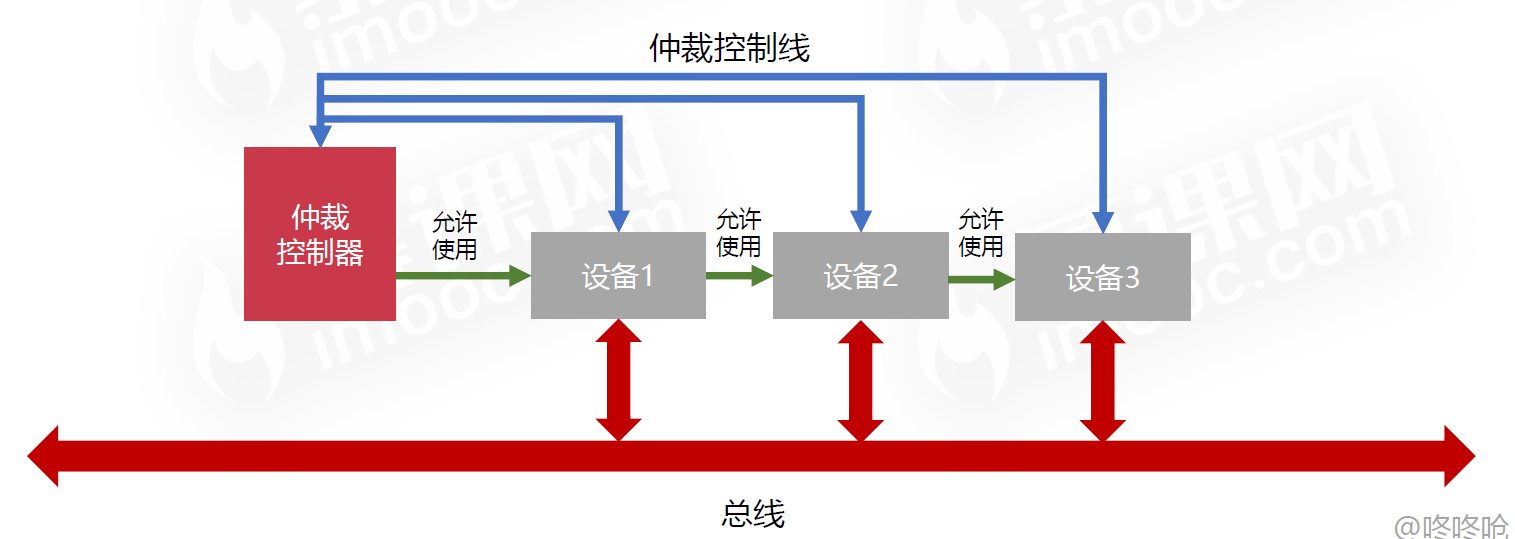

链式查询

如果这里我们的设备3想要拿到总线的使用权,那么在链式查询下,我们通过仲裁控制线,首先询问设备1是否使用,如果是的话,那么设备1占用总线使用权,以此类推

链式查询

- 好处:电路复杂度低,仲裁方式简单

- 坏处:优先级低的设备难以获得总线使用权

- 坏处:对电路故障敏感 (串联0

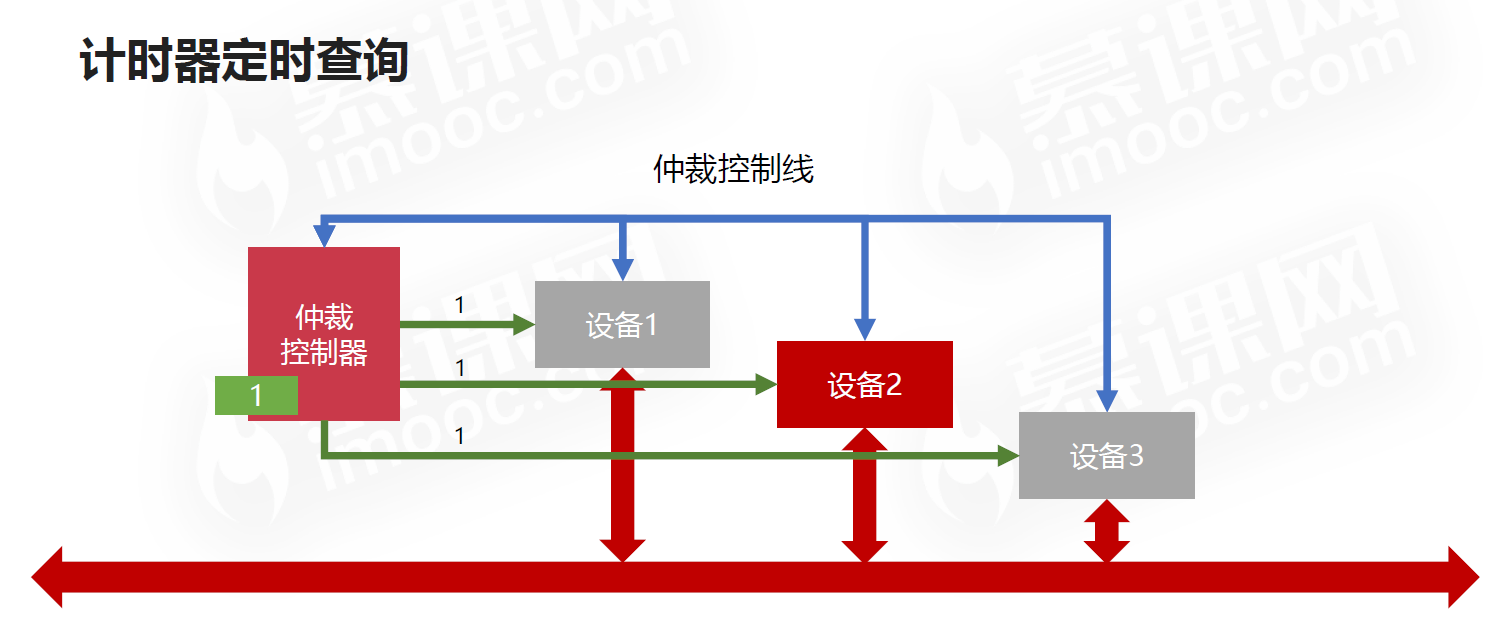

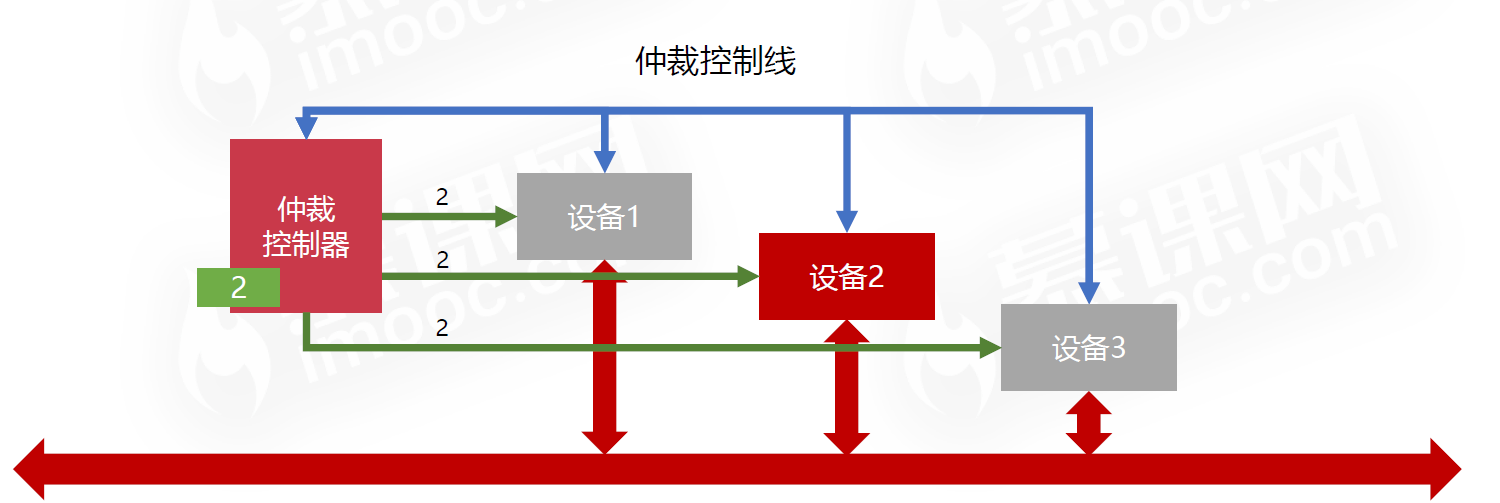

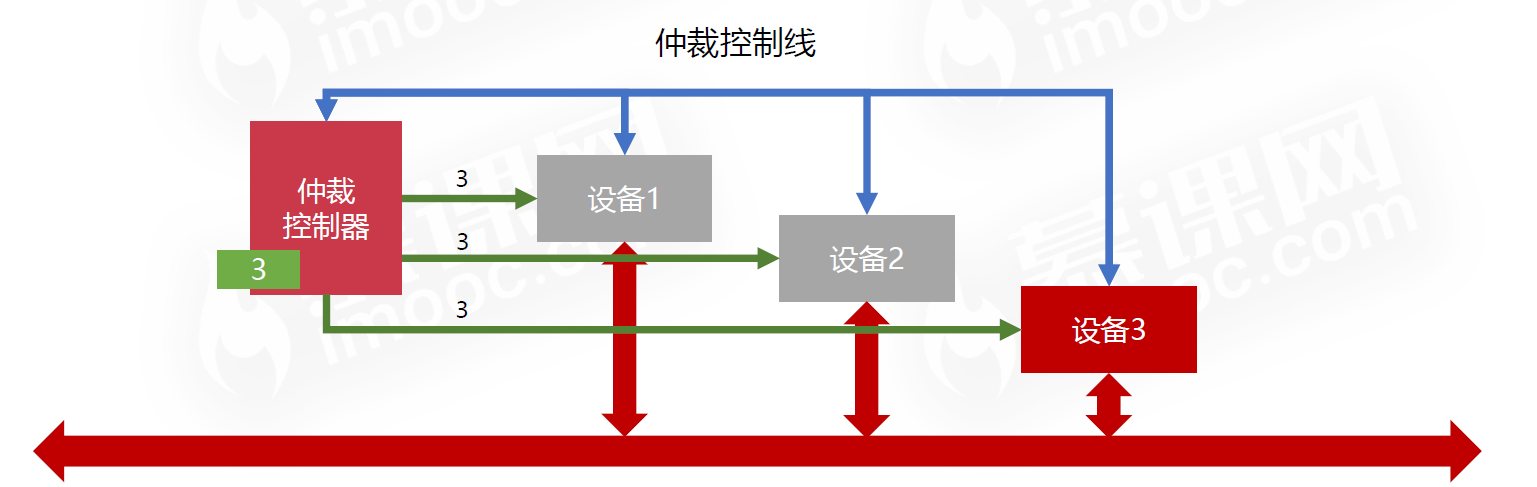

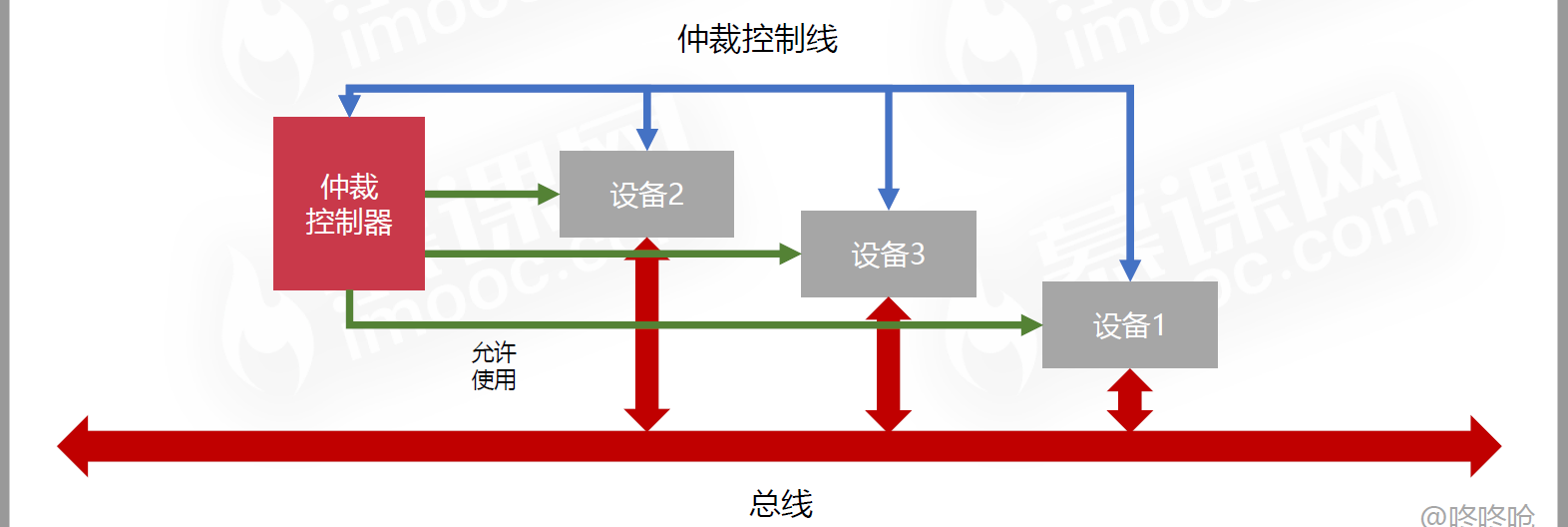

计时器定时查询

- 仲裁控制器对设备编号并使用计数器累计技术

- 接收到仲裁信号后,往所有设备发出计数值

- 计数值与设备编号一致则获得总线使用权

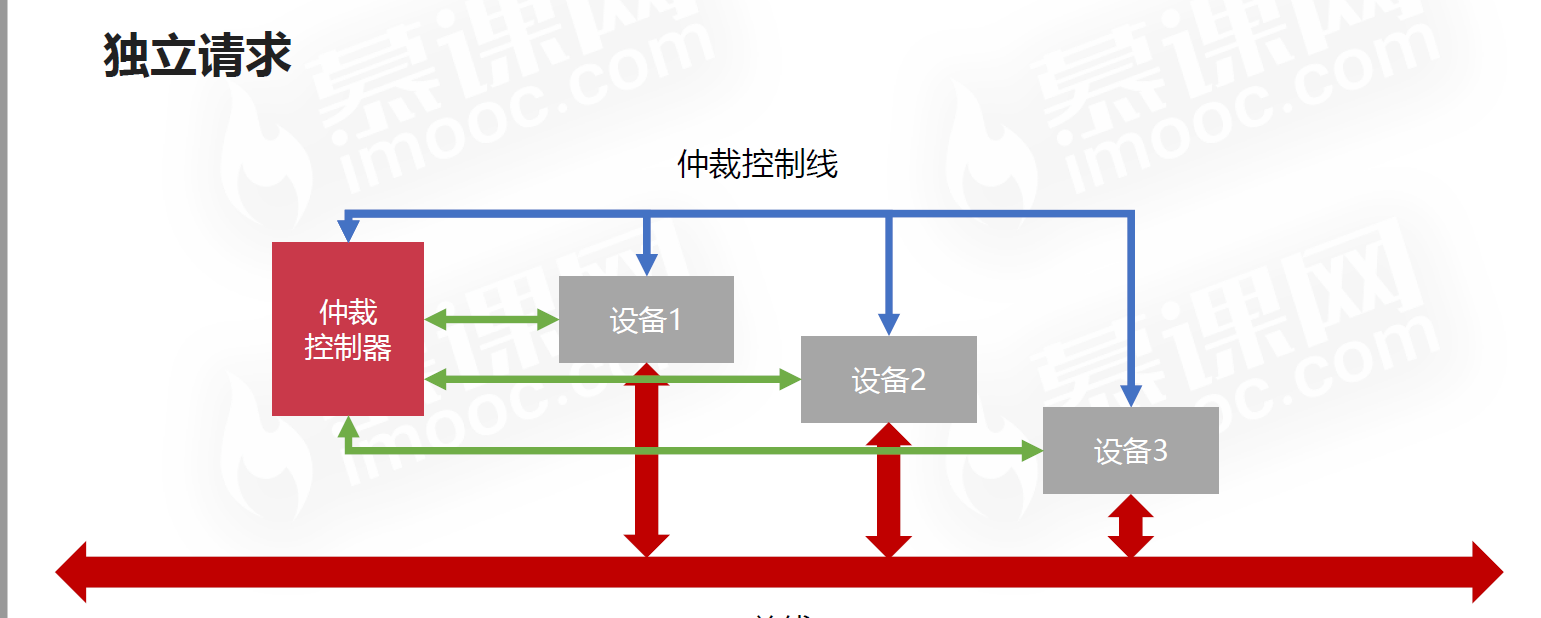

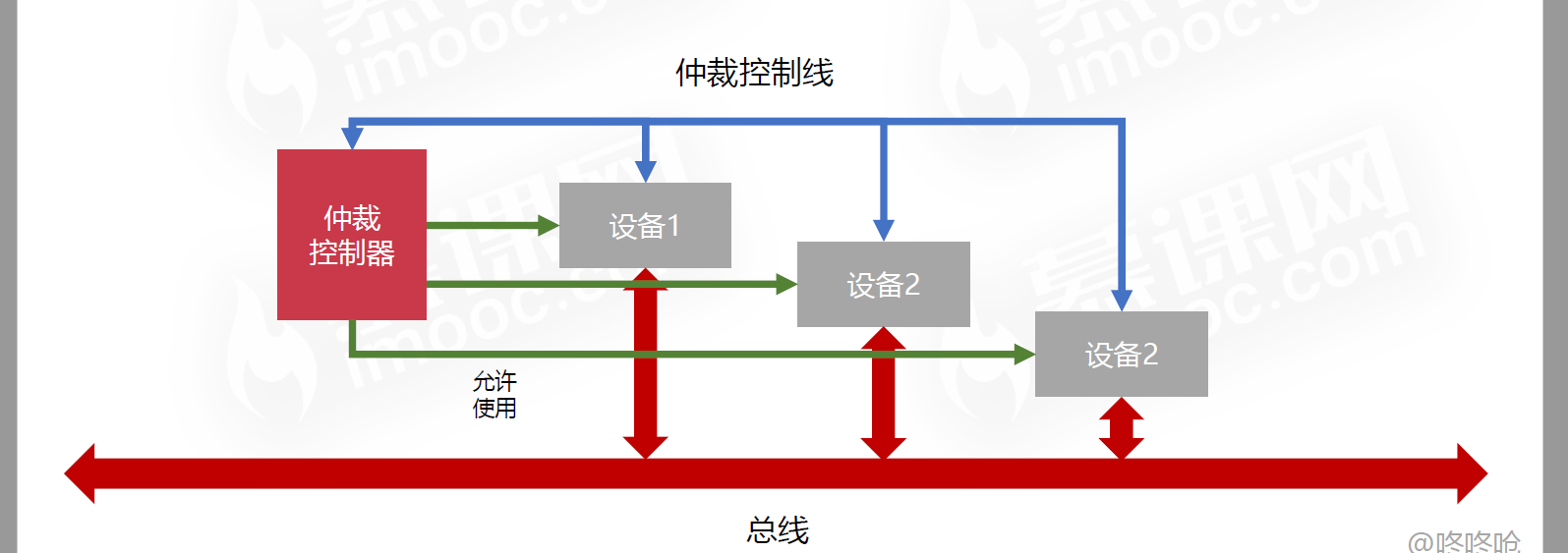

独立请求

- 每个设备均有总线独立连接仲裁器

- 设备可单独向仲裁器发送请求和接收请求

- 当同时受到多个请求信号,仲裁器有权按优先级分配使用权

独立请求

- 好处:响应速度快,优先顺序可动态改变

- 设备连线多,总线控制复杂

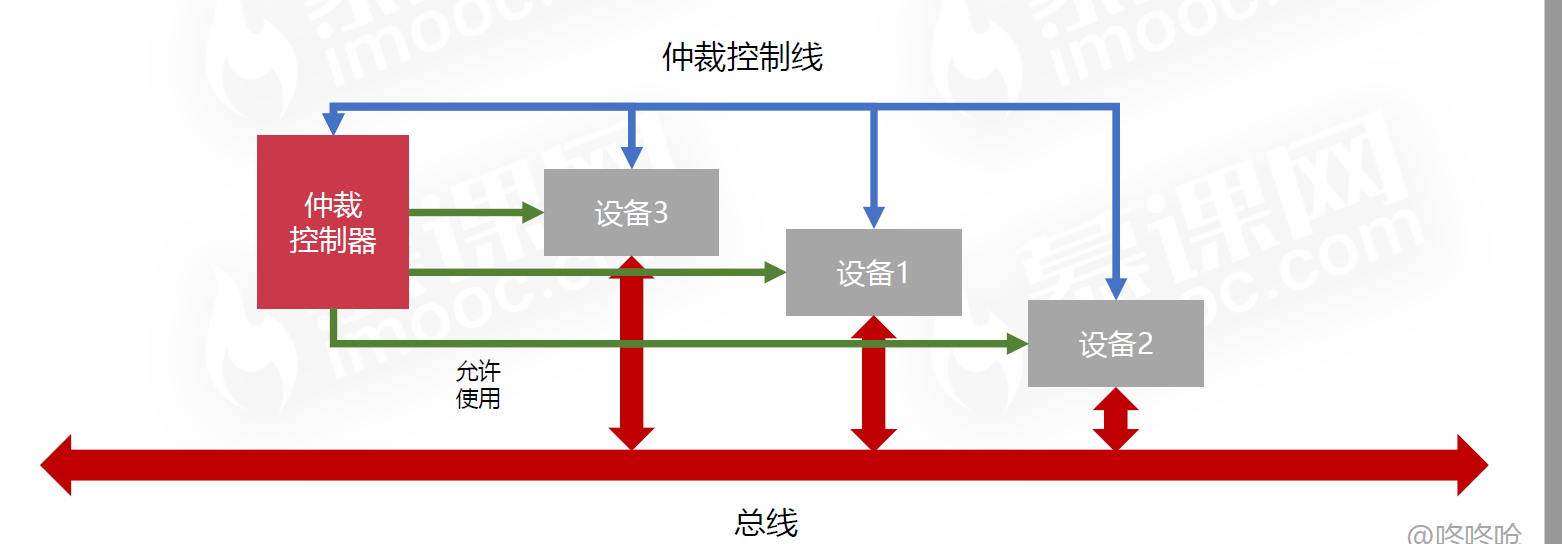

串联优先级判别

- 优先级高的设备经常得到总线使用权限

- 优先级低的设备长时间无法得到总线

并联优先级判别

- 优先级高的设备经常得到总线使用权向

- 优先级低的设备长时间无法得到总线

循环优先级判别

计算机的输入输出设备

- 常见的输入输出设备

- 输入输出接口的通用设计

- CPU与IO设备的通信

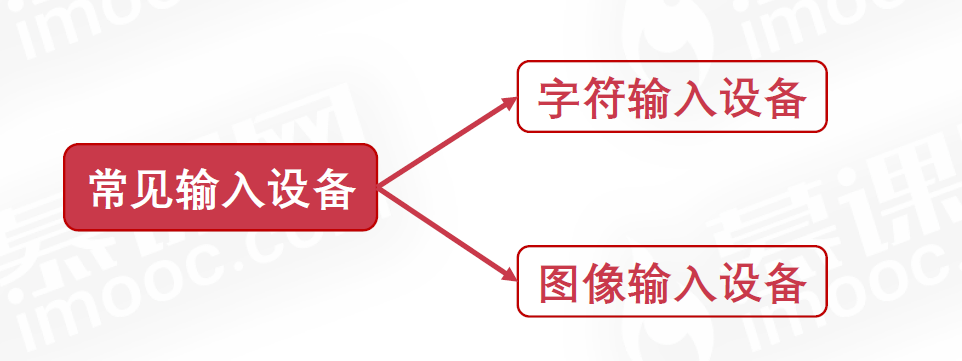

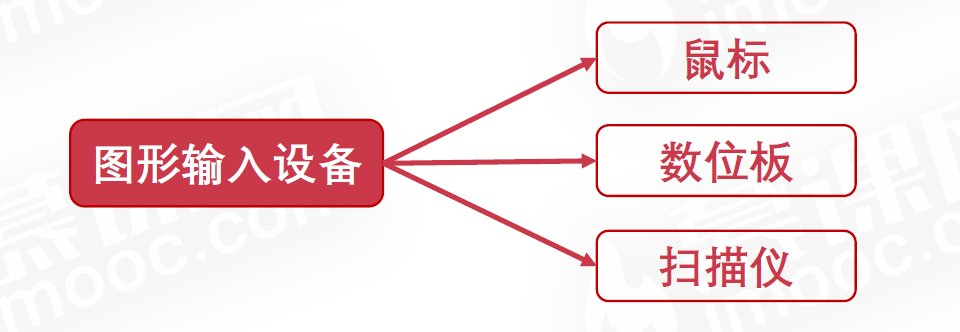

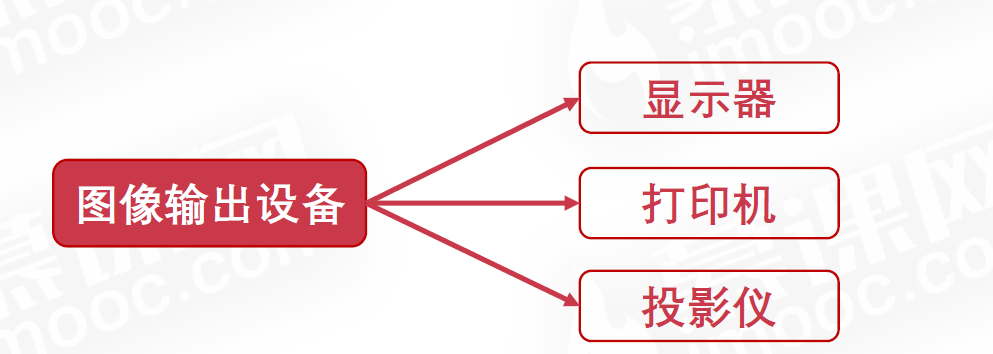

常见的输入输出设备

输入输出接口的通用设计

- 数据线

- 状态线

- 命令线

- 设备选择线

数据线

- 是I/O设备与主机之间进行数据交换的传送线

- 单向传输数据线

- 双向传输数据线

状态线

- IO设备状态向主机报告的信号线

- 查询设备是否已经正常连接并就绪

- 查询设备是否已经被占用

命令线

- CPU向设备发送命令的信号线

- 发送读写信号

- 发送启动停止信号

设备选择线

- 主机选择I/O设备进行操作的信号线

- 对连在总线上的设备进行选择

CPU与IO设备的通信

- 程序中断

- DMA(直接存储器访问)

CPU速度与IO设备速度不一致。

程序中断

- 当外围IO设备就绪时,向CPU发出中断信号

- CPU有专门的电路响应中断信号

提供低速设备通知CPU的一种异步的方式

CPU可以高速运转同时兼顾低速设备的响应。

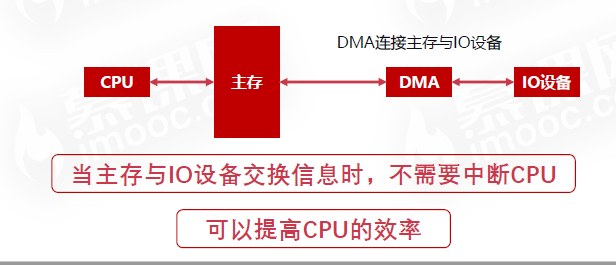

DMA

DMA(直接存储器访问)

- 硬盘

- 外置显卡

计算机存储器概览

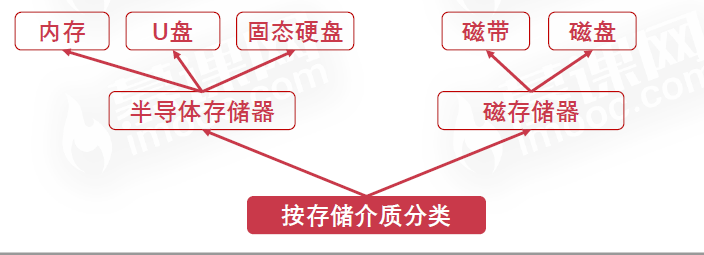

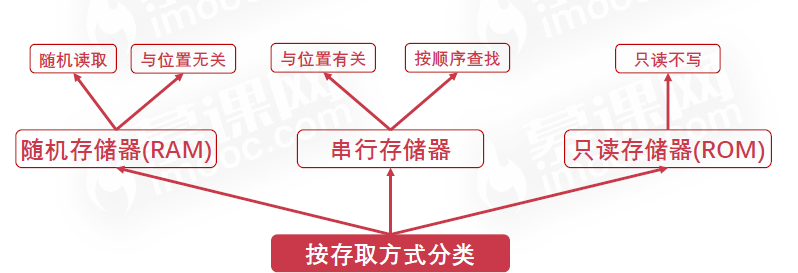

- 存储器的分类

- 存储器的层次结构

存储器的分类

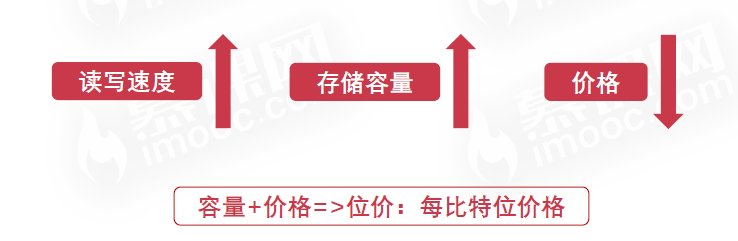

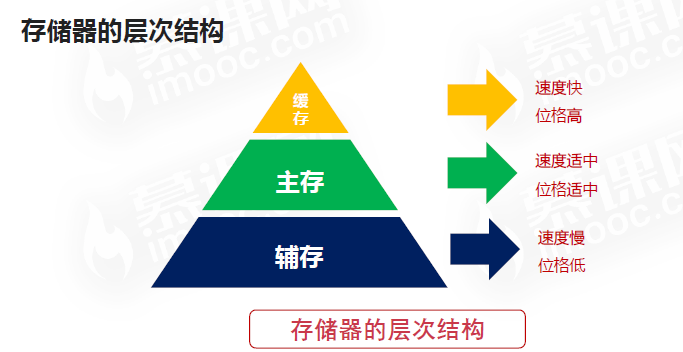

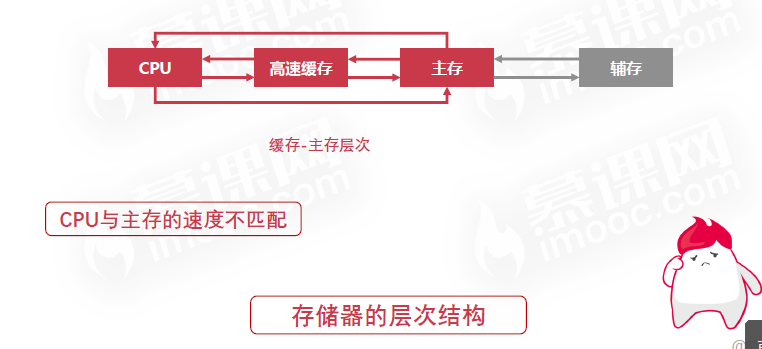

存储器的层次结构

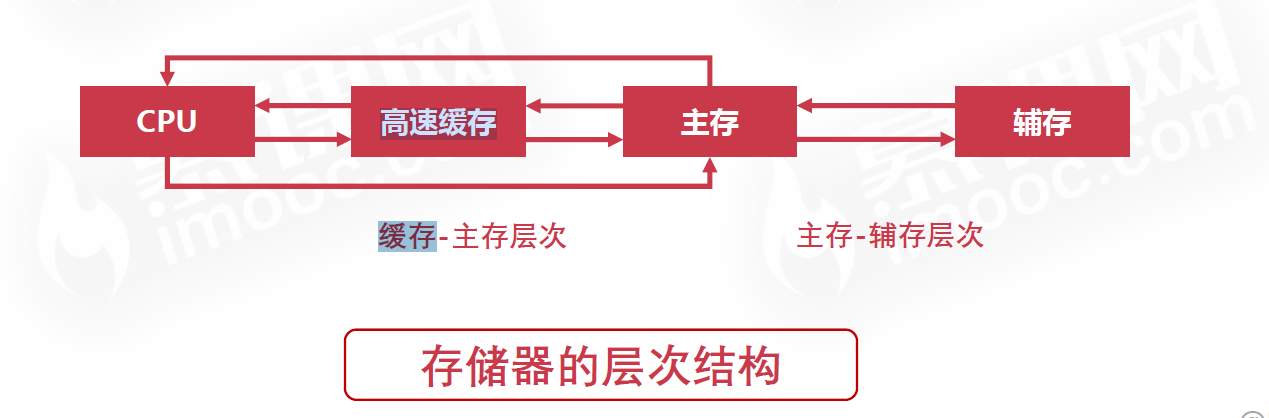

存储器的层次结构

- 原理:局部性原理

- 实现:在CPU与主存之间增加一层速度快(容量小)的cache

- 目的:解决主存速度不足的问题

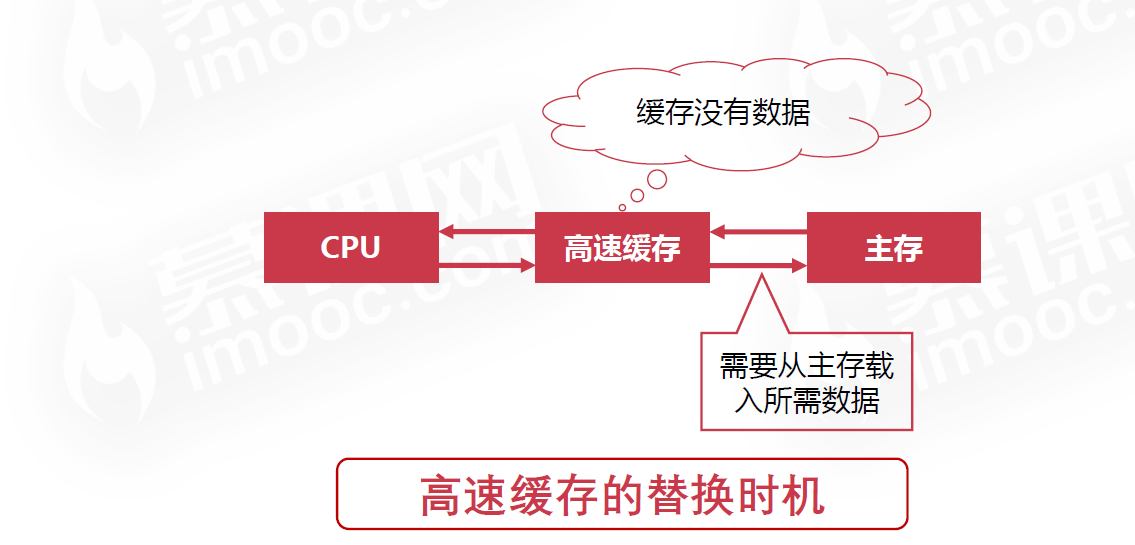

缓存-主存层次

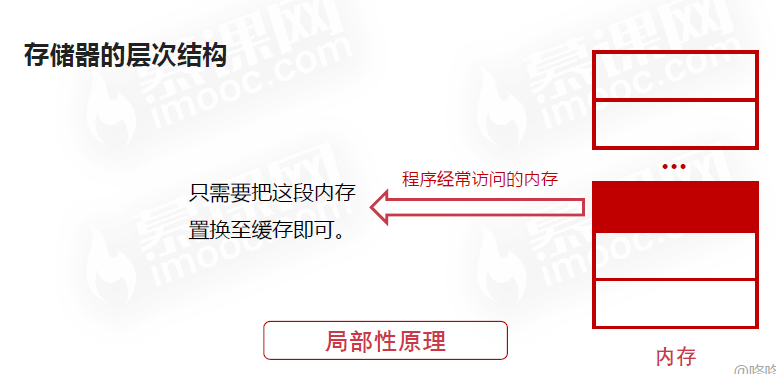

局部性原理是指CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中;

局部性原理

计算机的主存储器与辅助存储器

- 计算机断电,内存数据丢失

- 计算机断电,磁盘数据不会丢失。

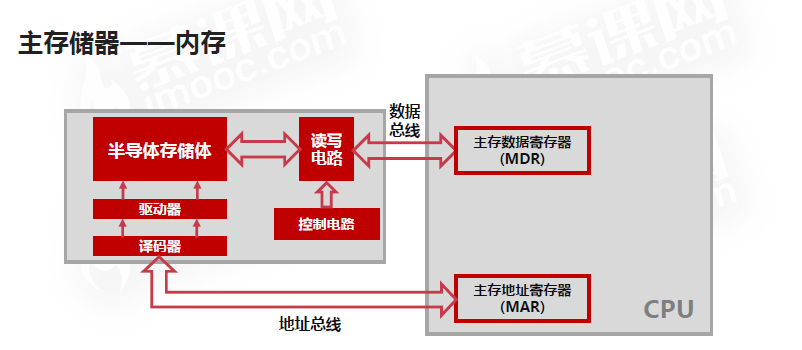

主存储器-内存

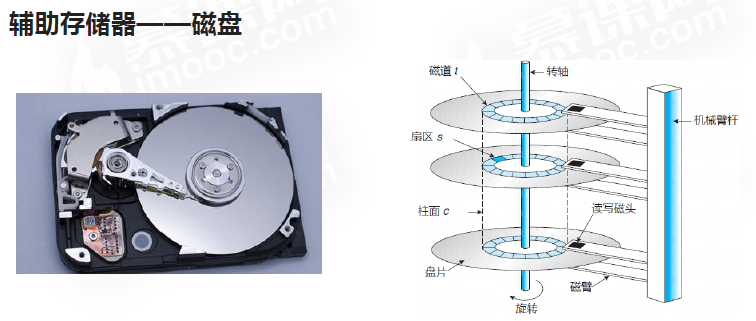

辅助存储器-磁盘

计算机的主存储器与辅助存储器

主存储器

主存储器--内存

- RAM(随机存取存储器:Random Access Memory)

- RAM通过电容存储数据,必须隔一段时间刷新一次

- 如果掉电,那么一段时间后将丢失所有数据

主存地址寄存器,32位系统与64位系统差别是地址总线寻址能力不同

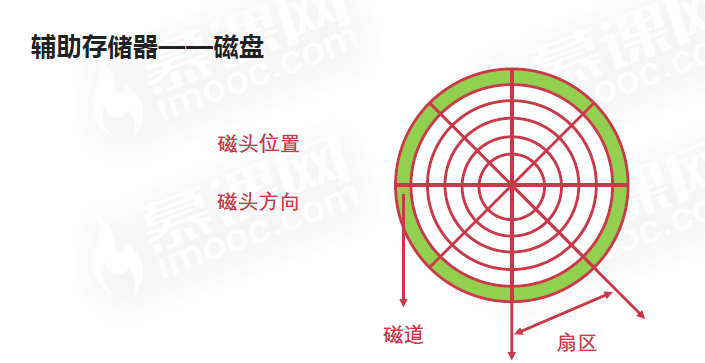

辅助存储器-磁盘

辅助存储器

- 表面是可磁化的硬磁特性材料

- 移动磁头经向运动读取磁道信息

辅导存储器-磁盘

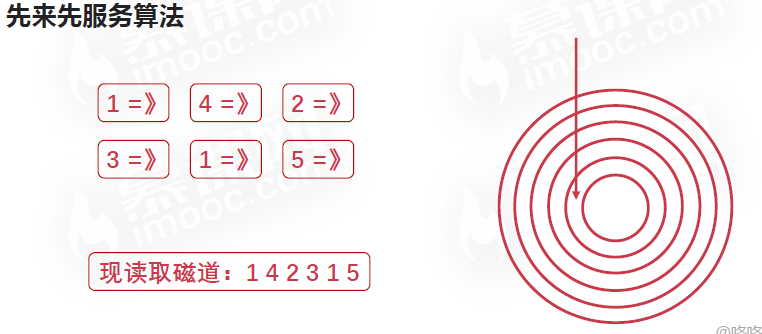

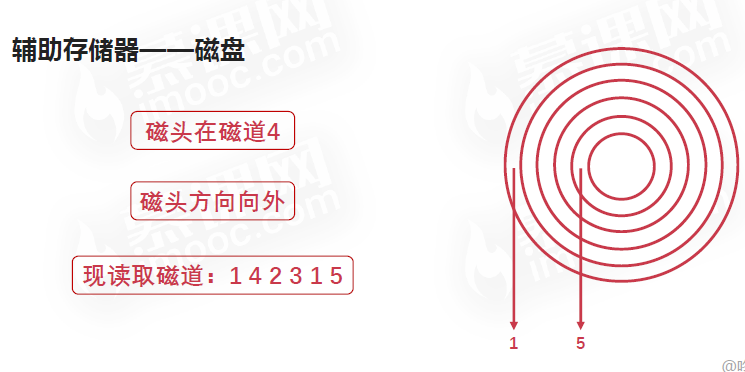

- 先来先服务算法

- 最短寻道时间优先

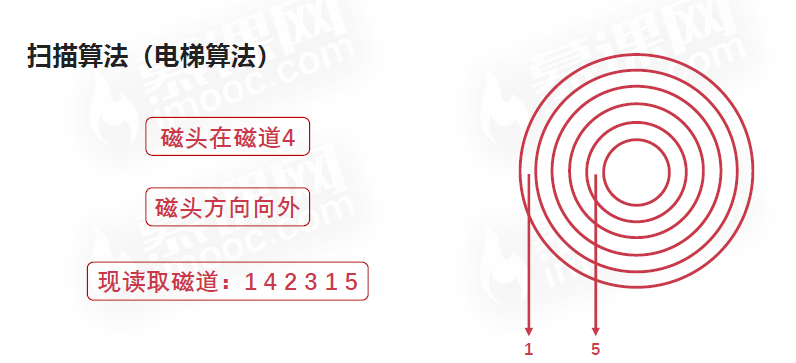

- 扫描算法(电梯算法)

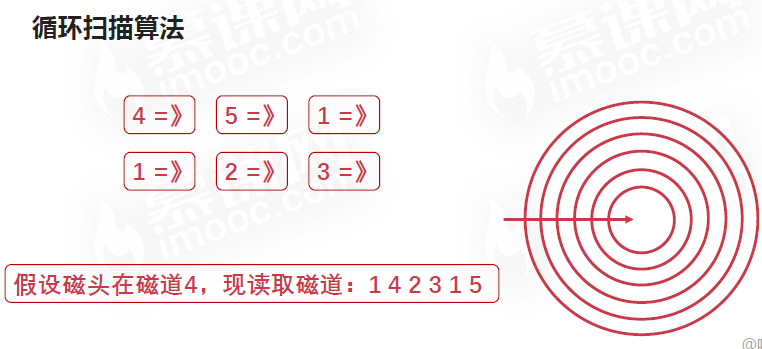

- 循环扫描算法

先来先服务算法

- 按顺序访问进程的磁道读写需求

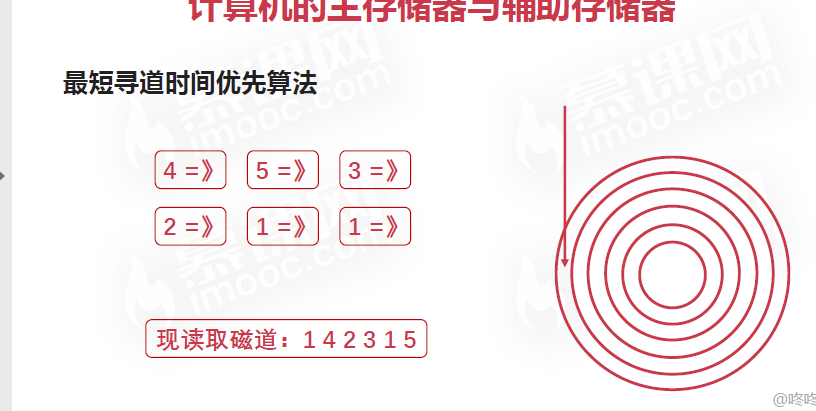

最短寻道时间优先算法

- 与磁头当前位置有关

- 优先访问离磁头最近的磁道

扫描算法(电梯算法)

- 每次只往一个方向移动

- 到达一个方向需要服务的尽头再反方向移动

扫描算法(电梯算法)

循环扫描算法

循环扫描算法,只能由外往内,或者说是由内往外进行读取

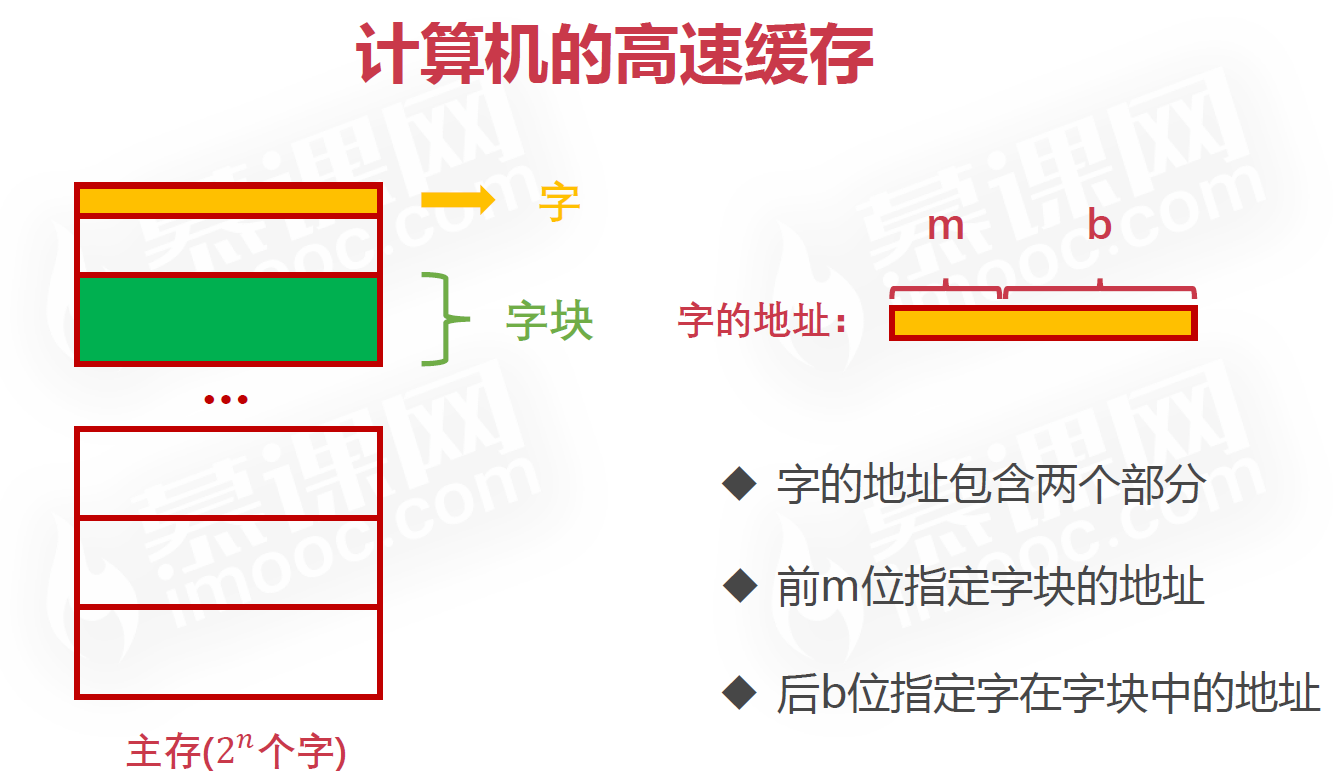

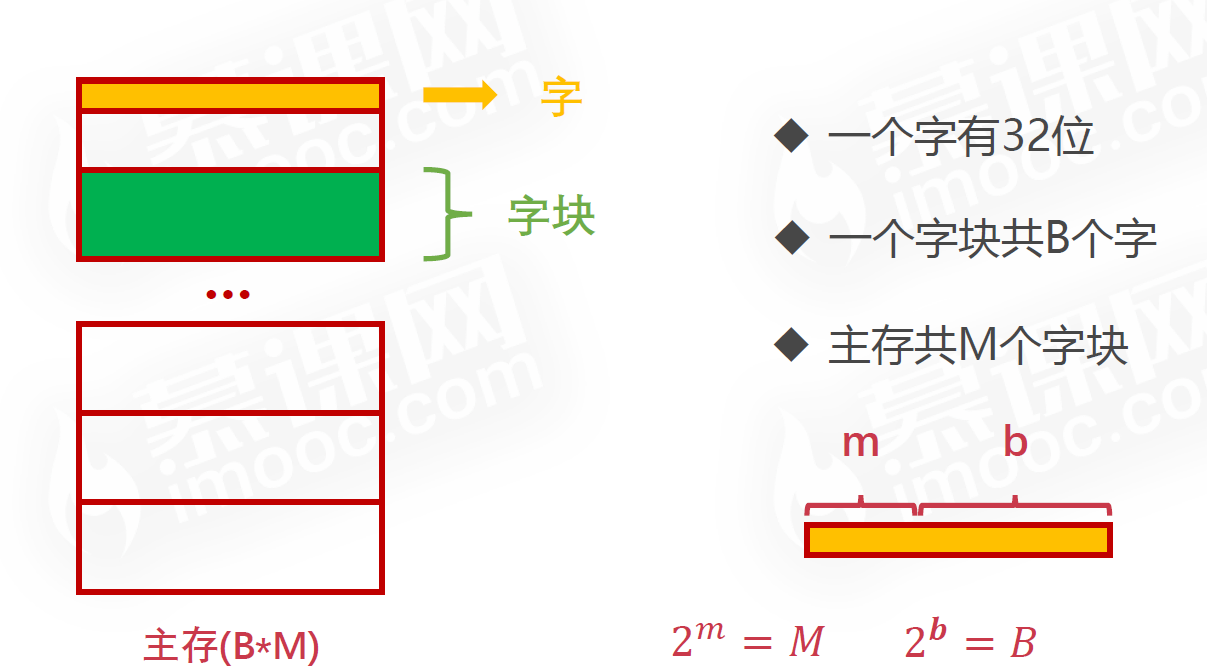

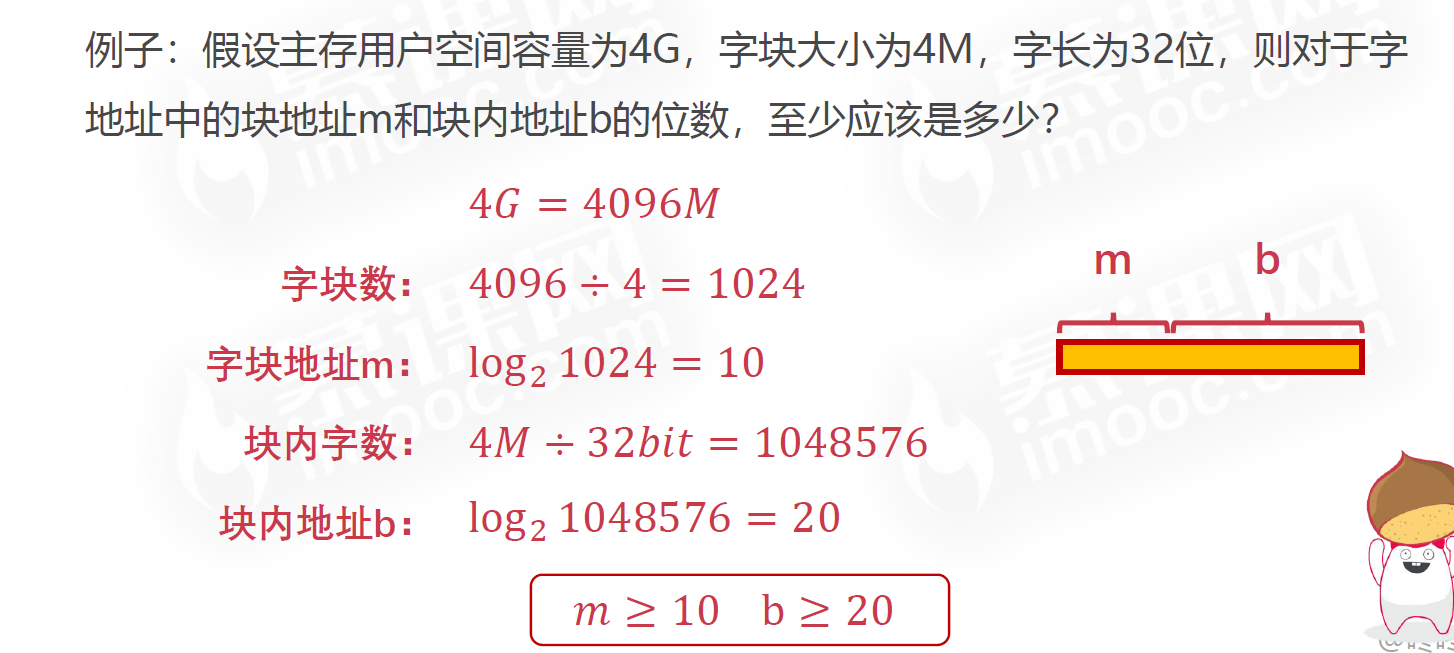

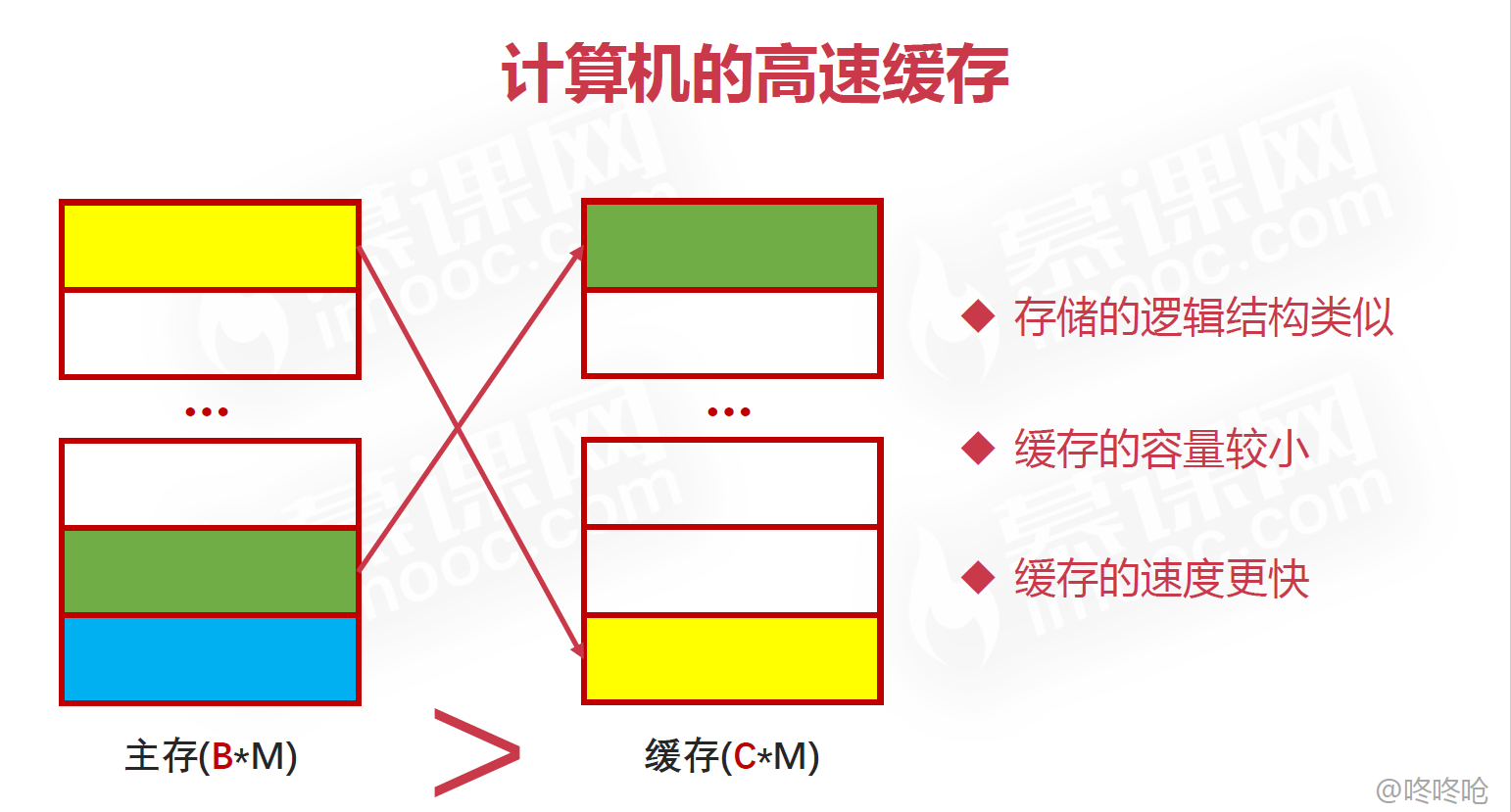

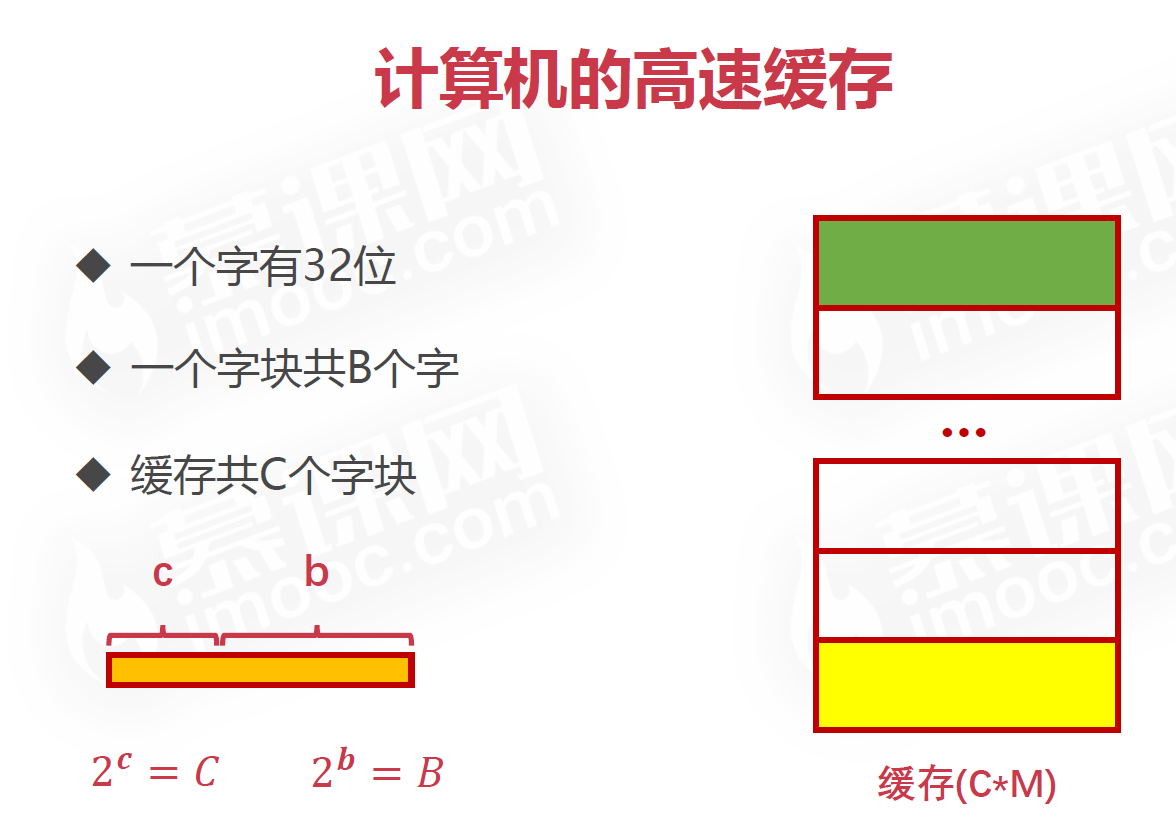

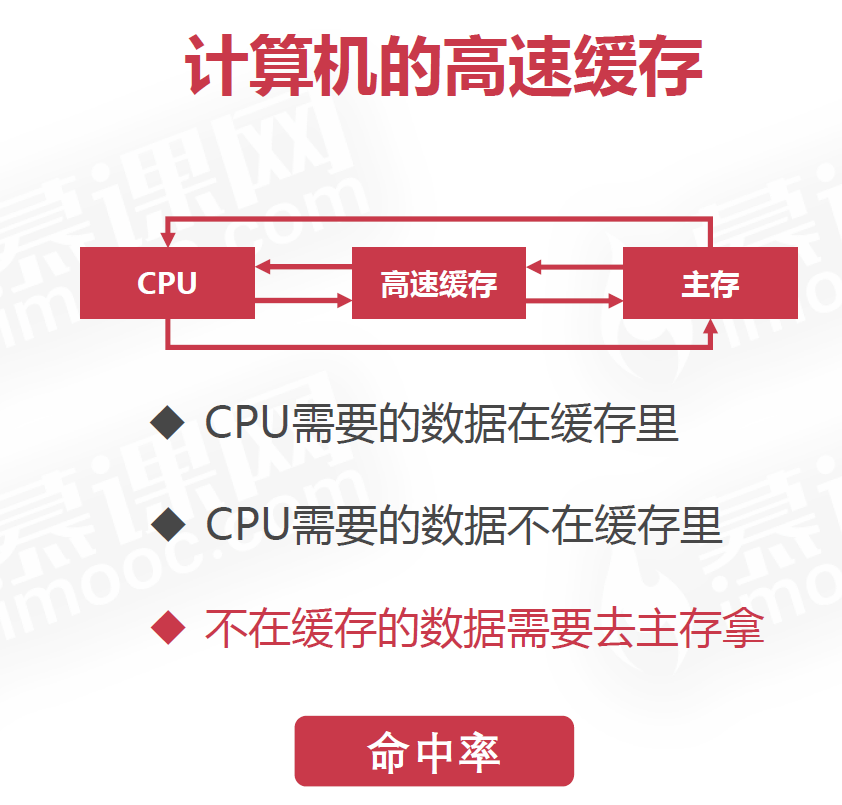

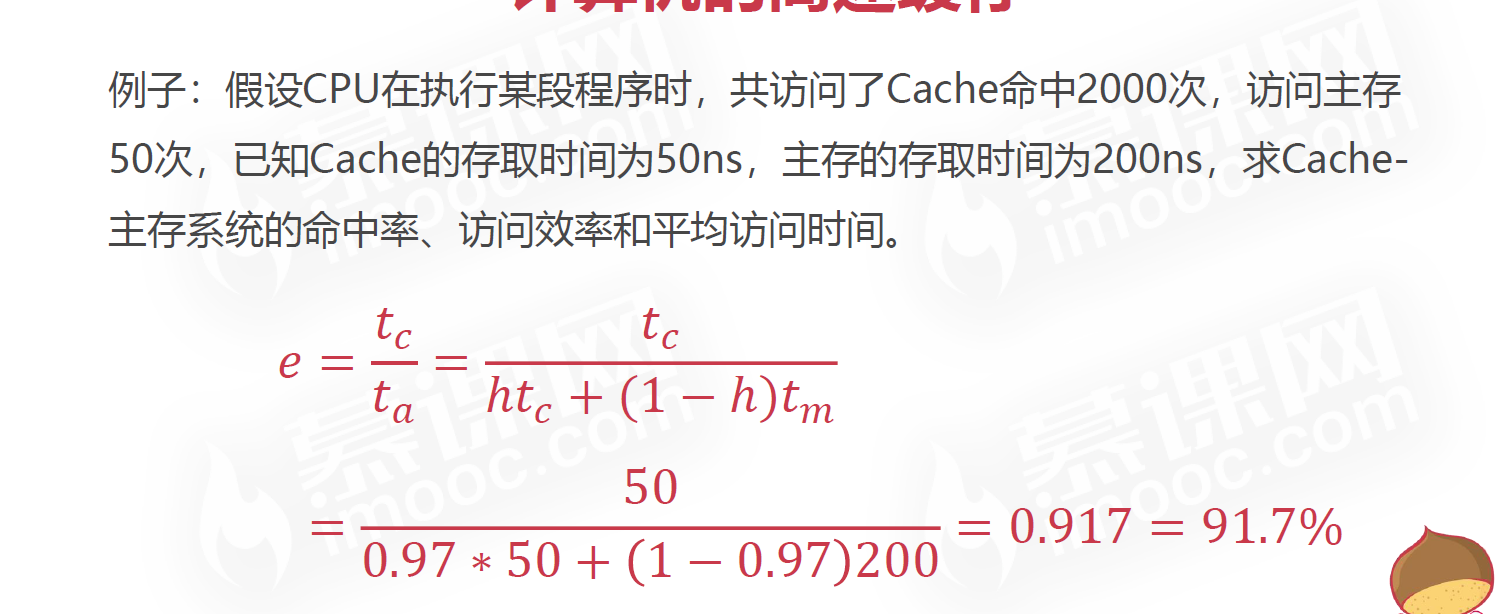

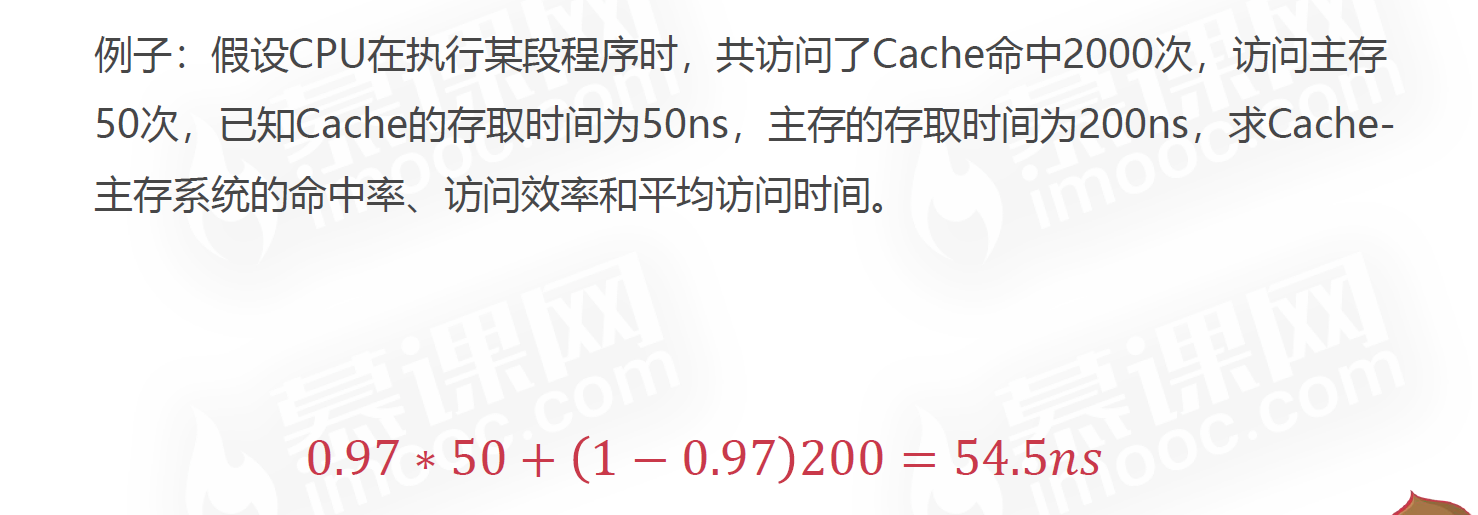

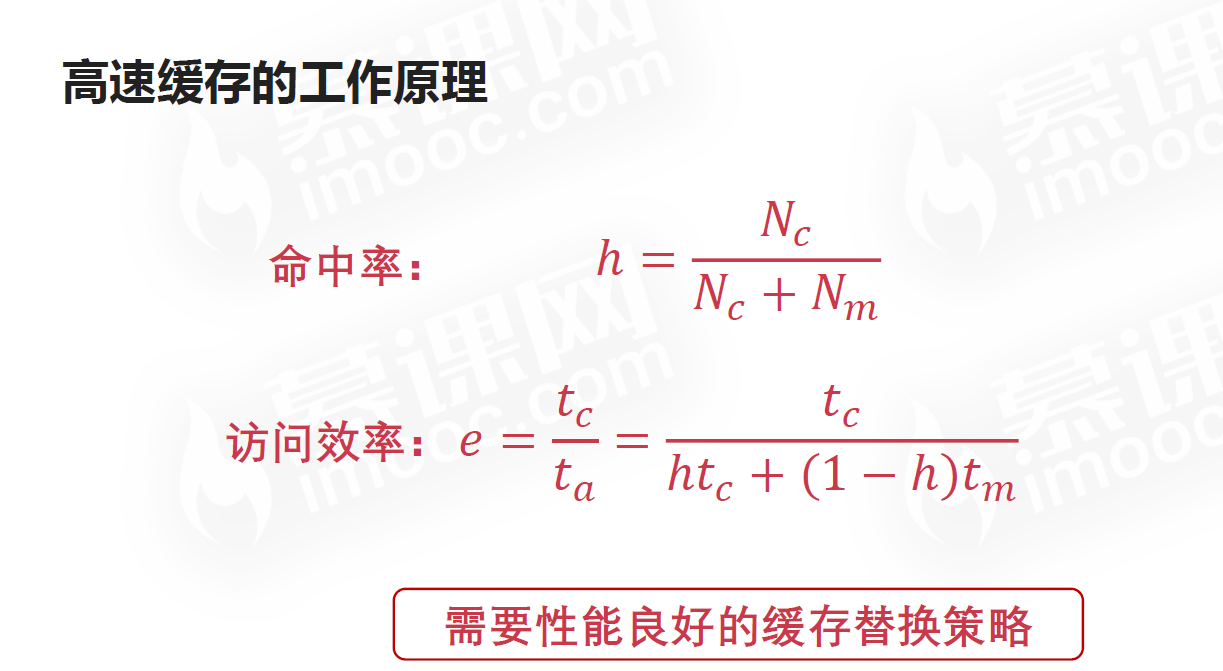

计算机的高速缓存

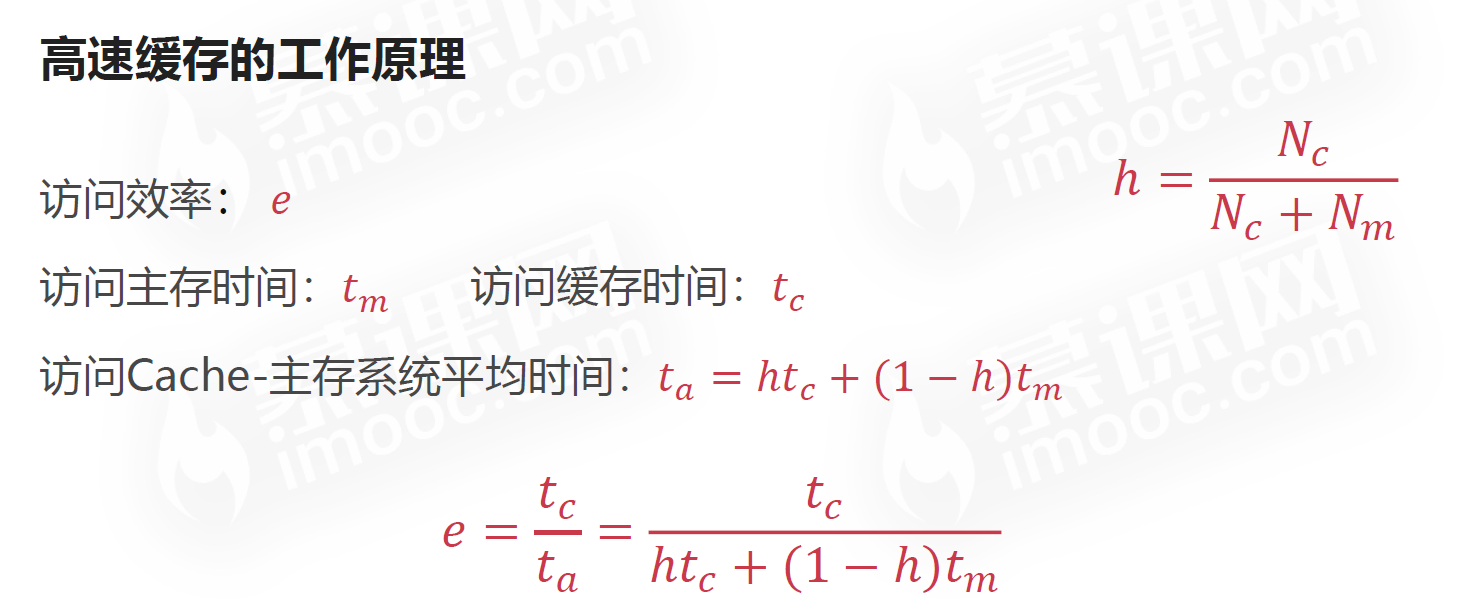

- 高速缓存的工作原理

- 高速缓存的替换策略

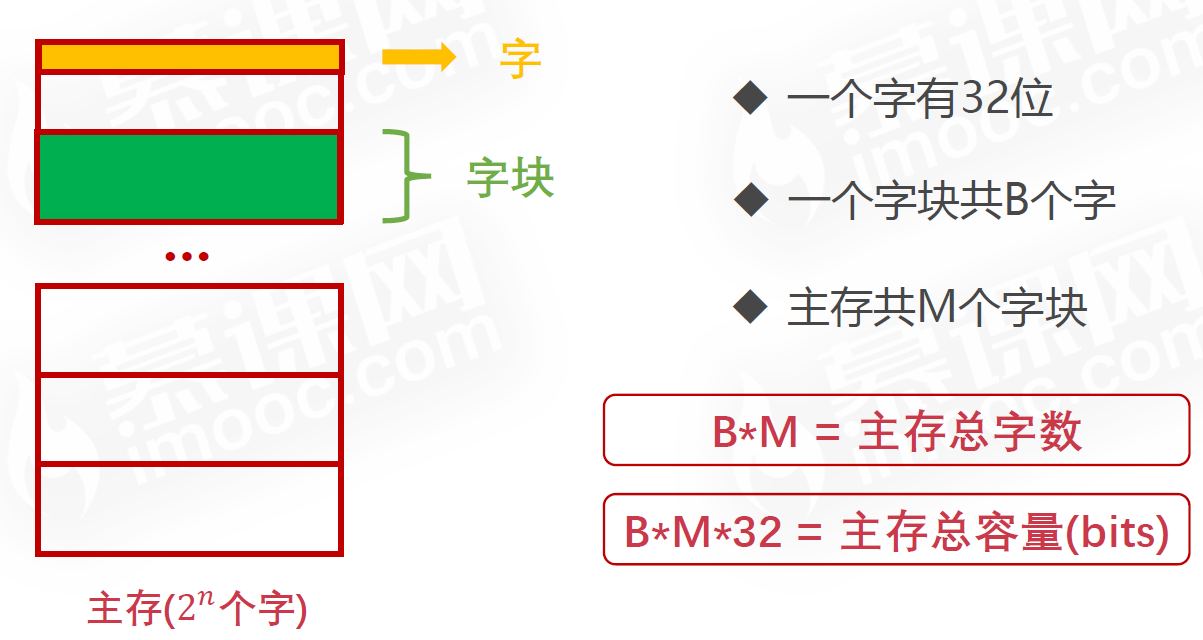

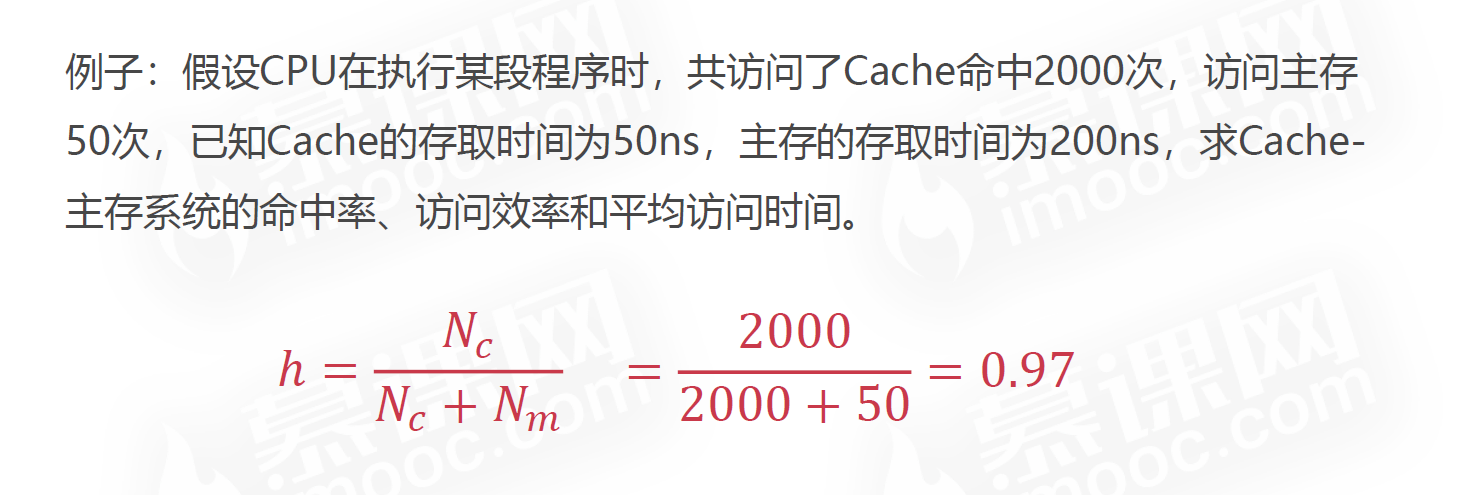

高速缓存的工作原理:

字:是指存放在一个存储单元中的二进制代码组合字块:存储在连续的存储单元中而被看作是一个单元的一组字

此处前m位指定字块的地址

高速缓存的替换策略

高速缓存的替换策略

- 随机算法

- 先进先出算法(FIFO)

- 最不经常使用算法(LFU)

- 最近最少使用算法(LRU)

先进先出算法(FIFO)

- 把高速缓存看做是一个先进先出的队列

- 优先替换最先进入队列的字块

最不经常使用算法(LFU)

- 优先淘汰最不经常使用的字块

- 需要额外的空间记录字块的使用频率

最近最少使用算法(LRU)

- 优先淘汰一段时间内没有使用的字块

- 有多种实现方法,一般使用双向链表

- 把当前访问节点置于链表前面(保证链表头部节点是最近使用的)

计算机的指令系统

- 机器指令的形式

- 机器指令的操作类型

- 机器指令的寻址方式

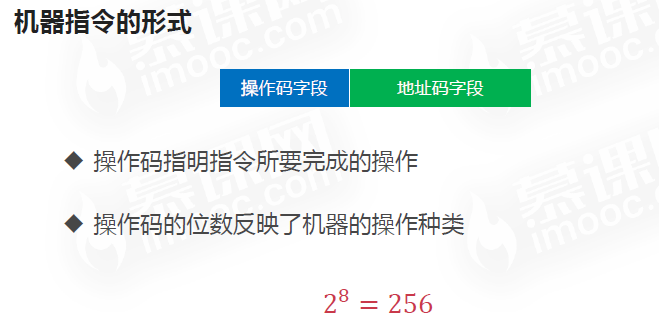

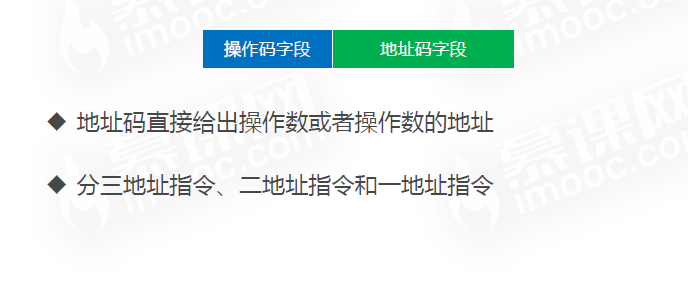

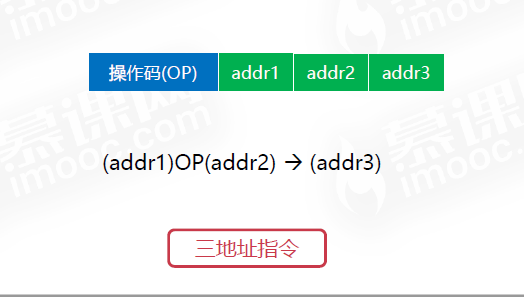

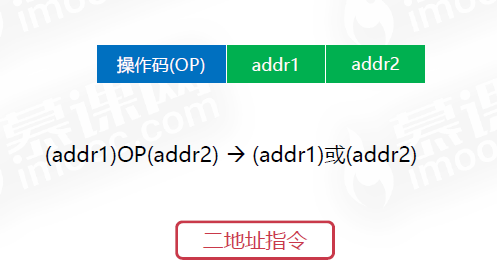

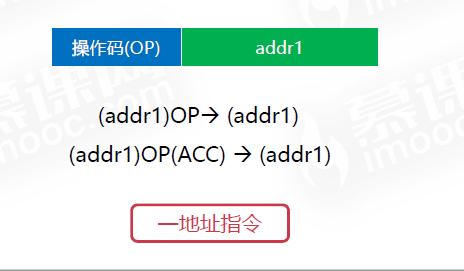

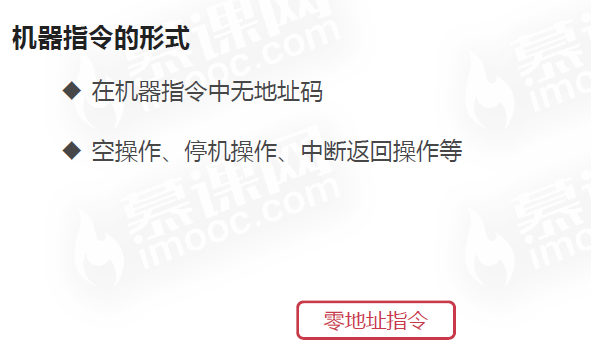

机器指令的形式

- 机器指令主要由两部分组成:操作码、地址码

机器指令的操作类型

- 数据传输

- 算术逻辑操作

- 移位操作

- 控制指令

数据传输

- 寄存器之间、寄存器与存储单元、存储单元之间传送

- 数据读写、交换地址数据、清零置一等操作

算术逻辑操作

- 操作数之间的加减乘除运算

- 操作数的与或非等逻辑位运算

移位操作

- 数据左移(乘2)、数据右移(除2)

- 完成数据在算数逻辑单元的必要操作

控制指令

- 等待指令、停机指令、空操作指令、中断指令等

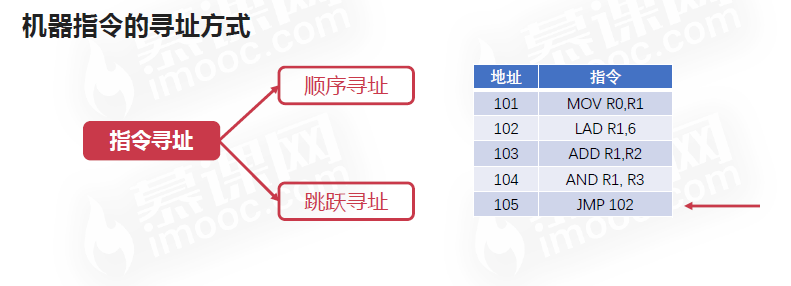

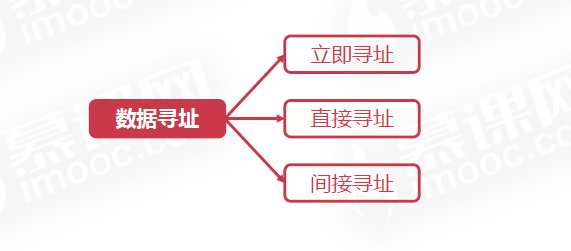

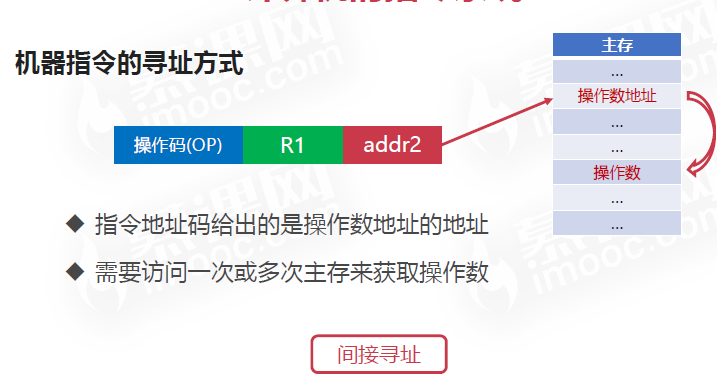

机器指令的寻址方式

- 指令寻址

- 数据寻址

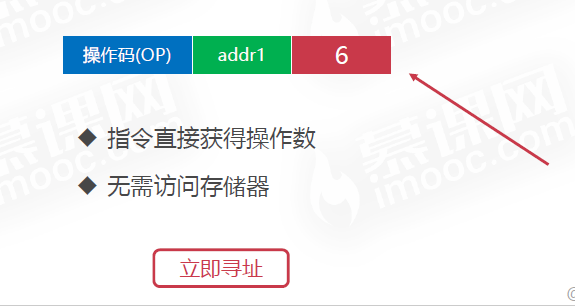

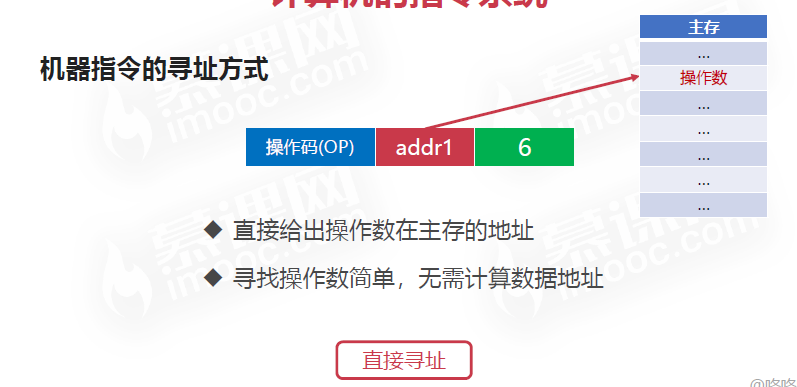

| 寻址方式 | 优点 | 缺点 |

|---|---|---|

| 立即寻址 | 速度快 | 地址码位数限制操作数表示范围 |

| 直接寻址 | 寻找操作数简单 | 地址码位数限制操作数寻址范围 |

| 间接寻址 | 操作数寻址范围大 | 速度较慢 |

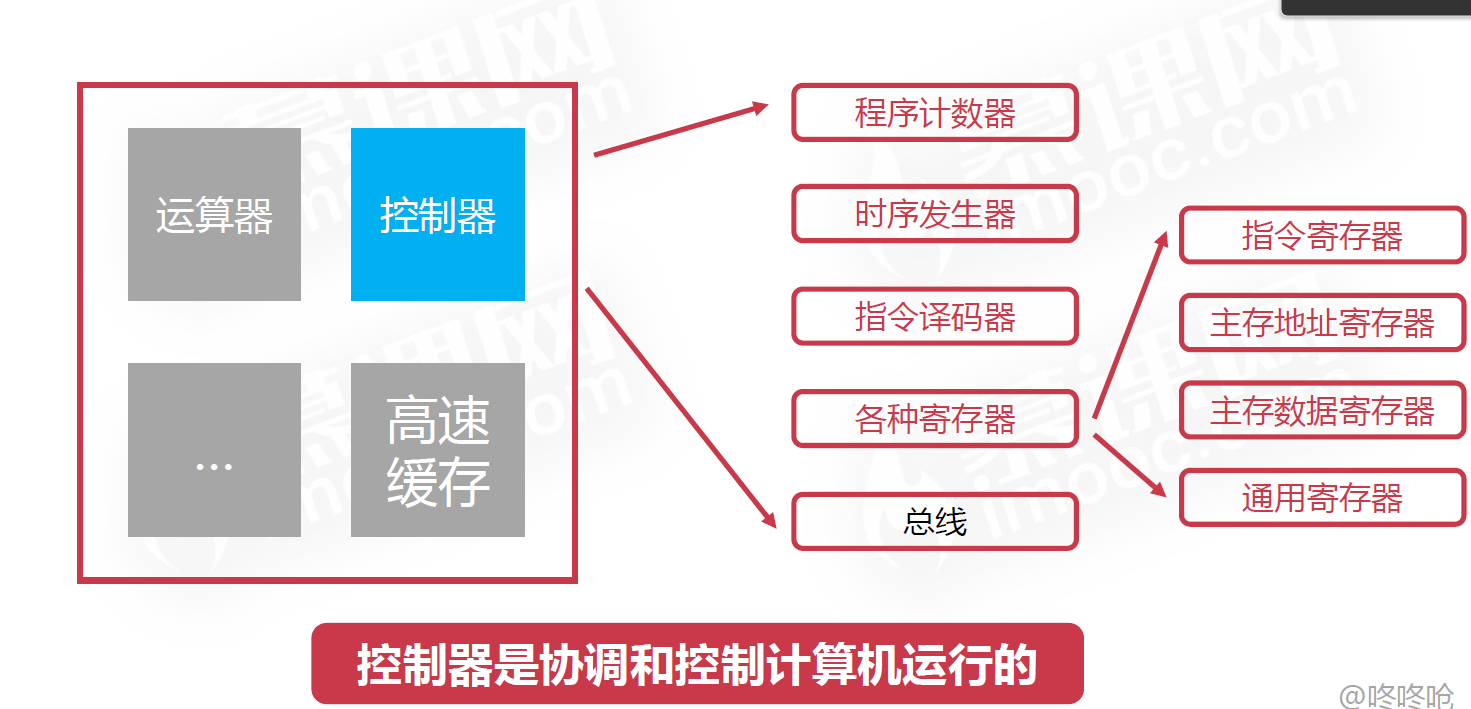

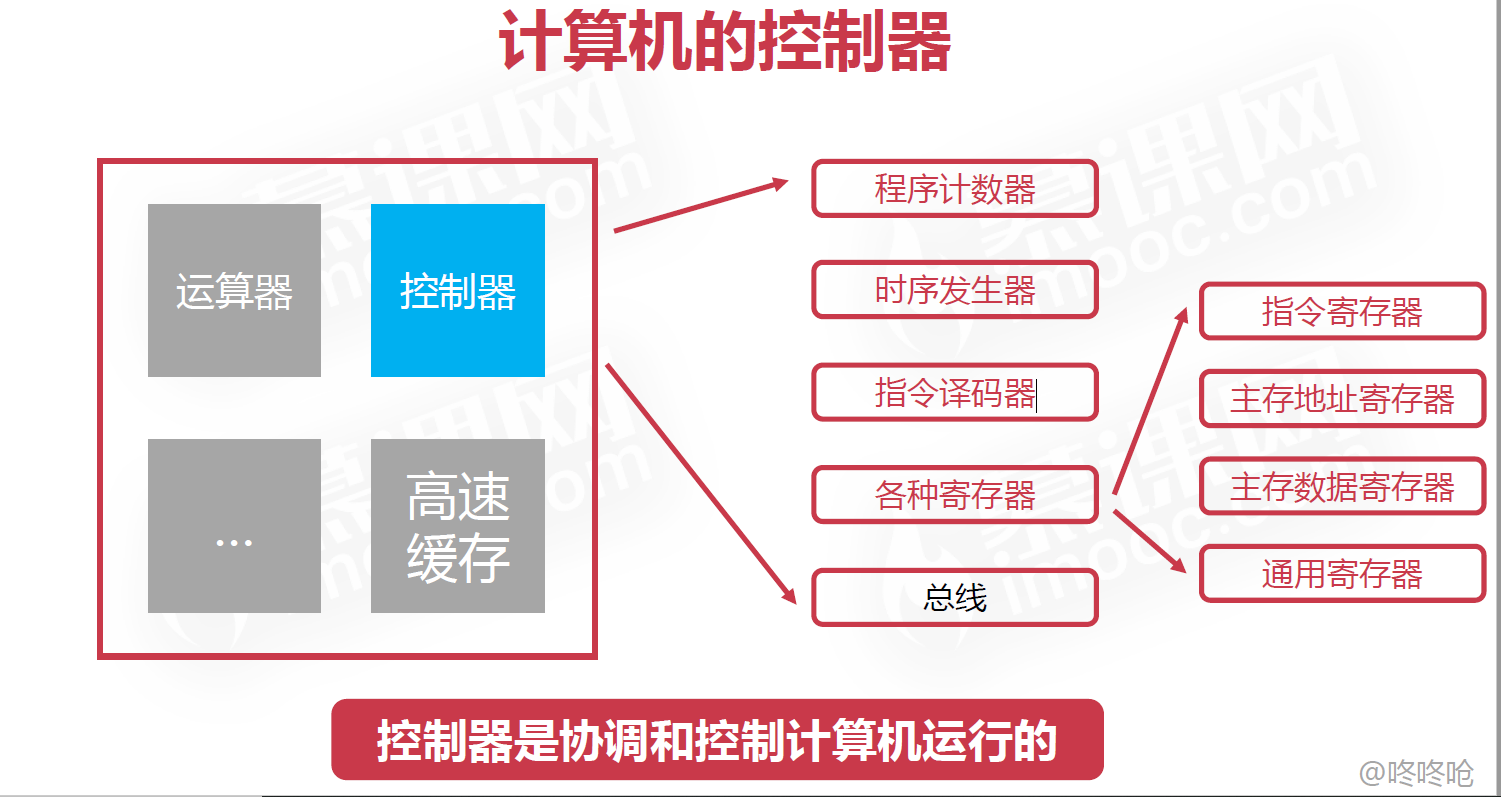

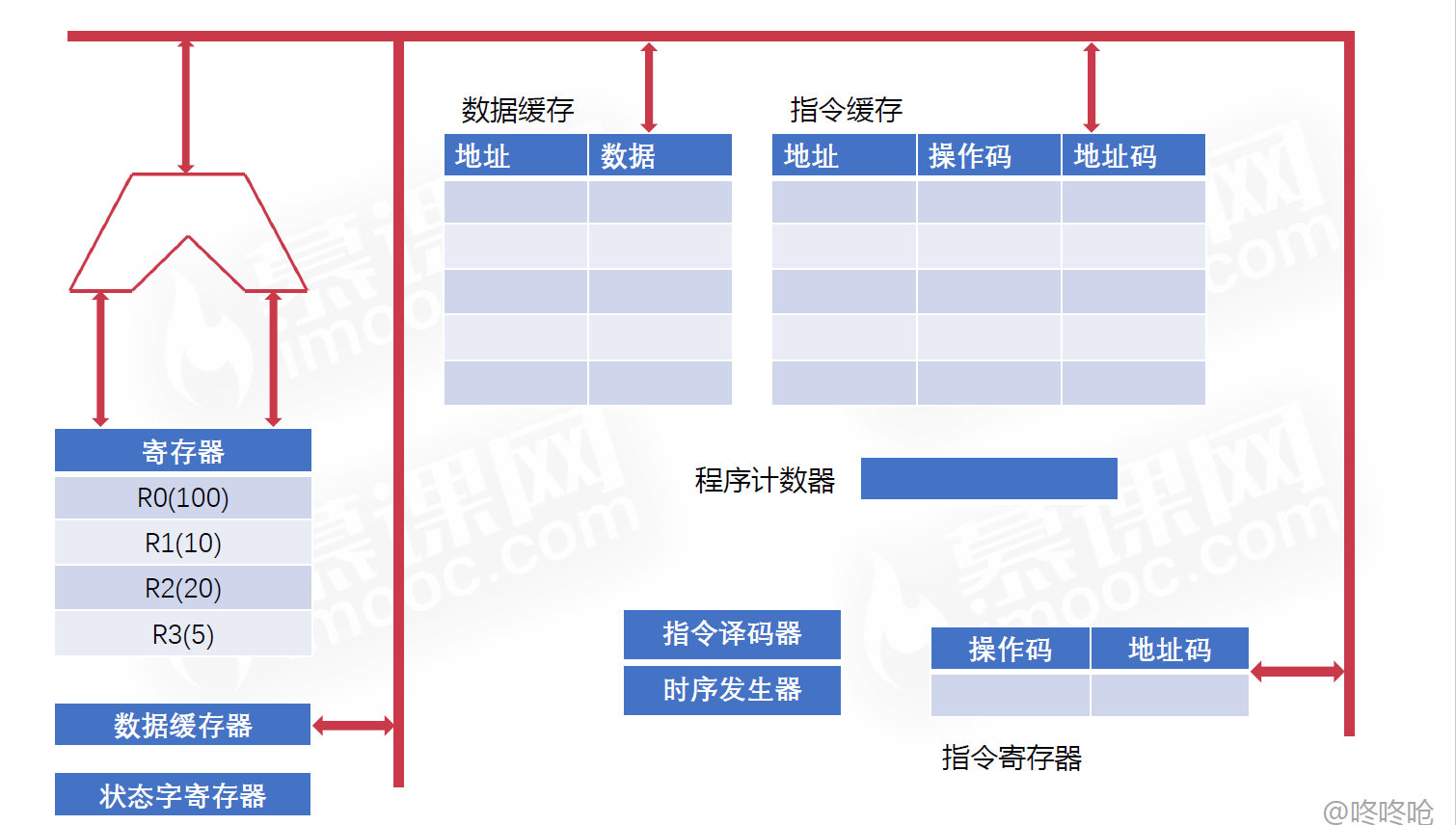

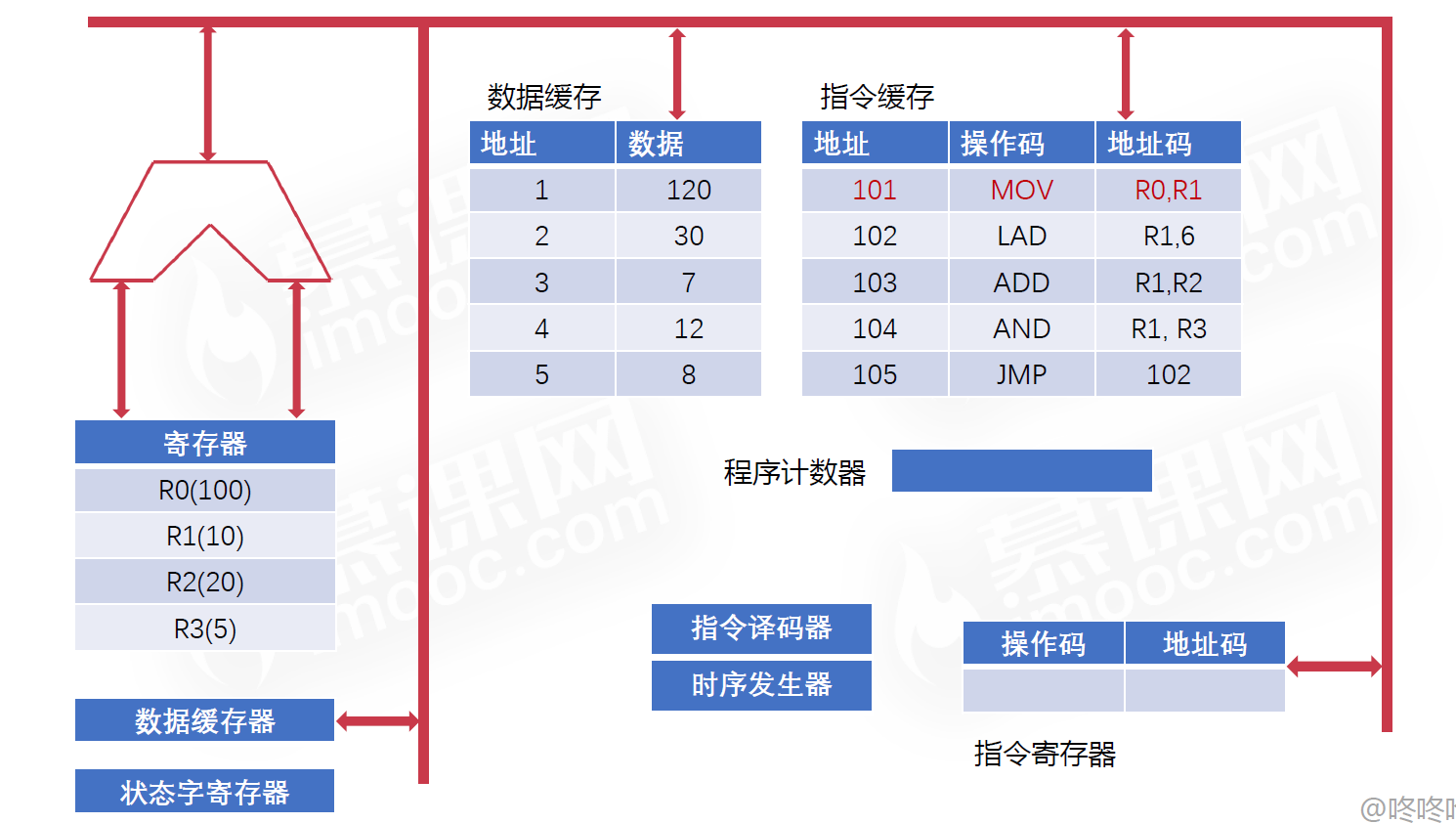

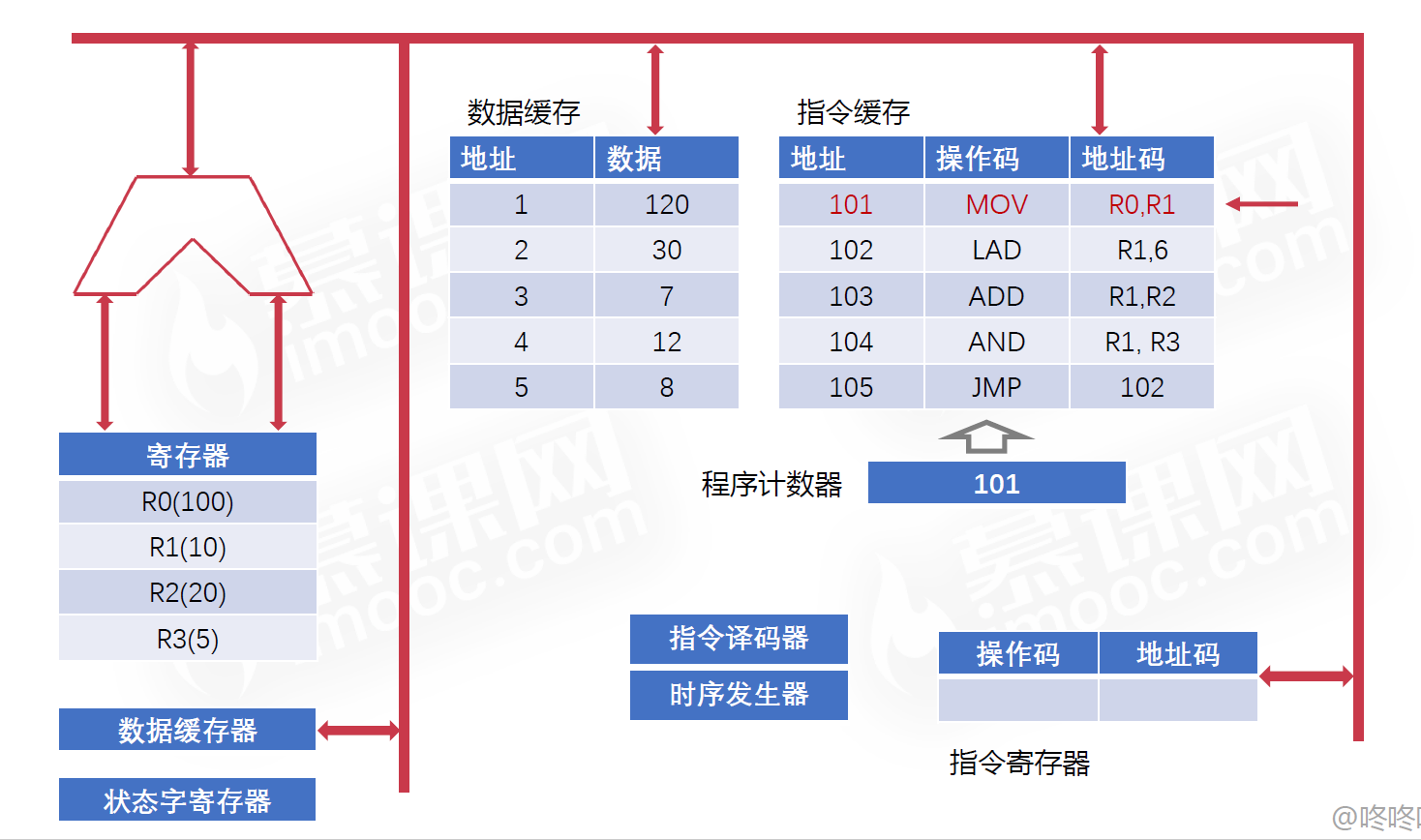

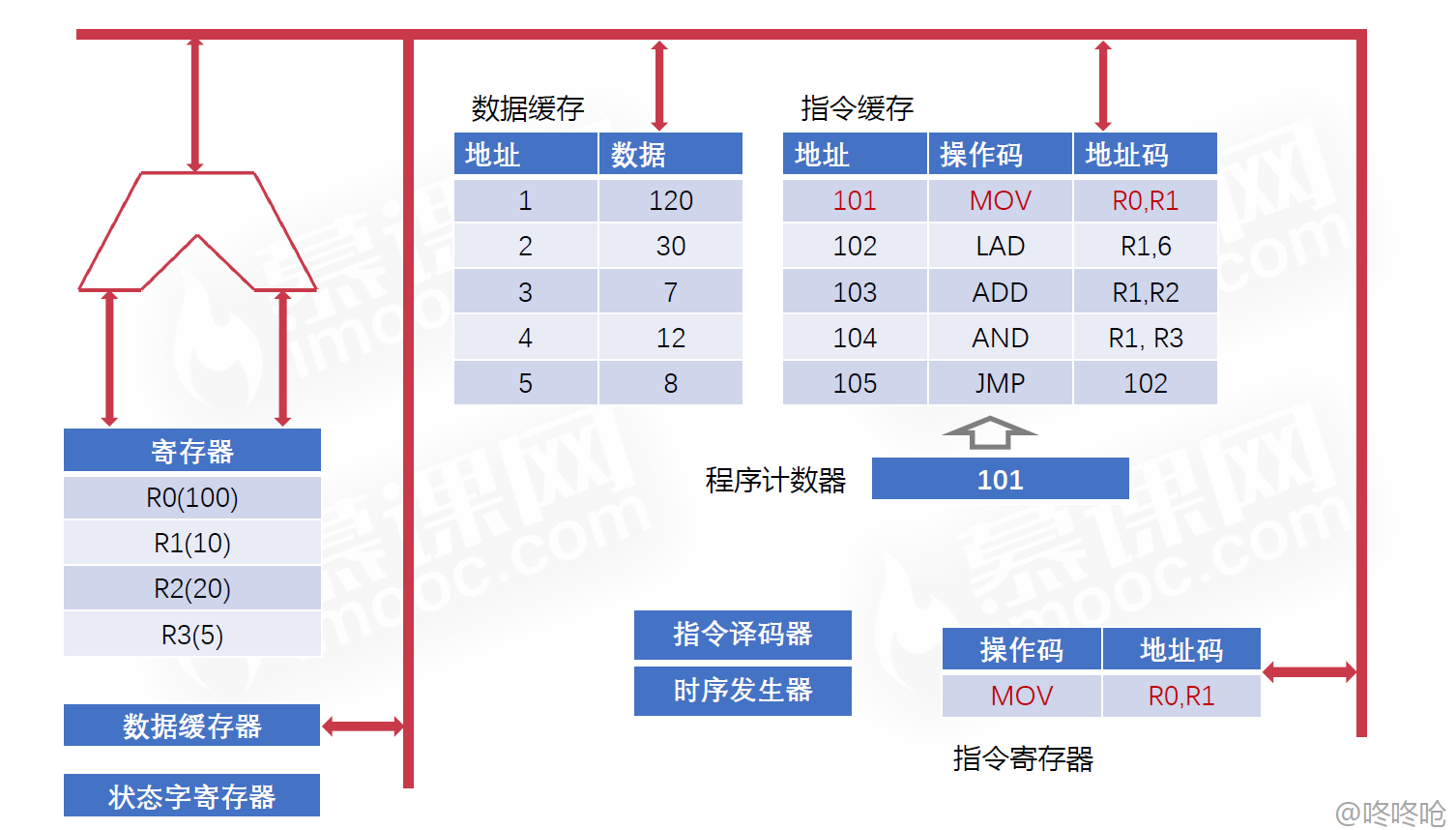

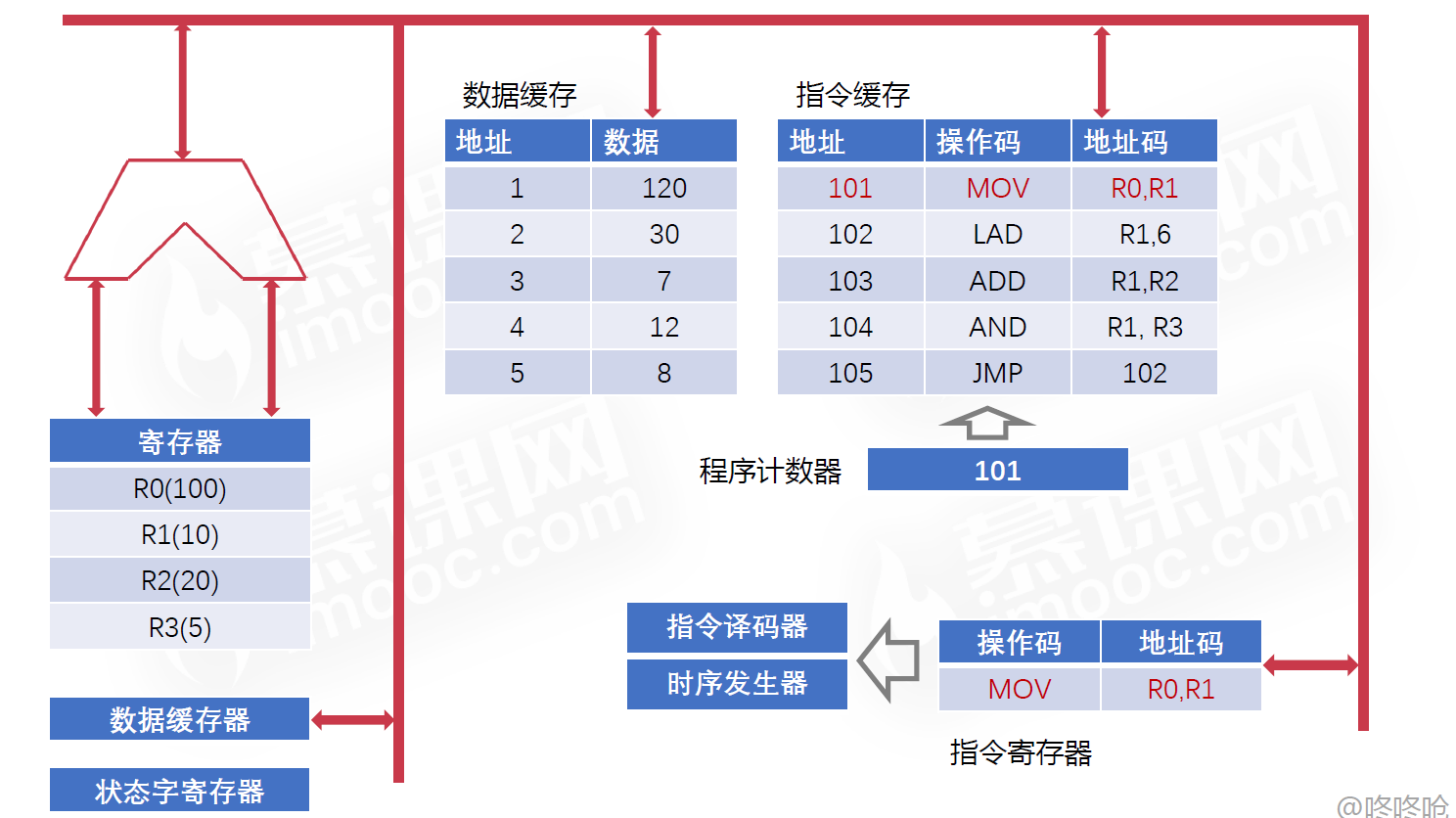

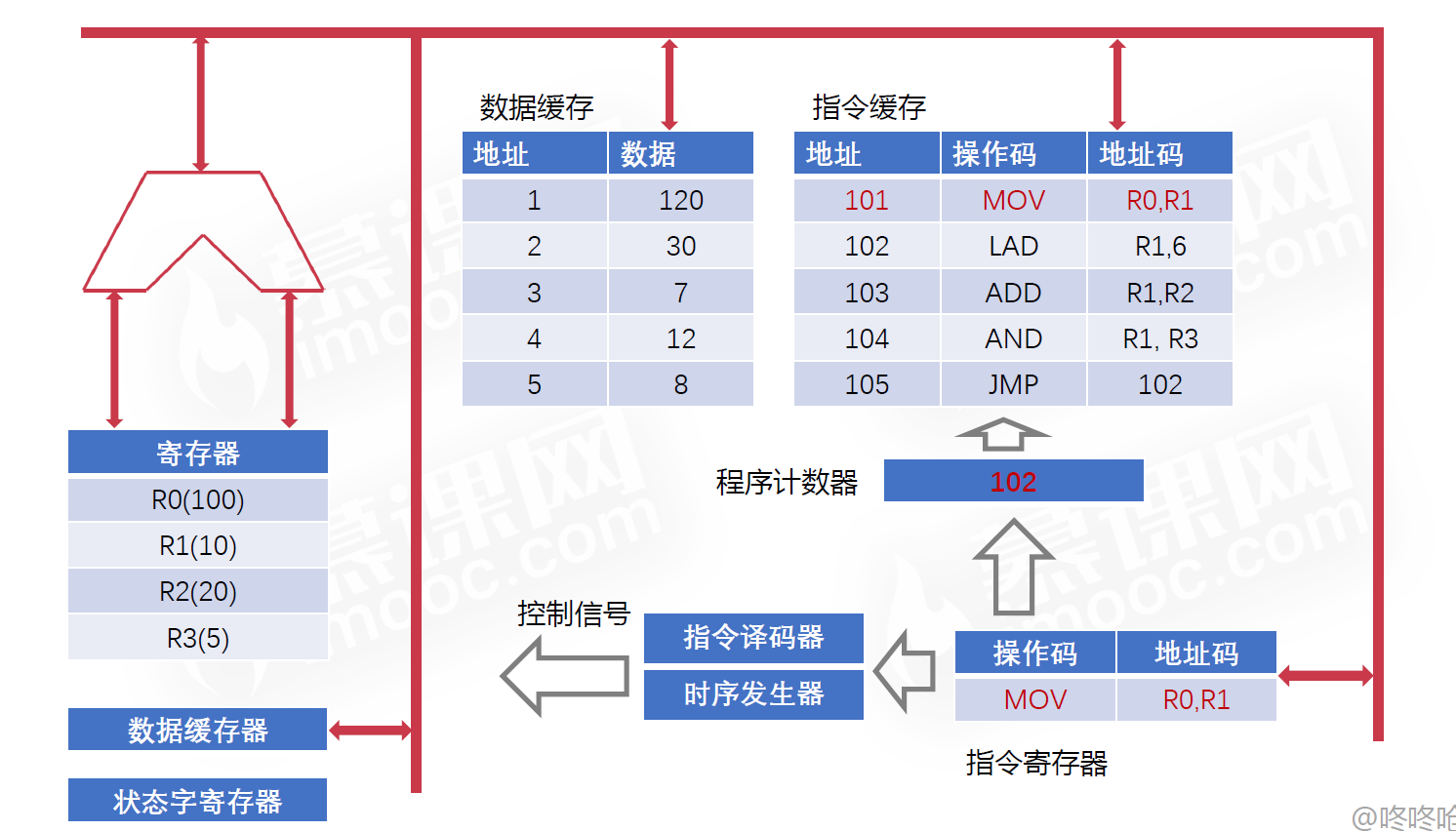

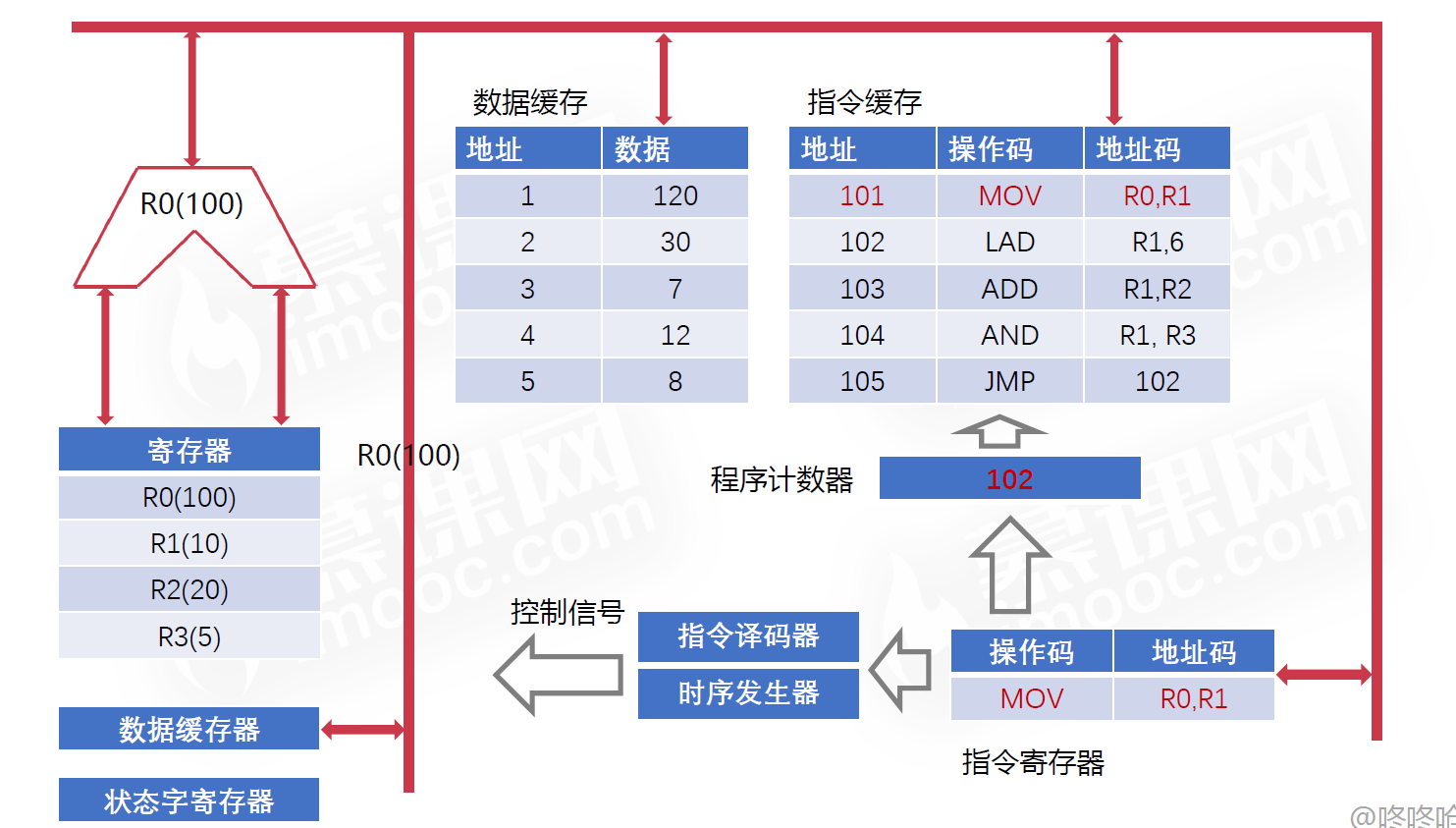

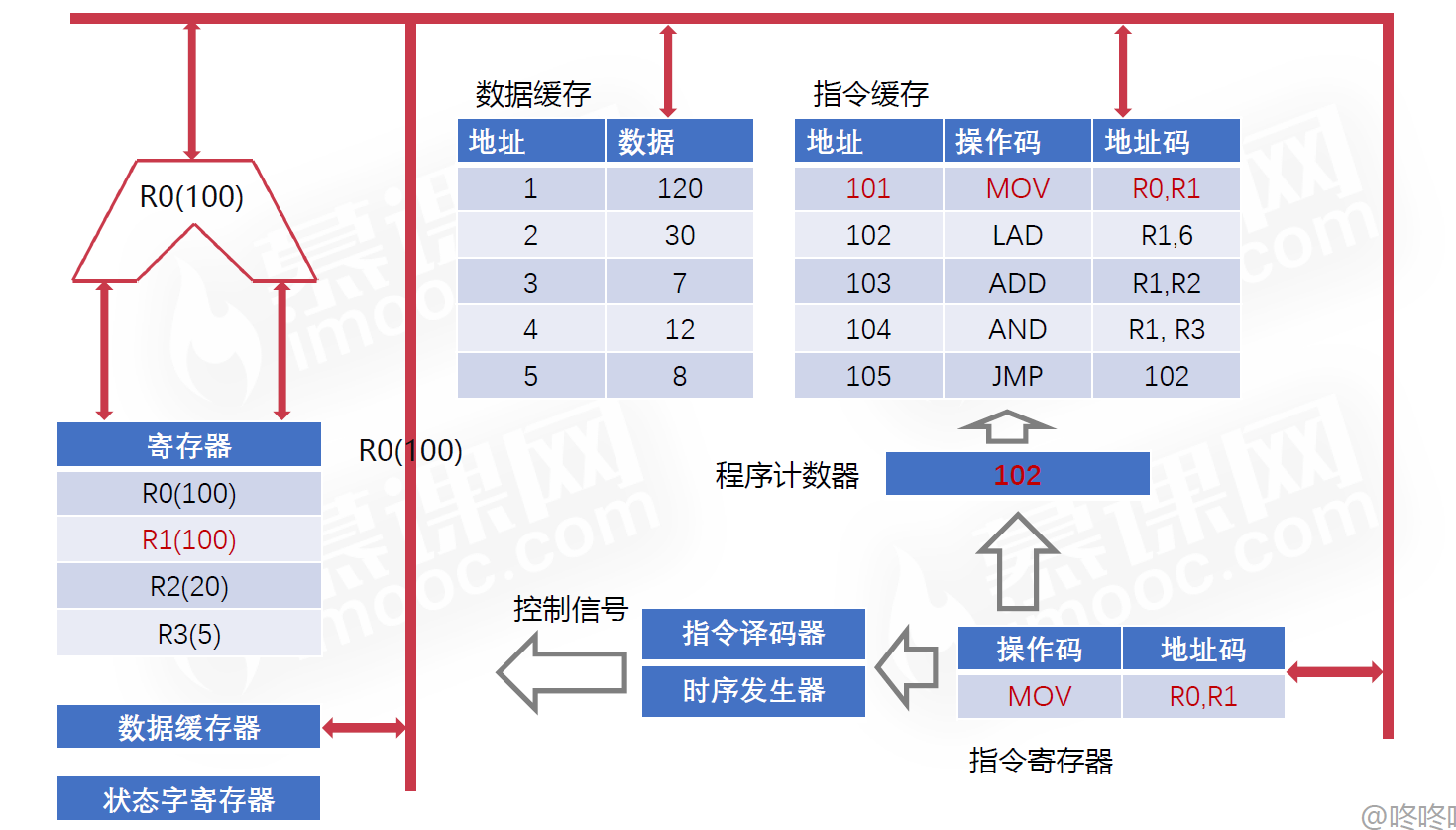

计算机的控制器

程序计数器

- 程序计数器用来存储下一条指令的地址

- 循环从程序计数器中拿出指令

- 当指令被拿出时,指向下一条指令。

时序发生器

- 电气工程领域,用于发送时序脉冲

- CPU根据不同的时序脉冲有节奏的进行工作

指令译码器

- 指令译码器是控制器的主要部件之一

- 计算机指令由操作码和地址码组成

- 翻译操作码对应的操作以及控制传输地址码对应的数据

指令寄存器

- 指令寄存器也是控制器的主要部件之一

- 从主存或高速缓存取计算机指令

主存地址寄存器

- 保存当前CPU正要访问的内存单元的地址

主存数据寄存器

- 保存当前CPU正要读或写的主存数据

通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU的运算中间结果

- 容量比一般专用寄存器要大

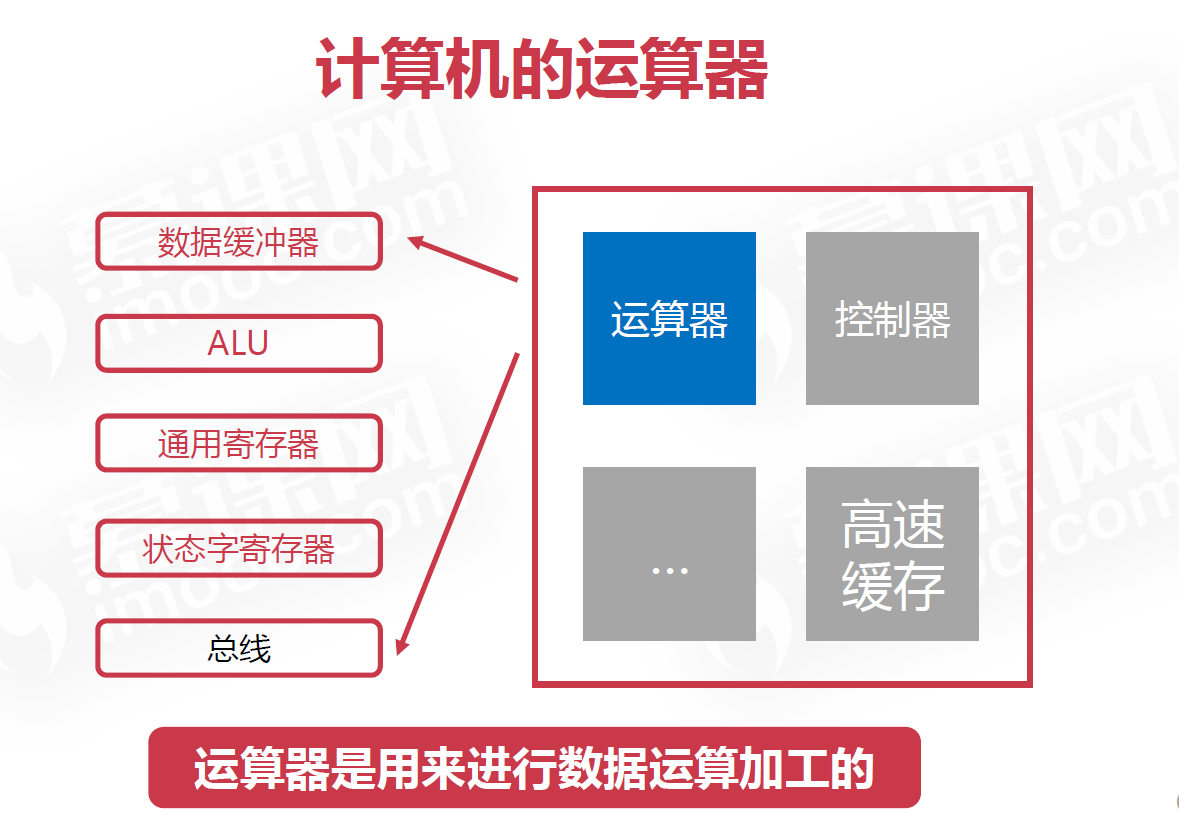

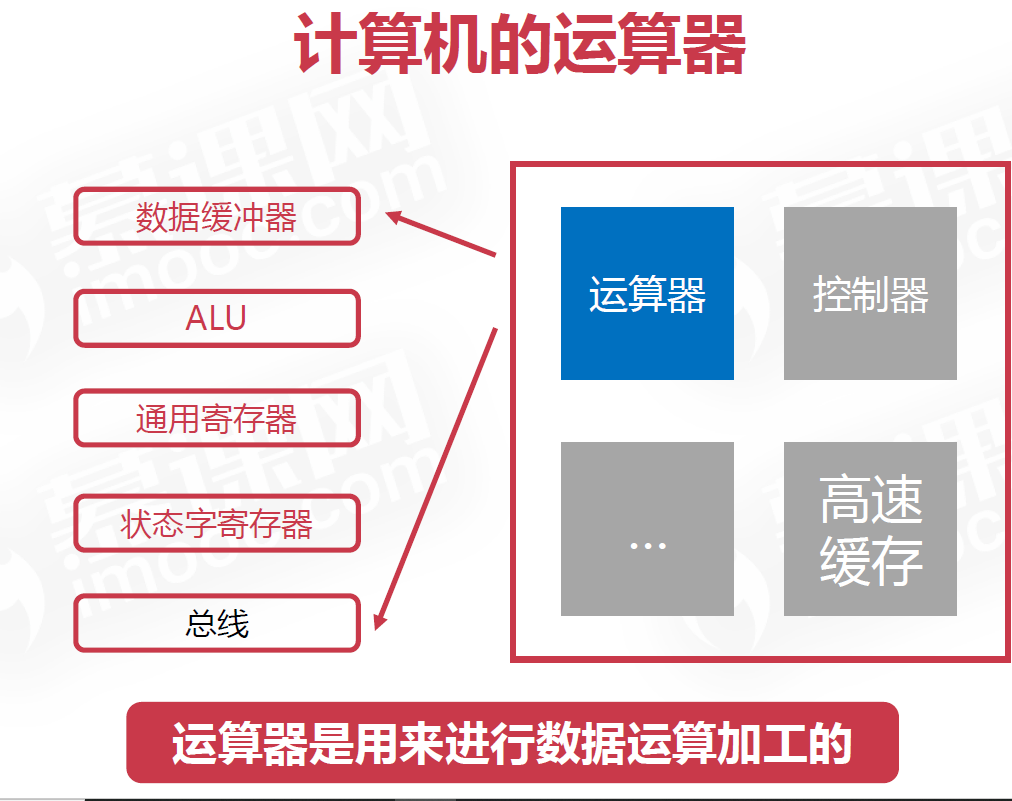

计算机的运算器

- 数据缓冲器

- ALU

- 通用寄存器

- 状态字寄存器

- 总线

数据缓冲器

- 分为输入缓冲和输出缓冲

- 输入缓冲暂时存放外设送过来的数据

- 输出缓冲暂时存放送往外设的数据

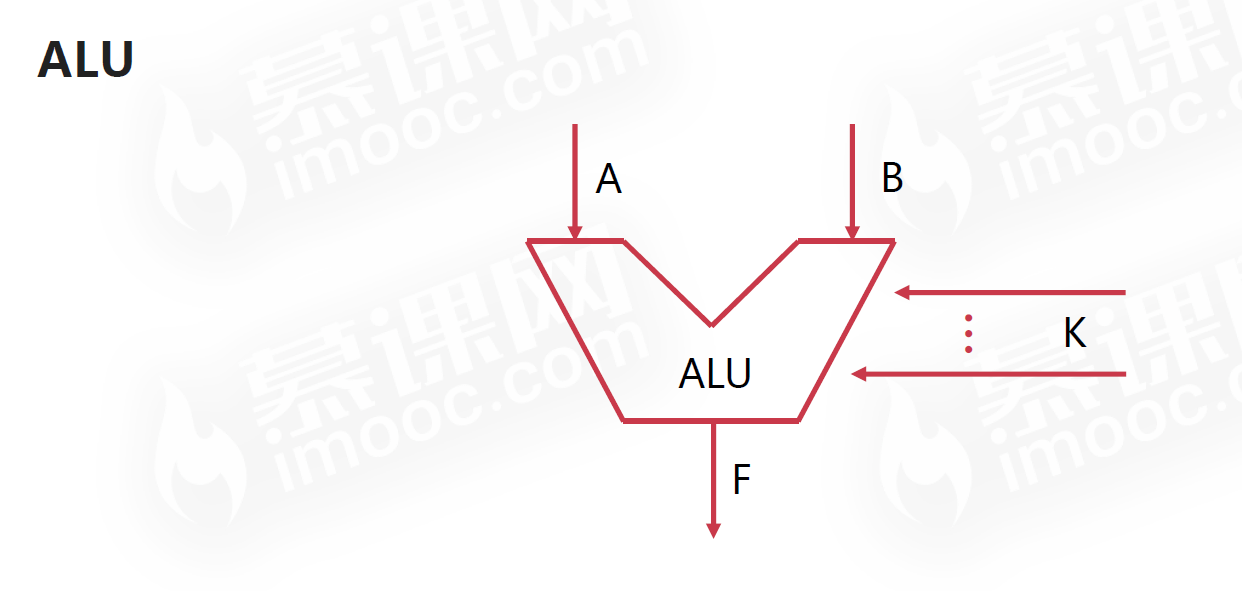

ALU

- ALU:算数逻辑单元,是运算器的主要组成

- 常见的位运算(左右移动、与或非等)

- 算术运算(加减乘除等)

状态字寄存器

- 存放运算状态(条件码、进位、溢出、结果正负等)

- 存放运算控制信息(调试跟踪标记位、允许中断位等)

通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU的运算中间结果

- 容量比一般专用寄存器要大

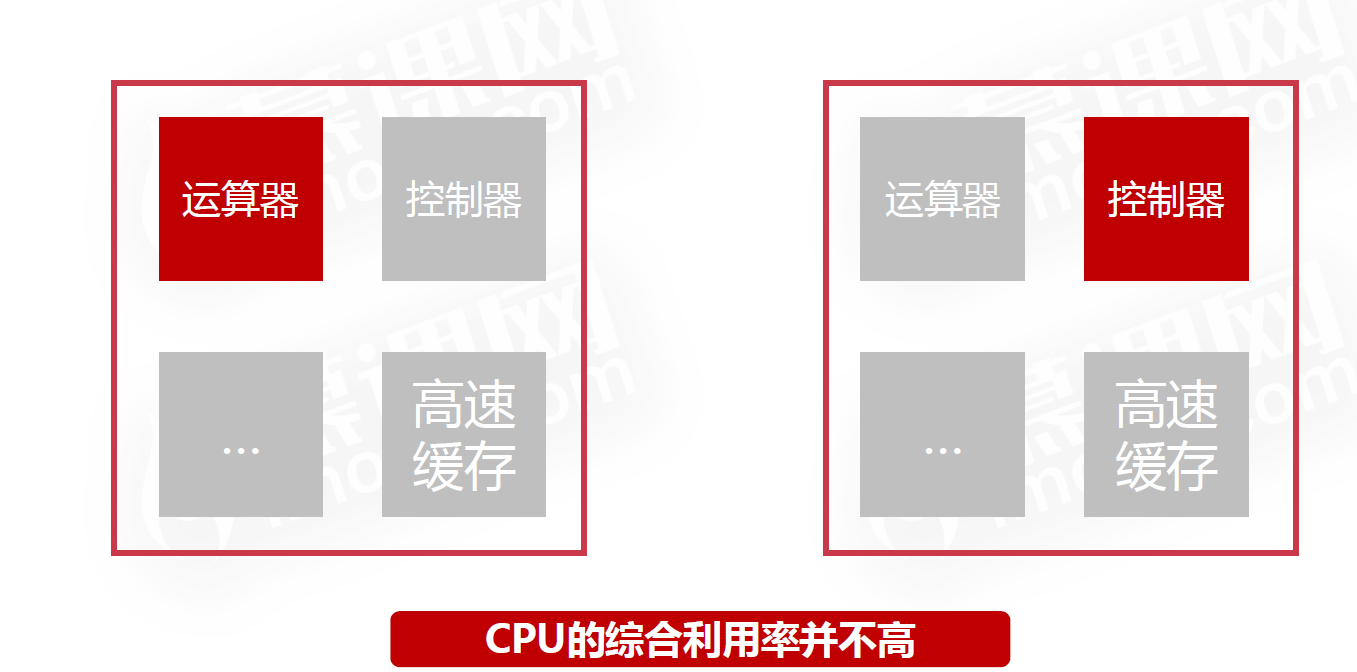

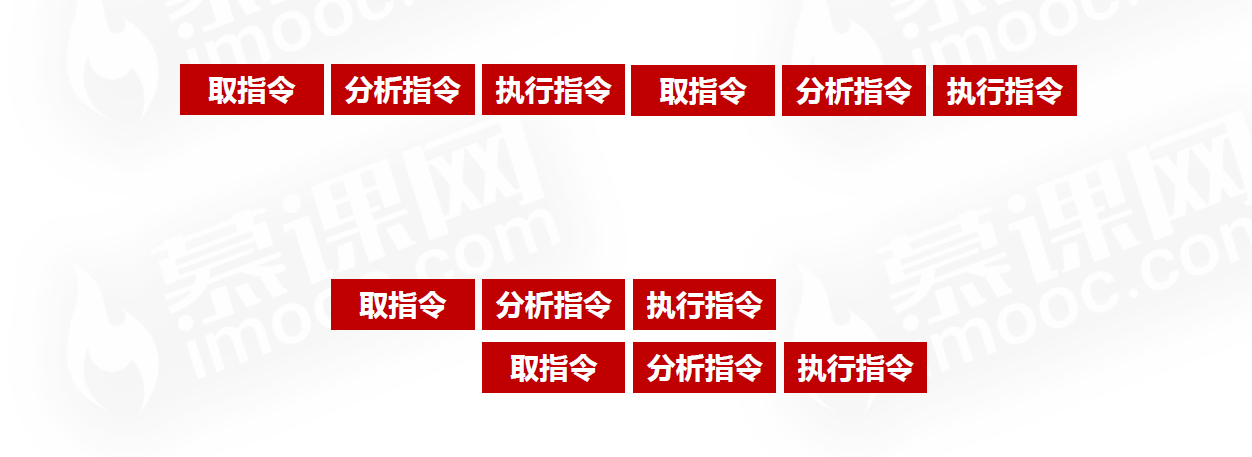

计算机指令的执行过程

- 指令执行过程

- CPU的流水线设计

指令執行過程

取指令->分析指令->执行指令

CPU的流水线设计

- 类似工厂的装配线

- 工厂的装配线使得多个产品可以同时被加工

- 在同一个时刻,不同产品均位于不同的加工阶段

串行执行m条指令 : T1 = 3t * m

流水线执行m条指令:t2 = t(m+2)

H = t2/t1 = t(m+2)/3t*m = 1/3 + 1/3m

计算机的异构计算设备

- 图像处理器(GPU)

- 现场可编程门阵列(FPGA)

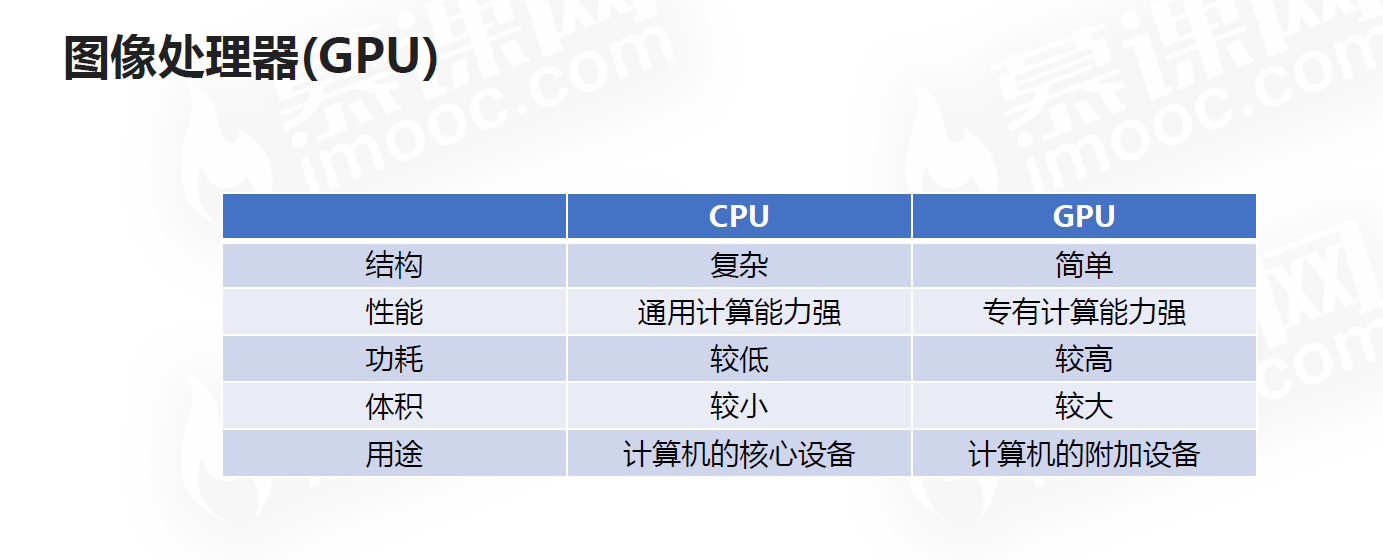

图像处理器(GPU)

- 又称显示核心、视觉处理器、显示芯片

- 擅长执行复杂的数学和几何计算

现场可编程门阵列(FPGA)

- 是一种专用集成电路,诞生于1985年

- 电路级别的设备,属于硬件层面的开发

- AI人工智能的大热,FPGA逐渐走进大众的视野

浙公网安备 33010602011771号

浙公网安备 33010602011771号