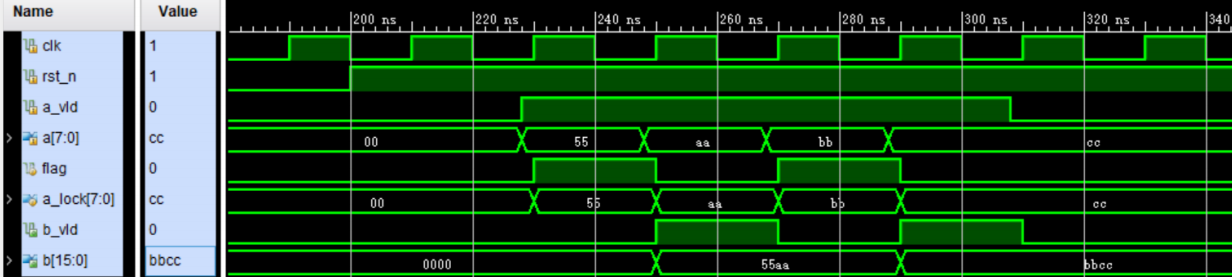

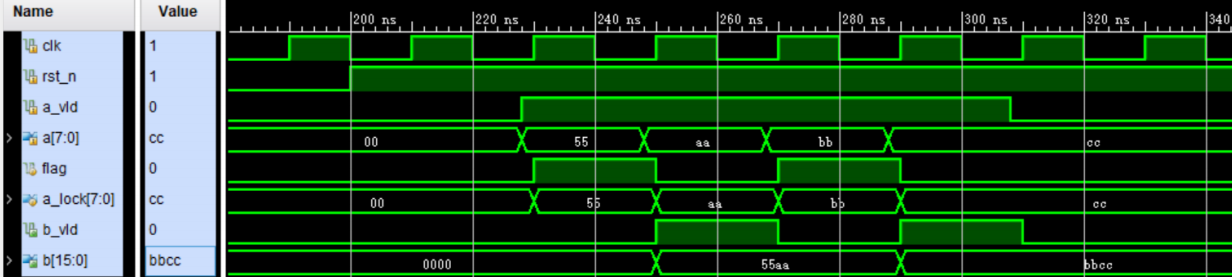

一、整数倍拼接

1 module width_change_8to16

2 (

3 input clk ,

4 input rst_n ,

5 input a_vld ,

6 input [ 7:0] a ,

7 output reg b_vld ,

8 output reg [15:0] b

9 );

10 reg flag ;

11 reg [7:0] a_lock ;

12 //==========================================================================

13 //== code

14 //==========================================================================

15 //拼接指示

16 always @ (posedge clk or negedge rst_n) begin

17 if(~rst_n)

18 flag <= 1'b0;

19 else if(a_vld)

20 flag <= ~flag;

21 end

22

23 //数据移位

24 always @ (posedge clk or negedge rst_n) begin

25 if(~rst_n)

26 a_lock <= 8'b0;

27 else if(a_vld)

28 a_lock <= a;

29 end

30

31 //数据拼接

32 always @ (posedge clk or negedge rst_n) begin

33 if(~rst_n)

34 b <= 16'b0;

35 else if(flag)

36 b <= {a_lock,a};

37 end

38

39 //拼接后的数据有效指示

40 always @ (posedge clk or negedge rst_n) begin

41 if(~rst_n)

42 b_vld <= 1'b0;

43 else if (flag)

44 b_vld <= 1'b1;

45 else

46 b_vld <= 1'b0;

47 end

48

49 endmodule

二、非整数倍拼接

1 module width_change_8to12

2 (

3 input clk ,

4 input rst_n ,

5 input a_vld ,

6 input [ 7:0] a ,

7 output reg b_vld ,

8 output reg [12:0] b

9 );

10 reg [1:0] vld_cnt ;

11 reg [7:0] a_lock ;

12 //==========================================================================

13 //== code

14 //==========================================================================

15 //拼接计数

16 always @ (posedge clk or negedge rst_n) begin

17 if(~rst_n)

18 vld_cnt <= 2'b0;

19 else if(vld_cnt == 3-1)

20 vld_cnt <= 2'b0;

21 else if(a_vld) begin

22 vld_cnt <= vld_cnt + 2'b1 ;

23 end

24 end

25

26 //数据移位

27 always @ (posedge clk or negedge rst_n) begin

28 if(~rst_n)

29 a_lock <= 8'b0;

30 else if (a_vld)

31 a_lock <= a;

32 end

33

34 //数据拼接

35 always @ (posedge clk or negedge rst_n) begin

36 if(~rst_n)

37 b <= 12'b0;

38 else if(vld_cnt==2-1)

39 b <= {a_lock,a[7:4]}; //拼接第一个数据和第二个数据高4位

40 else if(vld_cnt==3-1)

41 b <= {a_lock[3:0],a}; //拼接第二个数据低4位和第二个数据

42 else

43 b <= 1'b0;

44 end

45

46 //拼接后的数据有效指示

47 always @ (posedge clk or negedge rst_n) begin

48 if(~rst_n)

49 b_vld <= 1'b0;

50 else if(vld_cnt==2-1)

51 b_vld <= 1'b1;

52 else if(vld_cnt==3-1)

53 b_vld <= 1'b1;

54 else

55 b_vld <= 1'b0;

56 end

57

58 endmodule