【转】Xilinx FPGA ChipScope的ICON/ILA/VIO核使用

--------------------------------------------------------------------------------------------------------------------------

使用ChipScope有两种方式:

第一种,使用CoreInsert,可参考下面链接:

这种方法可以快速的使用ICON和ILA核,以及ATC2核,而且不必修改原代码。缺点是不能使用其他核,如VIO核。以及用ILA观测信号时,有的可能被综合器综合掉的信号就观察不到了。

第二种,使用Generator的方法,可参考下面链接,是一个Verilog的使用教程。

官方推荐使用方法二,在工程中添加IP核,然后例化到程序中,需要修改原代码,但可以使用所有ChipScope核,且使用灵活。

下面,使用方法二,使用VHDL来完成ICON/ILA/VIO的使用,相关工程文件可从这下载:http://download.csdn.net/detail/sundonga/8284747

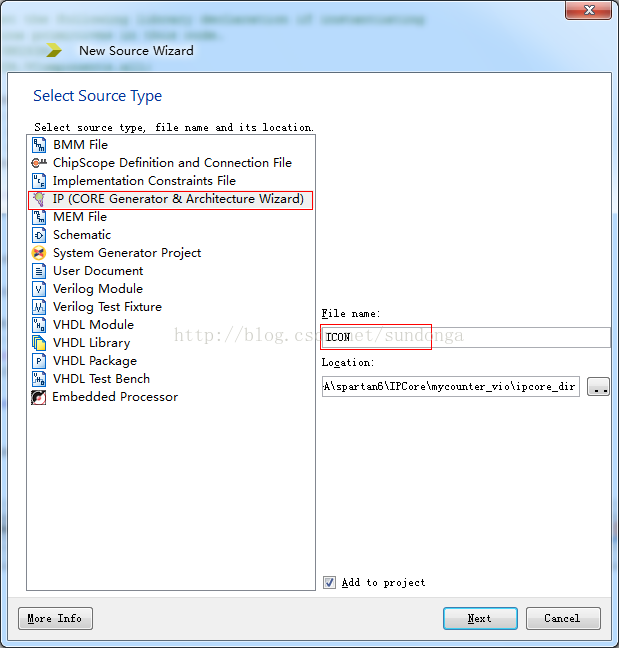

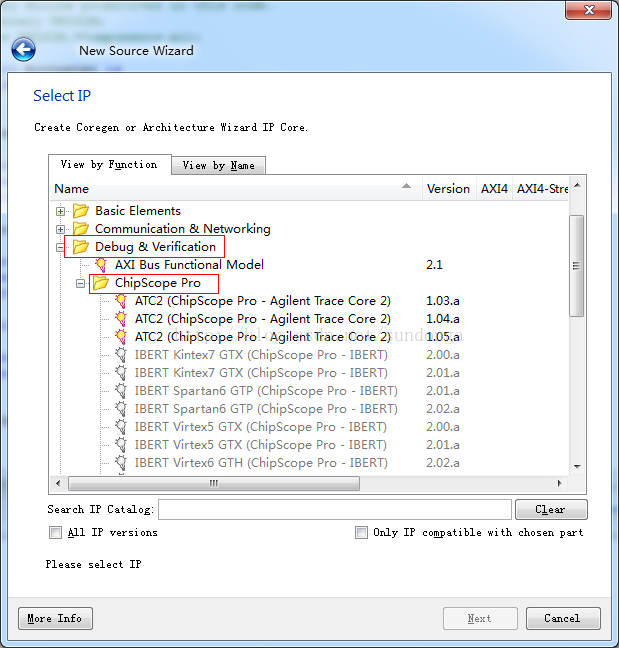

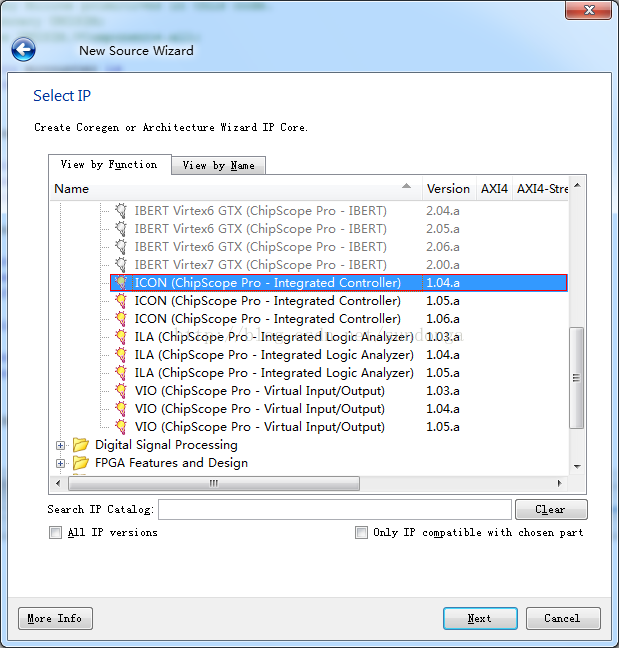

1. 以一个8位的加法器为例,写好加法器的代码后,先加入一个ICON核

2. 设置ICON核的参数,由于要与一个ILA核和一个VIO核相连,因此控制口选择2,如下图。

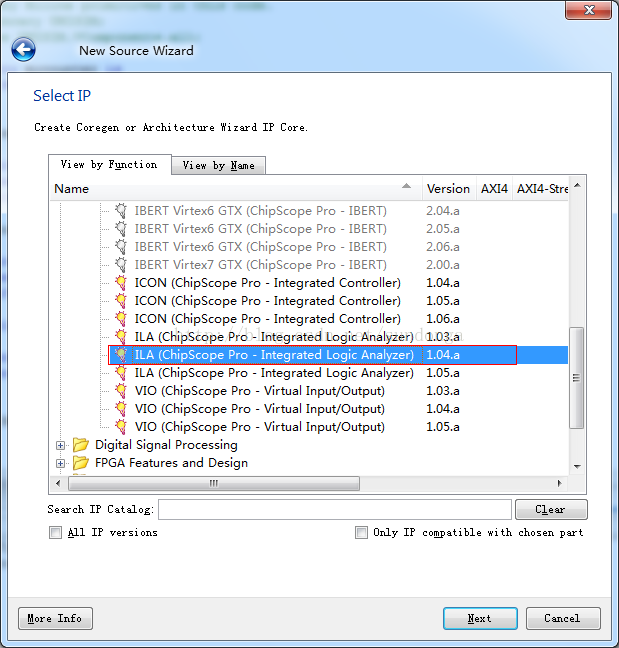

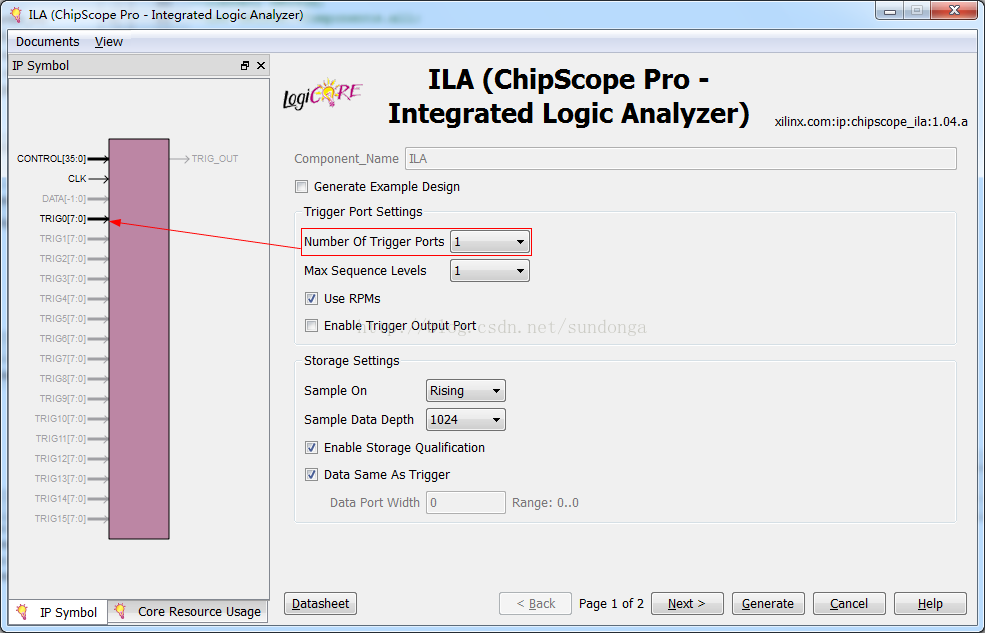

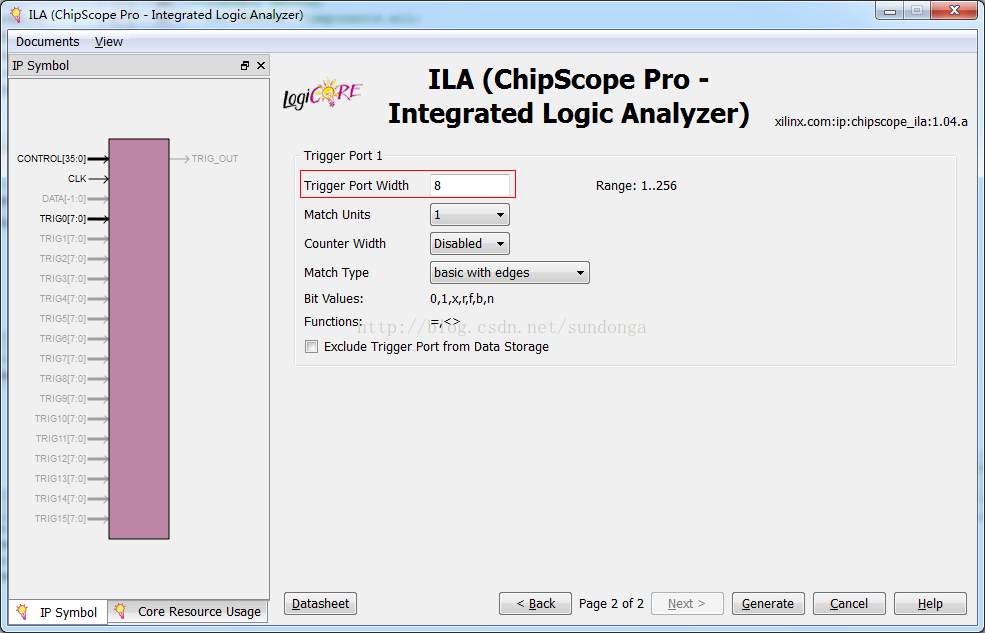

3. 添加ILA核,选择一组观测,且一组观测8位,用来观测我的8位加法器的值。

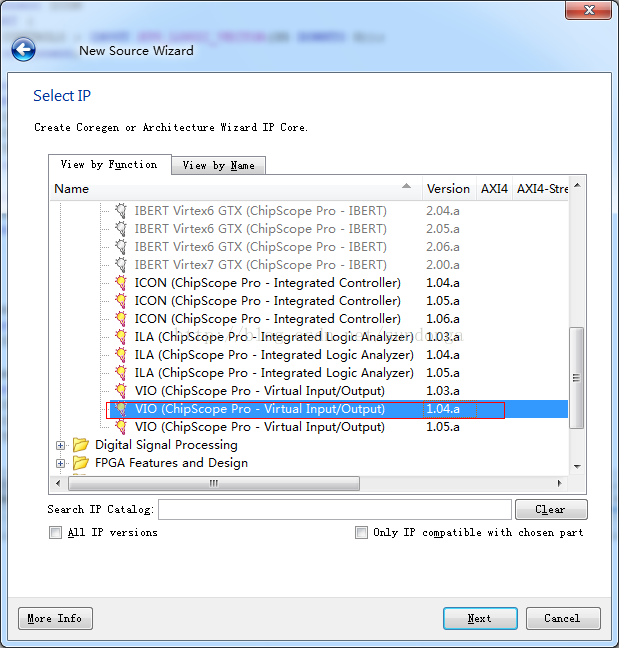

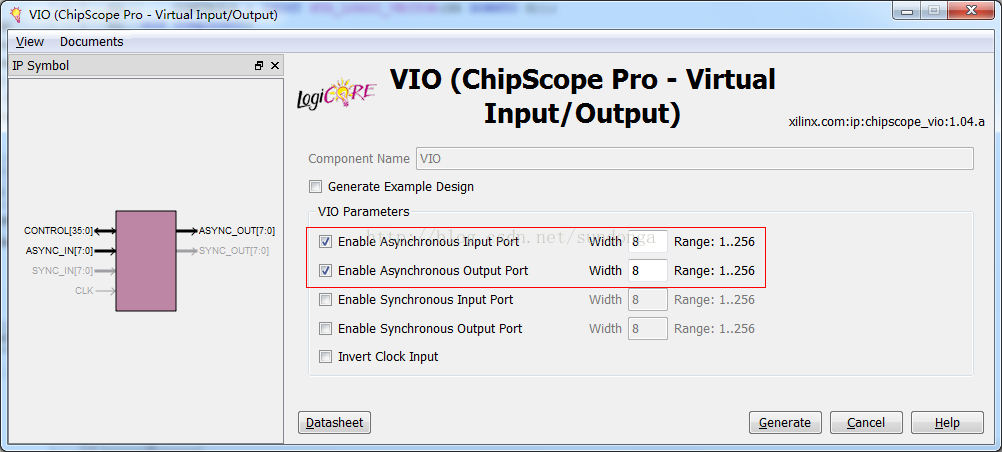

4. 添加VIO核,设置8个虚拟输入,8个虚拟输出,8个输入接加法器的8位,输出只用了一位接reset。

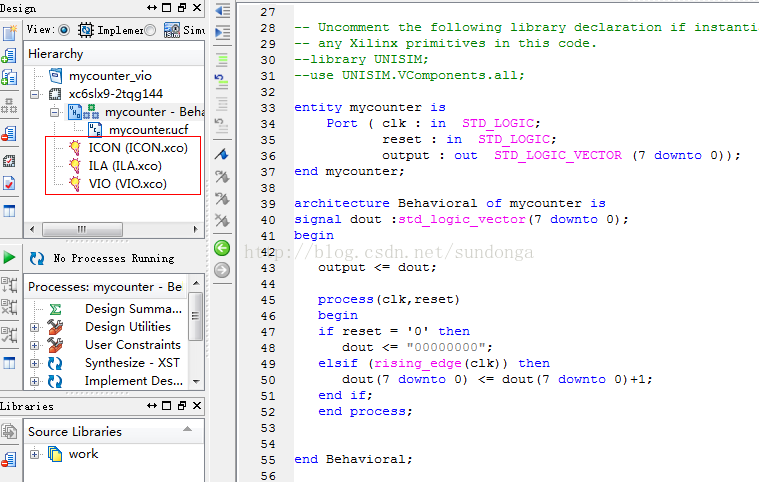

5. 添加完IP核之后,可以看到工程中除了自己原来写的VHDL和UCF文件,多了三个IP核文件。

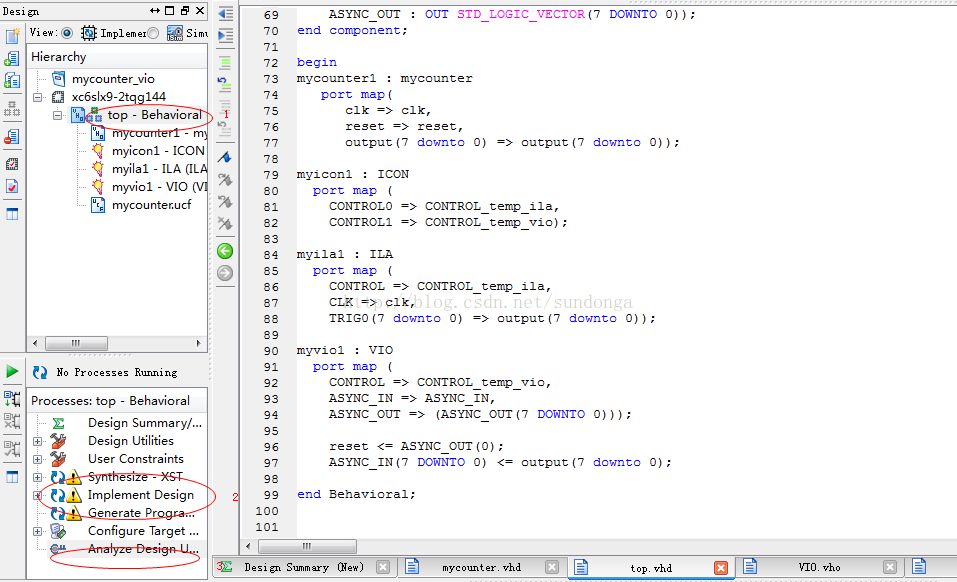

6. 之后写一个顶层文件,将mycounter/ICON/ILA/VIO全部例化、连接。然后综合布线,最后点击左下角Analyze Design Using ChipScope。

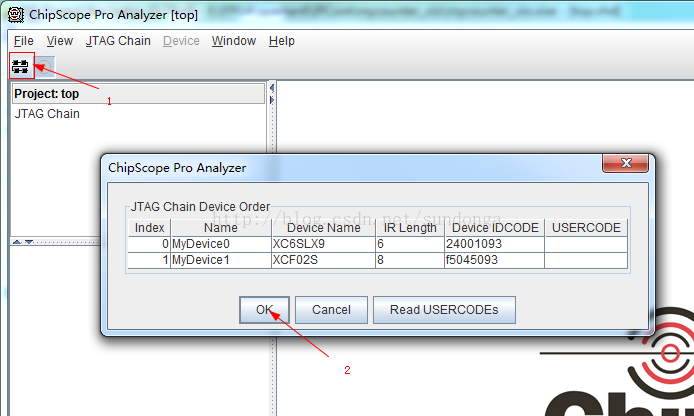

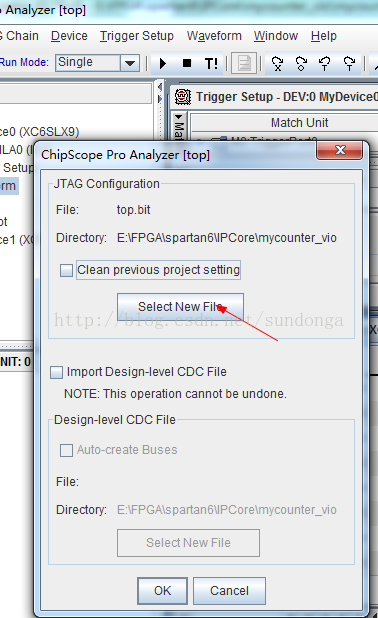

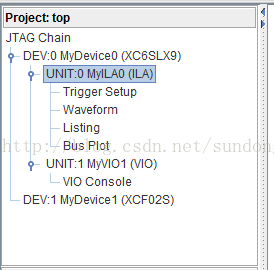

7. 开发板上电,按图中所示找到设备,加载.bit文件。会看到Device0中有ILA核和VIO核。

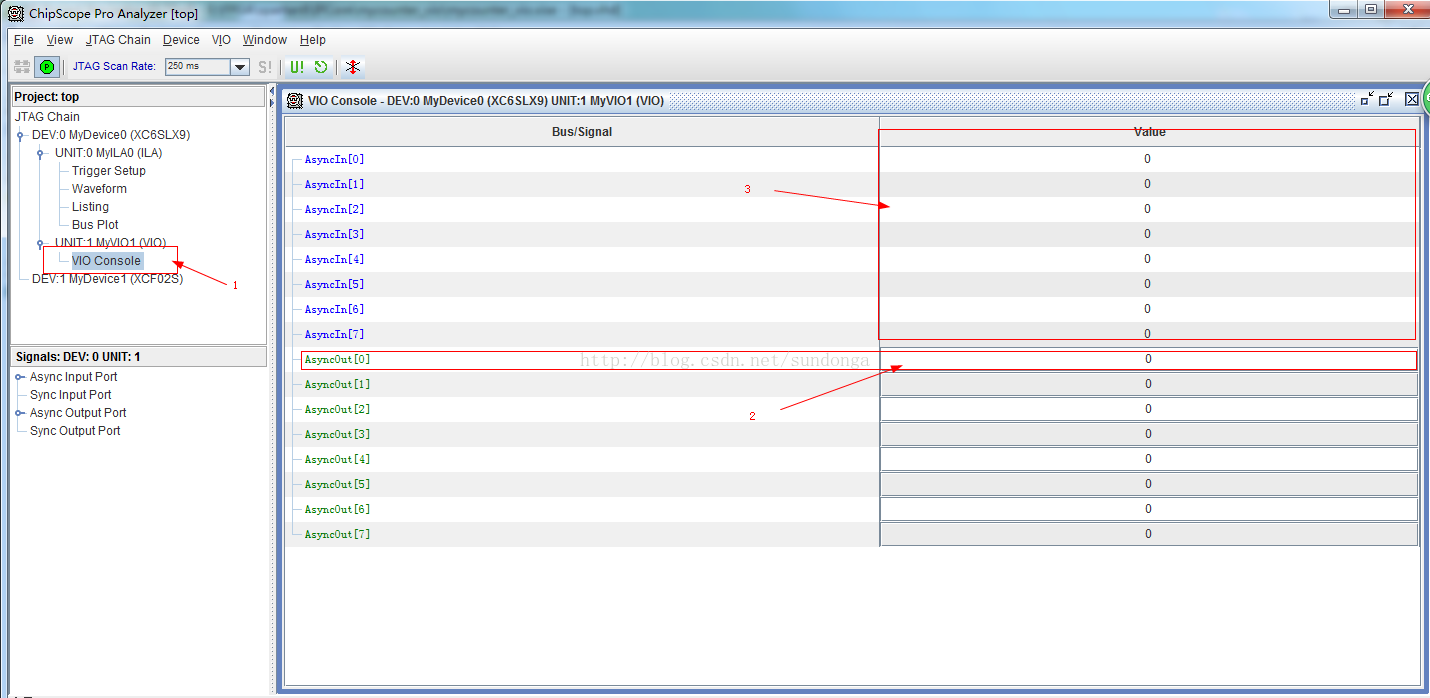

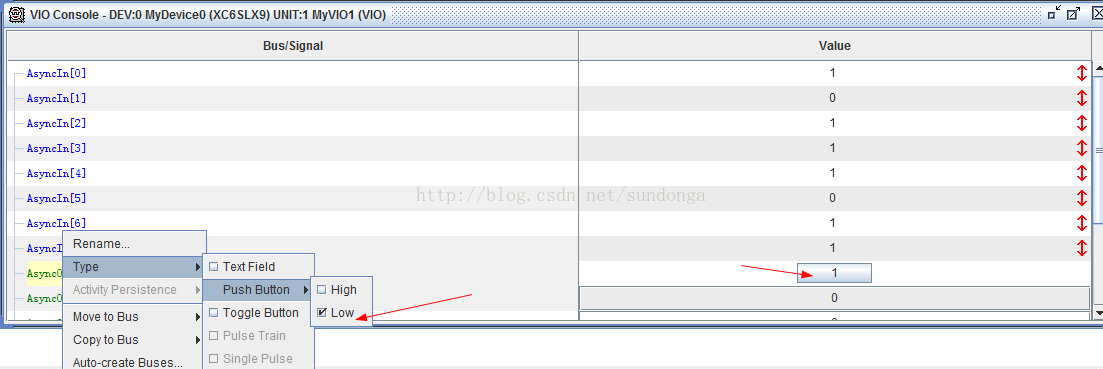

8. 双击左侧VIO核,设置虚拟输入AsyncIn[0]为按钮,即可实现虚拟的reset键。

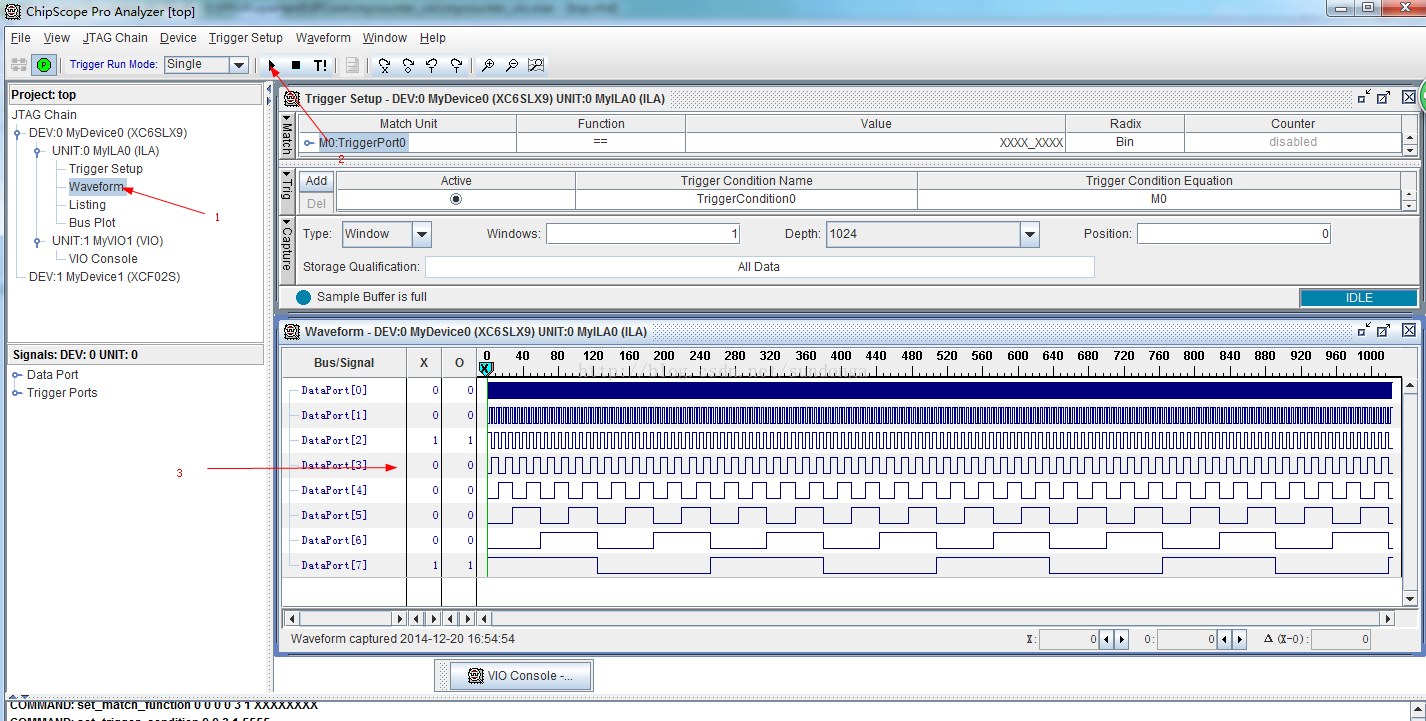

9. 双击左侧Waveform,再单击上方小三角可抓波形,当然我这里没有设置触发,也可以先设置好触发后再抓波形

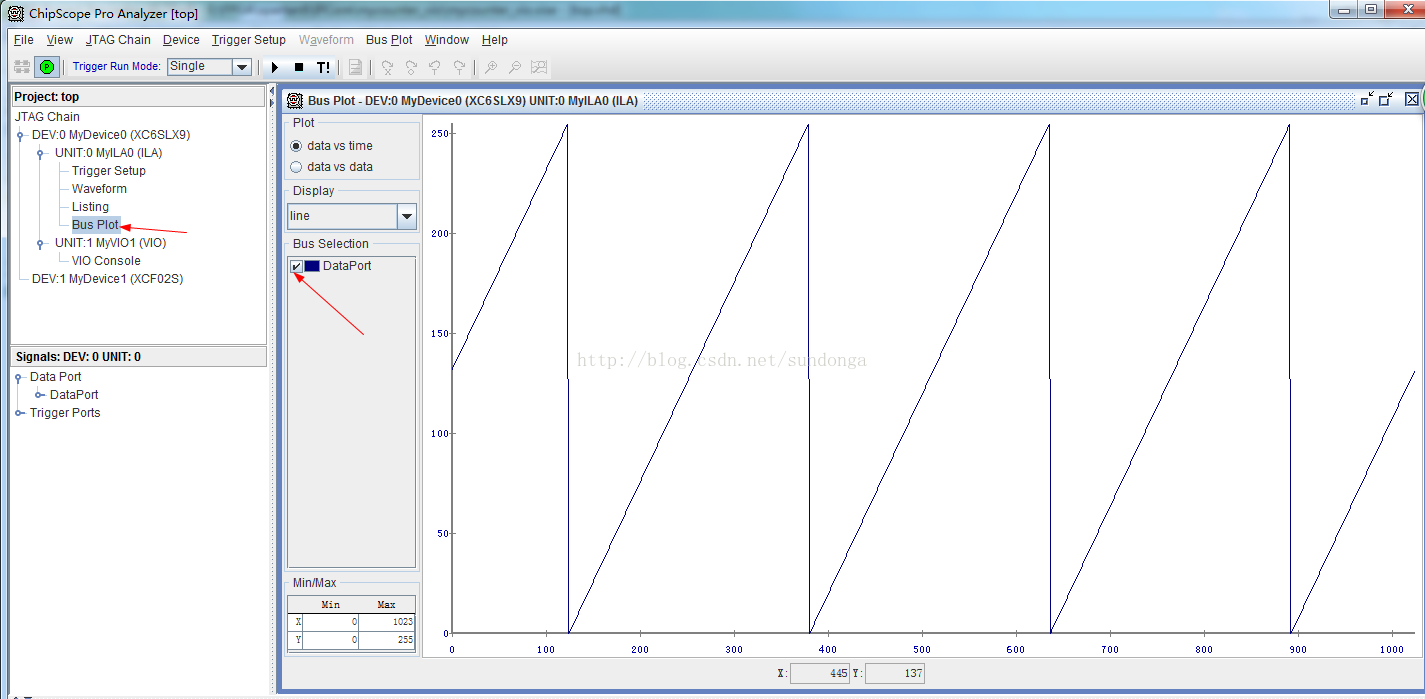

10. 将加法器的输出建立BUS后,可以使用Bus Plot查看,可以看到是0~255的循环,且使用虚拟输入可清0。