IP核——PLL

一、Quartus II创建PLL

1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager

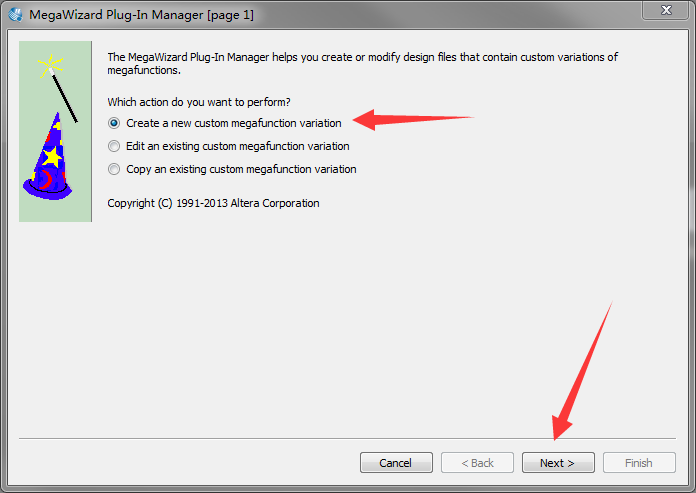

2.弹出创建页面,选择Creat a new custom megafunction variation,点Next

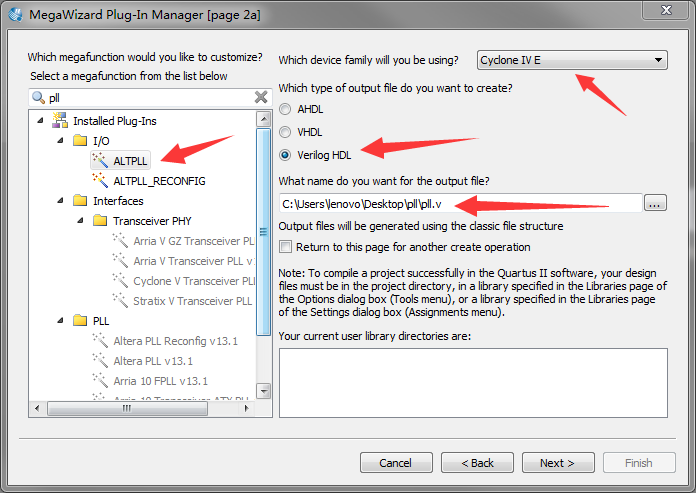

3.选择IP核,可以直接搜索pll,选择ALTPLL,右上方选择器件型号,语言选成Verilog,再填写一下路径名字,点Next,后面就是参数设置了。

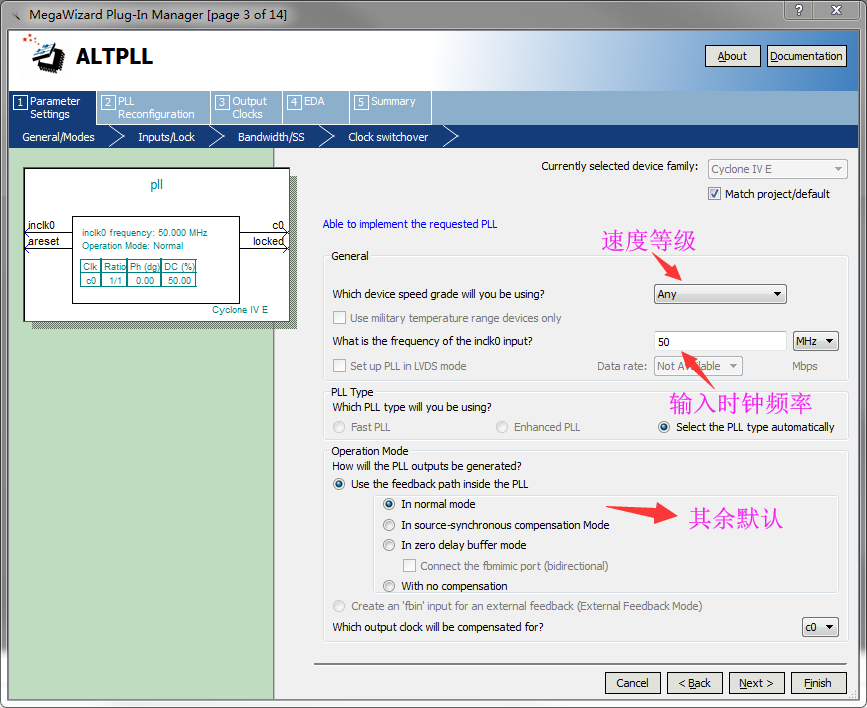

4.设置输入时钟频率,Next

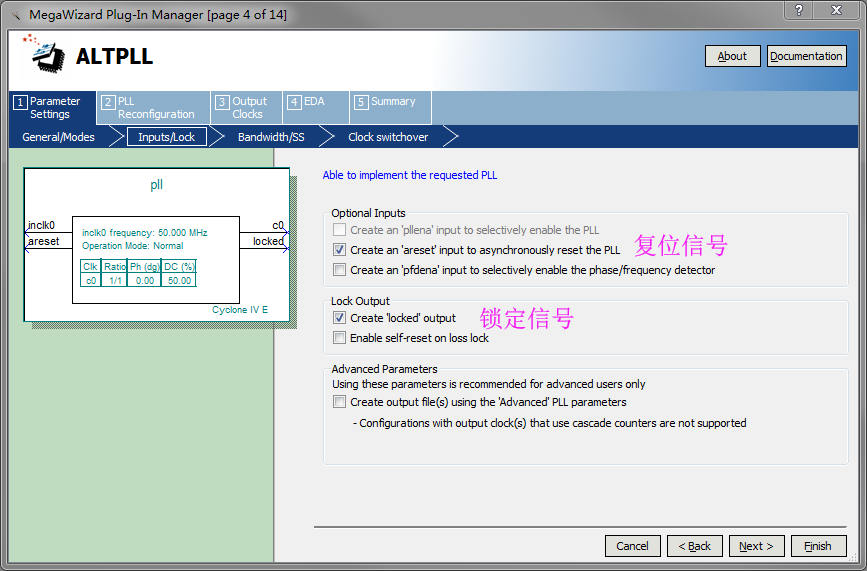

5.复位信号和锁定信号,锁定信号是指为1时,时钟就是稳定输出的状态,一般使用不勾选也行。Next

6.默认,Next

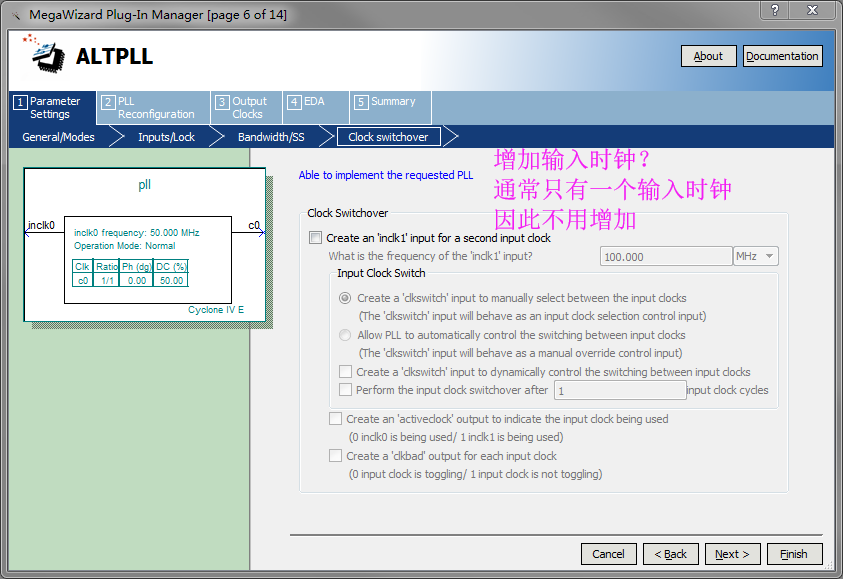

7.增加输入时钟,一般只有一个输入时钟,只用inclk0即可,因此无需增加,Next

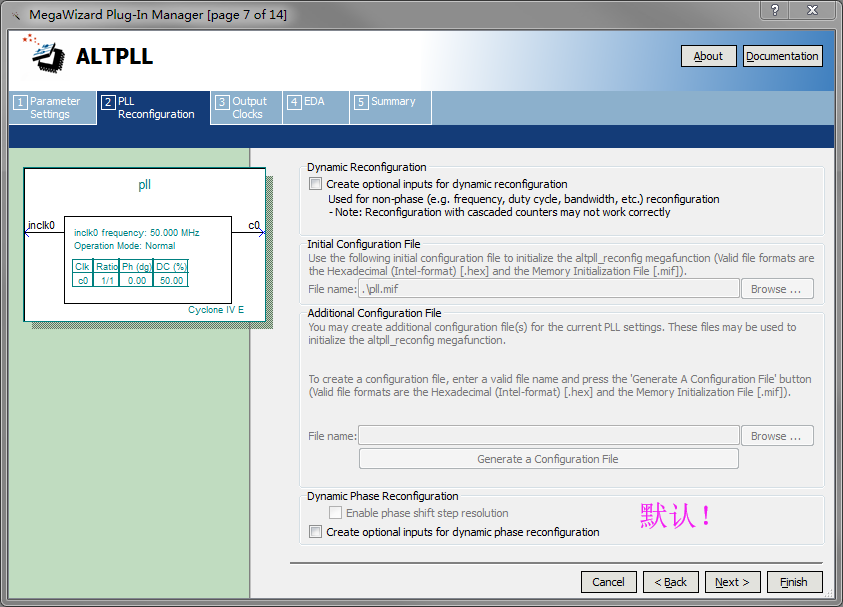

8.默认,Next

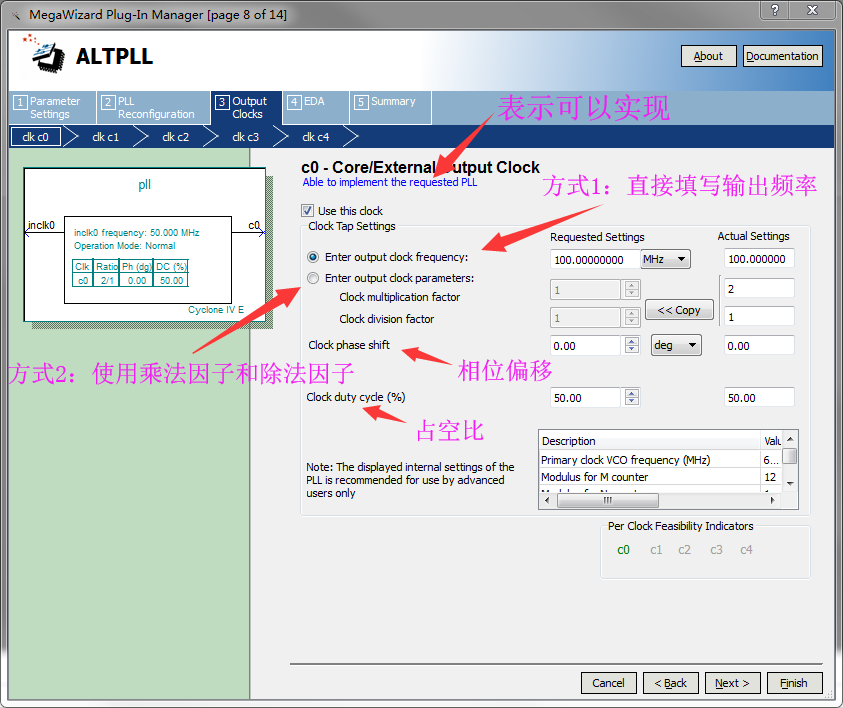

9.设置输出时钟,Next

10.后面是c1,c2,c3,c4,说明总的支持5个输出时钟,我们需要几个填几个就行,Next

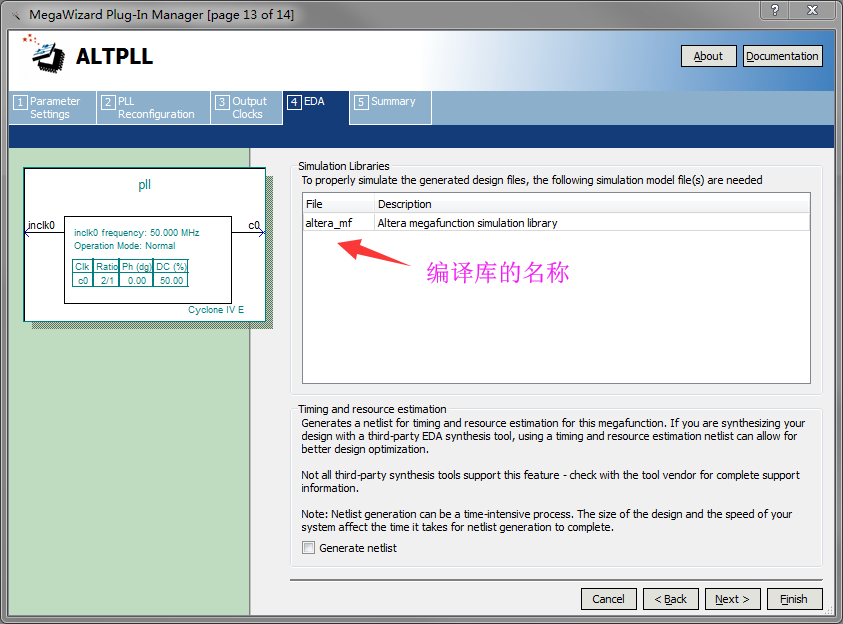

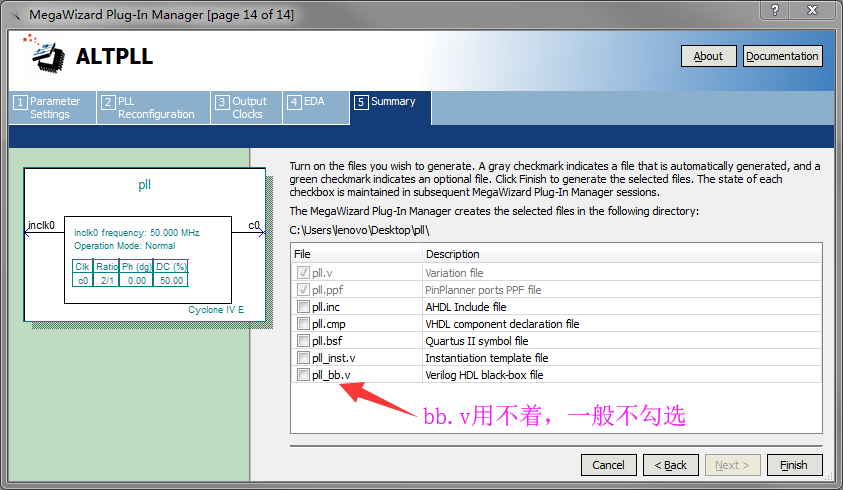

11.告诉你此IP核的编译库是什么,Next

12.输出的文件列表,除了正常IP核,还可以选择例化文件,注意bb.v文件用不到,一般是不勾选的。之后点finish就生成IP核了。

ps

1.Modelsim联合仿真ip核:quartus正常调用Modelsim就行

2.Modelsim独立仿真ip核:上面提示了仿真库名称,该仿真库可以在你的quartus安装目录下搜索到,把它复制出来,和其他文件一起添加到Modelsim中即可。

二、ISE

1.创建

1.创建ISE工程,IP核需要在ISE工程里面进行调用。点击Tools---Core Generator...

2.在新弹出来的界面中创建一个属于IP核的工程:file---new project,并填写文件存储位置和文件名称,一般为ipcore_dir文件夹,点击保存

3.弹出的Part处填写器件的系列、型号、封装以及速度等级,Generation处设置语言为Verilog,点击OK

4.点击文件夹,找到FPGA Features and Design---Clocking---Clocking Wizard,(也可以直接搜索)双击打开,进行参数设置

5.设置模块名和输入的时钟频率,Next

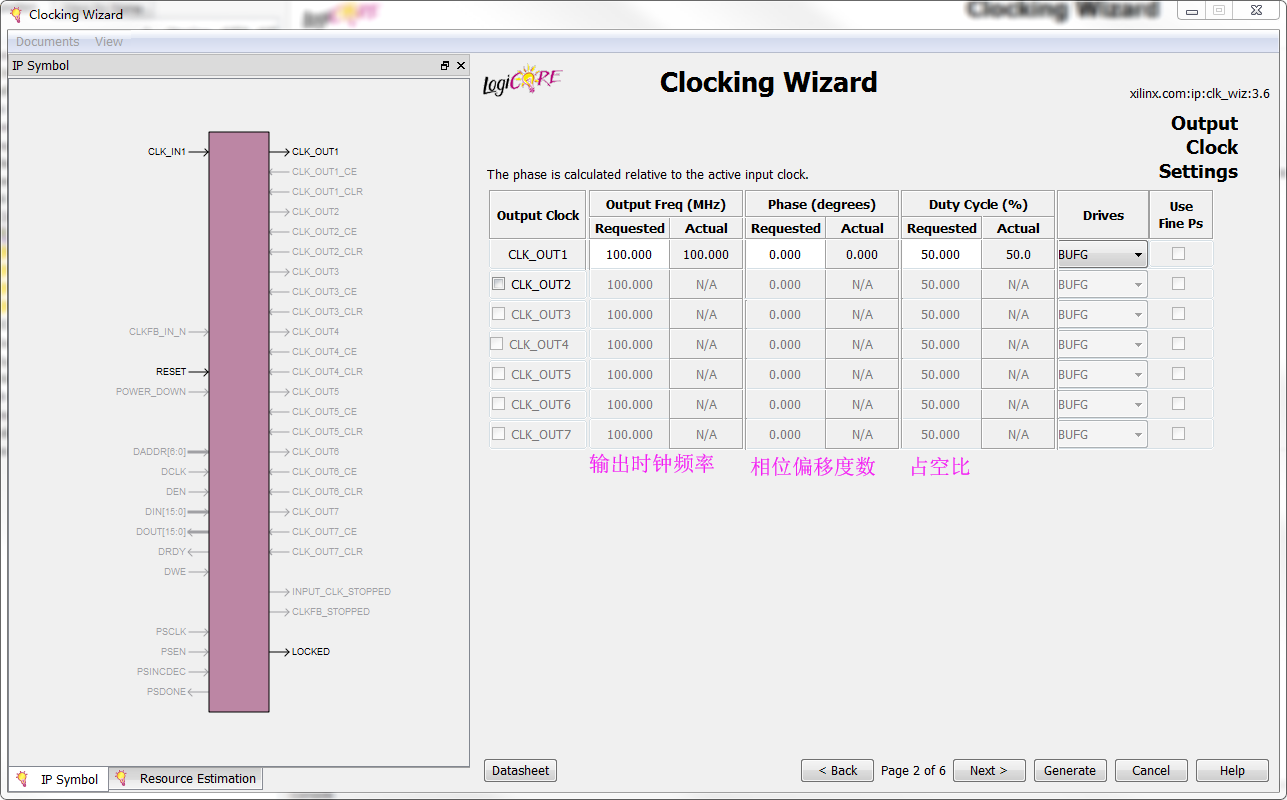

6.设置输出的时钟频率,还可以进行相位偏移度数和占空比,Next

7.设置控制信号,一般的设计不勾选就行,Next

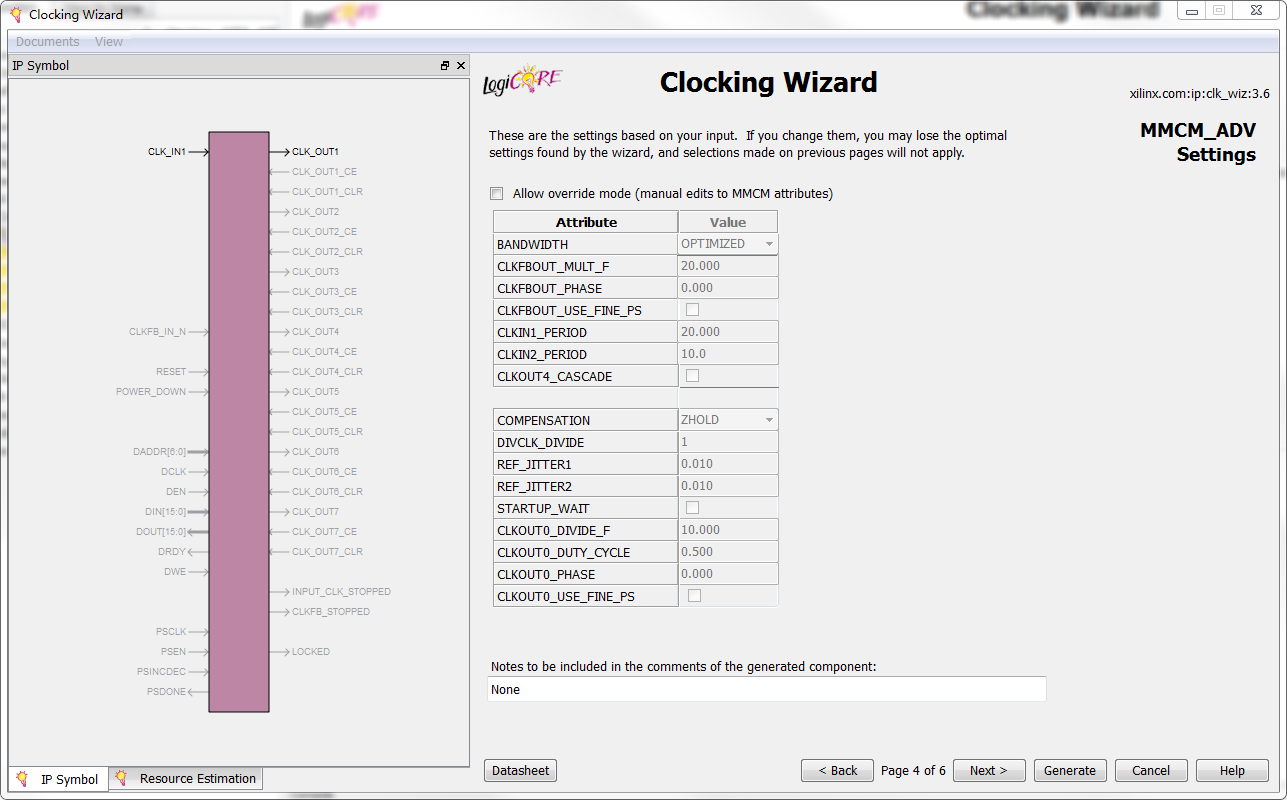

8.预览页面,Next

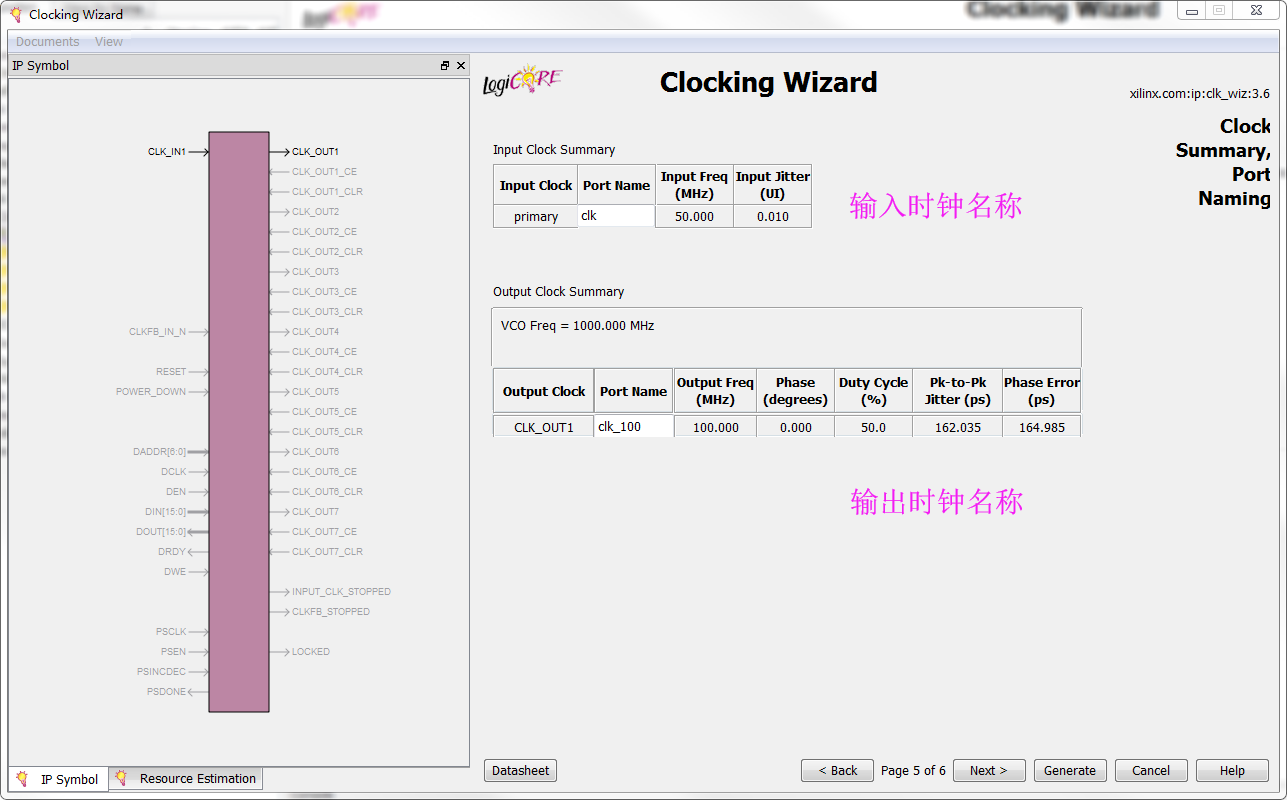

10.设置输入时钟和输出时钟的信号名称,Next

11.预览页面,点击Generate,静静等待IP核生成,生成后关闭弹出的readme.pll页面,关闭Core Generator页面。

2.使用

1.需要把创建好的IP核添加到工程中,创建IP核会生成一些文件,主要看以下三种文件:

①pll.v:IP核模块,看看里面的接口就行,不需要关注具体的代码含义

②pll.xco:进行内部优化后的IP核模块,我们把这个添加到工程中

③pll.veo:此IP核的例化模板文件

2.选中工程,添加pll.xco

3.选中工程,右键New Source,选中Verilog Test Fixture,填写名称和保存路径,一路Next。

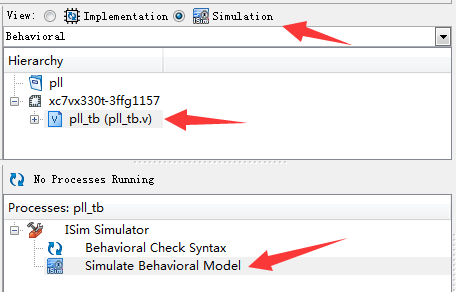

4.主页面切换至Simulation,可以看到生成了testbench文件,但是没有时钟驱动,我们设计一下。

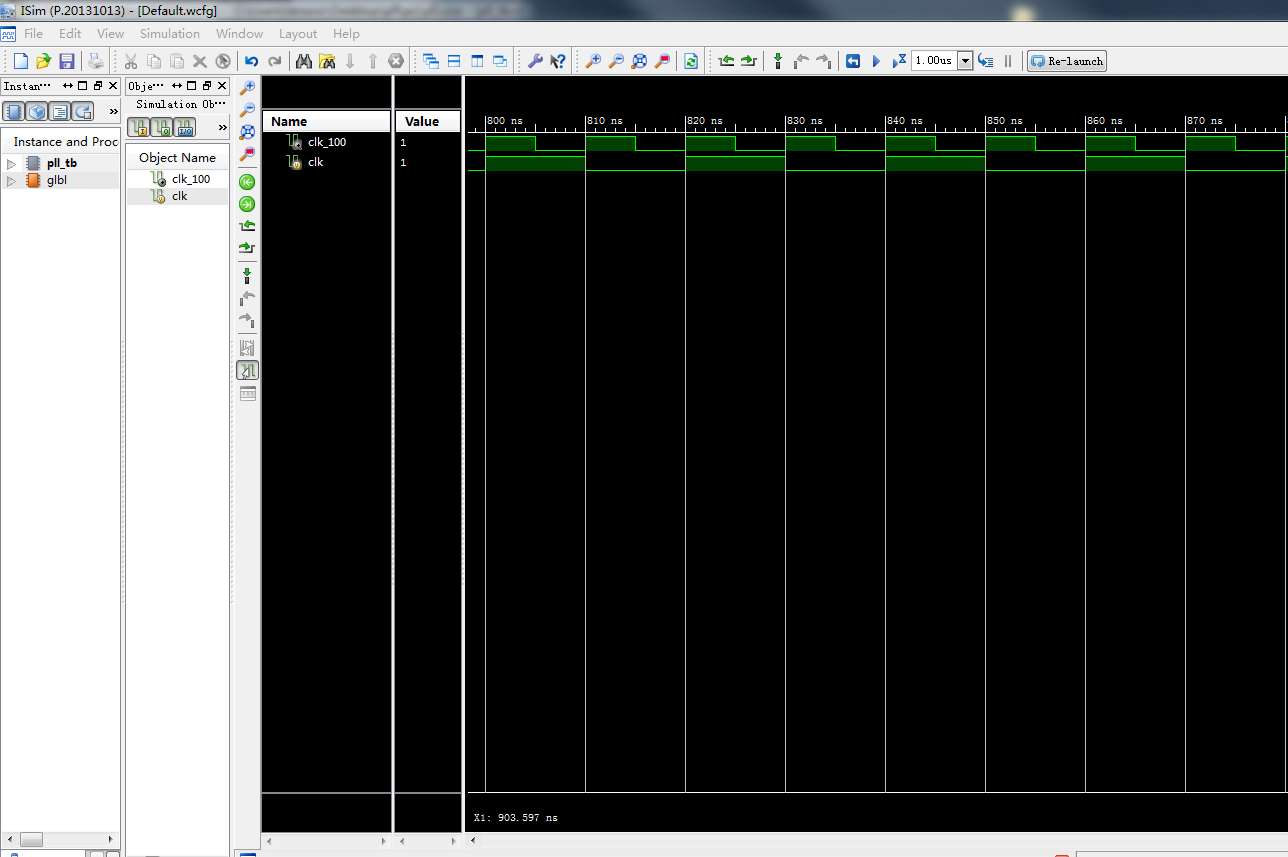

5.点击一下tb文件,下面进程栏中就出现了仿真工具,我们点击Simulate Behavioral Model,即可打开Isim,自动出波形。

PS:ISE也可以直接关联Modelsim,但有ip核的话还需要一个编译库的漫长过程,详细情况可自行百度。