校招基础——低功耗

低功耗简单知识

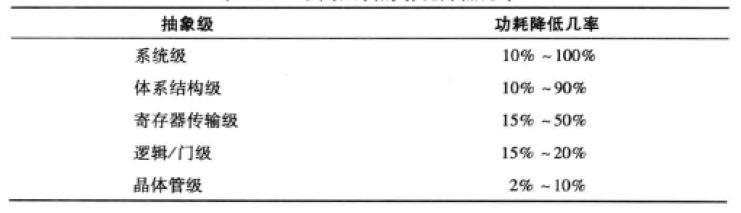

1、低功耗分类?

分为静态功耗和动态功耗;

- 静态功耗是指漏电流功耗,是电路状态稳定时的功耗,其数量级很小;

- 动态功耗是指电容充放电功耗和短路功耗,是由电路的翻转造成的;

2、低功耗技术

公式:Power = K*F*C*V^2,功率=系数*频率*负载电容值*电压平方

(1)控制工作频率

- ① 门控时钟,降低活动因子,降低时钟网络和D触发器功耗;

- ② 可变频率时钟,设置合适频率时钟;

(2)减少电容负载

- ① 使用更小的逻辑门;

- ② 降低平均逻辑开关频率,减少每个时钟沿处的逻辑开关总数,减少连线网络;

- ③ 数据隔离技术,使能才用,不使能不用;

- ④ 格雷码编码,减小翻转次数;

- ⑤ 尽量避免使用这些上拉电阻和下拉电阻;

(3)降低工作电压

- ① 多电压、动态电压频率调节DVFS、不工作关闭部分电源;

- ② 并行结构或流水线设计;

- ③ 动态处理温度补偿;

3、下列属于常用的低功耗设计方法是(ABCD)

A、时钟门控

B、多电压设计

C、降低电源电压

D、动态电压和频率调节

4、下面降低功耗的方法中,属于降低静态功耗的有(ADE)(不一定对)

A:门级电路的功耗优化

B:多阈值电压

C:门控时钟电路

D:操作数分离

E:多个供电电压

5、ASIC中低功耗的设计方法和思路(不适用于FPGA)

合理规划芯片的工作模式,通过功耗管理模块控制芯片各模块的Clock,Reset起到控制功耗的目的。

- 门控时钟(Clockgateing):有效降低动态功耗

- 多电压供电:通过控制模块的电压来降低功耗

- 多阈值电压

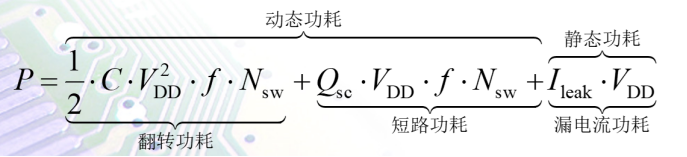

6、CMOS的功耗组成是什么样的?

功耗组成:动态功耗和静态功耗组成;

(1)动态功耗:开关功耗和短路功耗;

- 开关功耗:电路在开关过程中对输出节点的负载电容充放电所消耗的功耗。

- 短路功耗:电源到地的直流导通电流

(2)静态功耗:主要是漏电流引起的功耗

低功耗设计

1. 功耗源

浪涌、静态功耗和动态功耗是主要的三个功耗源。

浪涌电流指的是器件上电时产生的最大瞬时输入电流,在应用中也称为启动电流,其与设备相关。例如基于SRAM的FPGA就有很突出的浪涌电流,因为上电时需要这些器件的配置过程,从外部存储器下载数据配置编译资源等。

静态功耗又称为待机电流产生的功耗。待机电流指的是关断主电源或者系统进入待机模式下产生的电流。与浪涌电流类似,其与电子元件的电气特性密切相关。静态功耗也包括电路中由晶体管的漏电流所导致的功耗。

动态功耗或者开关功耗是门电路输出切换时,由逻辑转换所引起的功耗。

动态功耗在大规模IC设计中占主要地位,典型的应用中动态功耗占用了总功耗的80%。

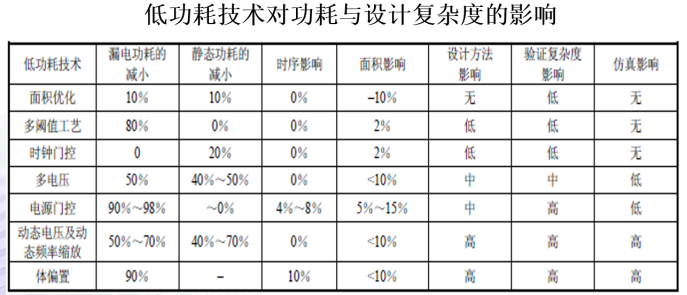

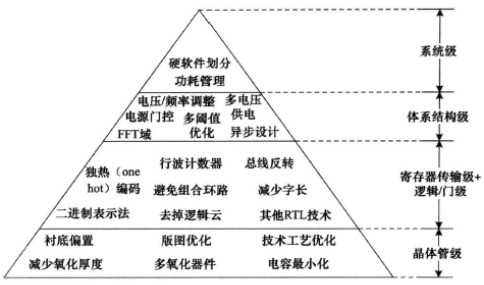

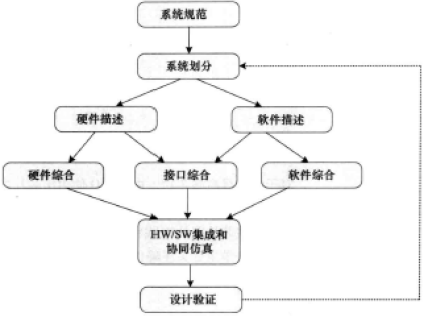

2、抽象层次降低功耗

降低功耗应当在所有的设计层次上进行,即在系统级、逻辑级和物理级。层次越高对功耗降低就可能越有效。如图所示2.1为在不同设计层次上降低功耗的各种设计技术。

图2.1 层次级低功耗设计

图2.2 功耗降低概率对比

2.1 系统级低功耗技术

在设计系统前,必须对系统及其性能以及功耗的目标作以考虑。

- 片上系统方法:针对纳米级芯片,由于I/O与内部使用电压不同,一般为3.3V,使得其占到总功耗的50%以上,如果系统中包含多块芯片,芯片与芯片之间 的连接会消耗大量的功耗,因此从片上系统主要关注降低功耗,缩减面积以及降低成本。

- 软硬件划分:在嵌入式系统中,有些功能适用于硬件实现,有些功能适用于软件时间。比如通行算法具有高度的递归特性,非常适合硬件实现,可以减少大量功耗。因此,在设计前将系统划分为硬件和软件部分反复优化得到最佳方案。

图2.3 软硬件划分流程

- 低功耗软件:通过对软件设计的优化,如语言设计上的优化,减少运行空间和时间复杂度。

- 处理器选择:不同的处理器,对于功耗的改善不一样,采用适合处理所有要求的数据位宽的处理器。

2.2 体系结构级降低功耗技术

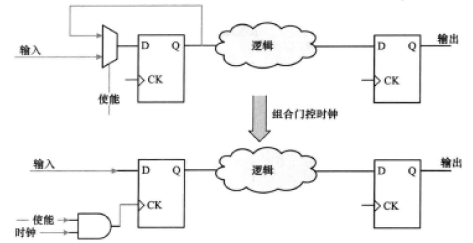

高级门控时钟:在同步数字系统中,时钟分布贡献了整个数字开关功率的绝大部分。在许多情况下可以通过门控时钟将绝大部分不使用的电路关闭掉。

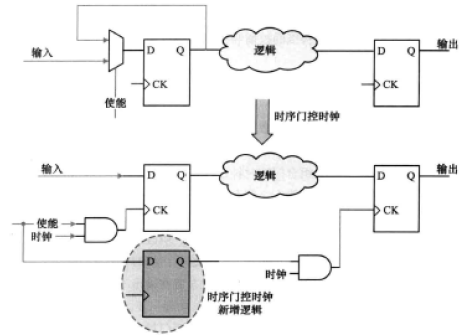

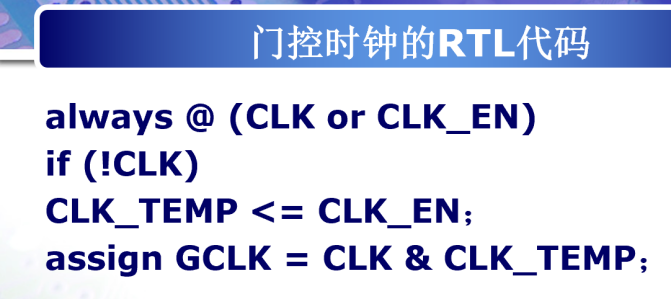

门控时钟,以前讲过组合门控时钟,即图2.4所示,由于其是在输出不变时使触发器的时钟失效,因此他可以降低5%-10%的动态功效,而时序门控时钟在不影响设计功能的情况下改变设计结构,其能够减少连接到带有门控时钟的寄存器块的设计部分的冗余切换。如图2.5所示为时序门控时钟。

图2.4 组合门控时钟

图2.5 时序门控时钟

不过时序门控时钟电路最大的挑战在于识别出流水线上“多余的”或者“不关心”的状态,一旦这一工作完成,将会大大将降低功耗,约15%-25%,不过在多于16触发器情况下使用更好。

- 动态电压调节:在对频率不敏感的应用阶段中降低时钟速率以及供电电压可以在性能稍微降低下大幅降低功率。DVFS算法调节。

- 基于缓存的系统体系结构:对于大多数DSP应用,FFT算法要求频繁访问系统存储器数据,这样的存储器效率不高,因此在系统存储器与处理器之间增加缓存,可以大大提高FFT能效。

- 异步设计:时钟消耗过大,有些 系统中会将时钟移除,通过例如握手接口进行交互。

3. 寄存器传输级降低功耗(编写设计规则)

在进行系统设计时,RTL完成时80%的功耗已经确定。后端流程不能解决所有功耗问题,因此需要系统性地直接从RTL中或从映射结果中寻找降低功耗的机会,微架构和RTL代码风格对于动态与静态功耗有极大的影响。

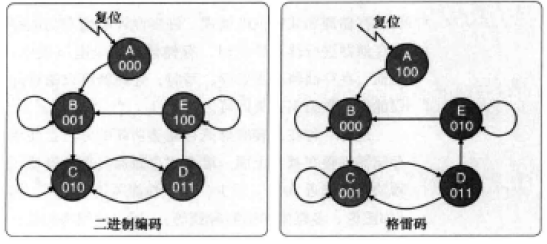

- 状态机编码与解码:在各种状态机编码类型中,格雷码是最适合降低功耗设计的。对于二进制编码而言,在状态转换过程中可能有多个触发器发生翻转,这种状态转换过程比每次只有一位触发器变换的格雷码要消耗更多的能量。而且格雷码编码 也消除了状态中组合等式存在毛刺的风险。如图3.1所示,为分别用二进制与格雷码进行设计编码的状态机。

图3.1 低功耗设计中二进制编码与格雷码对比

除此之外,对大型状态机进行分解,形成功能相同的两个子FSM,之间 并没有相互转换关系,这样由于在一个FSM激活时可以关闭另一个FSM,从而降低功耗。状态机详细设计 :状态机设计.docx

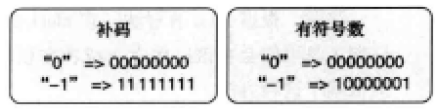

- 二进制数表示法:在大多数应用中,用补码表示二进制数往往比用有符号数更长使用,然而对于某些特殊应用,在切换过程中有符号数更具有优势,如图3.2为分别用补码和有符号数表示0和-1。对于某些只使用积分器进行求和的应用,补码表达法在0到-1的转变发生时所有位发生变化 ,而有符号位只有两个位发生,因此可以降低功耗。

图3.2 补码与有符号数

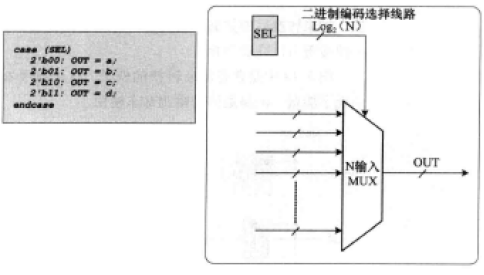

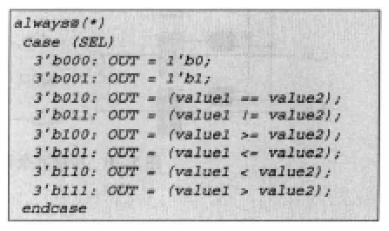

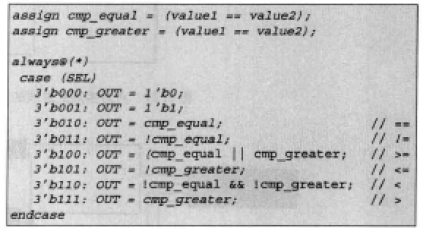

- 独热码多路器:在RTL中有许多使用多路器的方法。“case”语句、“if”语句和状态机一般都可以实现这种效果。表示多路器 (MUX)最常用的方法是使用二进制编码,如图5.17所示。

图3.3 MUX选择线路的二进制编码

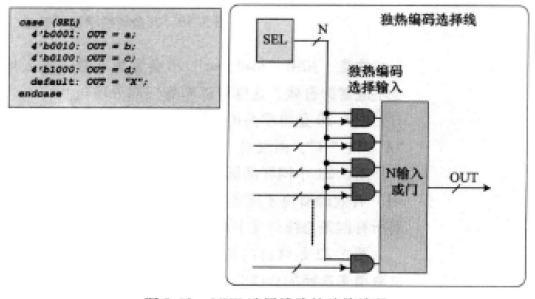

注意,如果MUX的每个输入是多位总线,就会产生明显 的开关过程 ,由此产生功耗 。如果对“case”条件进行编码时按照图3.4所示中的独热码方式,输出会更快更稳定,而且在初期就能将未选中的总线掩藏起来,因此实现 低功耗效果。

图3.4 独热编码case语句

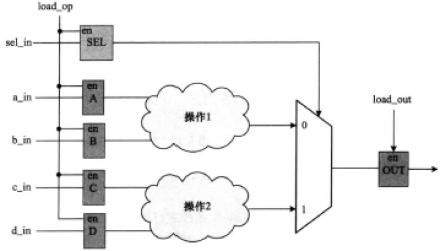

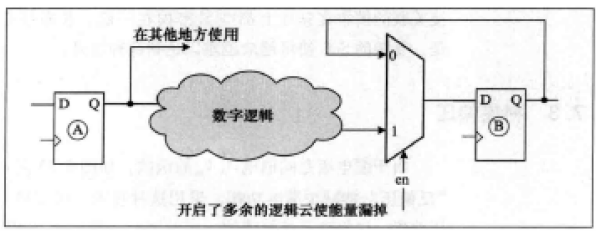

- 除掉多余的转换:在没有设置默认状态的情况下,总线数据常常会发生没有意义的转换。如果转换后的数据未被真正采样,那么它就是多余的,将这样的转换去掉显著可以降低功耗。如图3.5所示,系统读入所有的输入消耗了能量,但是输出却可能并没有用到,因此这里面就有多余转换的部分。

图3.5 冗余转换消耗了能量

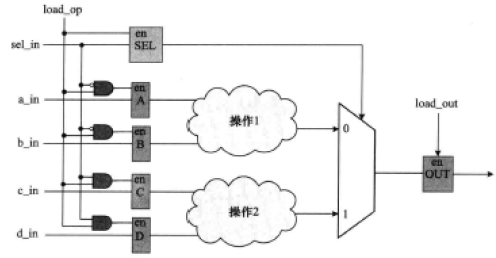

如图所示,如果load_out无效,则load_op也应该无效才不会有输入却没有输出,这样才可以节省功耗。除此之外,只有SEL为0时,AB才有效 ,CD无效,这里又会浪费部分功耗。如图3.6所示为压缩后的电路图。

图3.6 使能ABCD,使其可以有效时输出

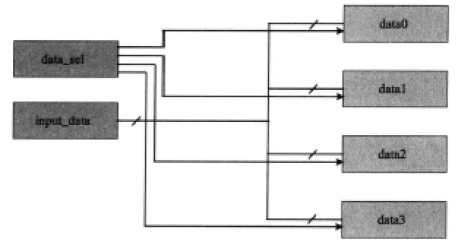

除此之外,在点对多点式的数据总线切换过程中,也会发生冗余转换的现象,如图3.7所示

图3.7 点对多式总线转换

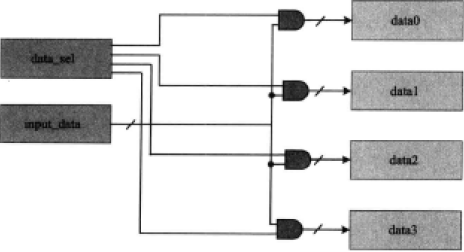

由于data_sel如果并不是全部有效的话,会导致部分数据data输入消耗功耗,却无用。如图3.8为更改后的电路。

图3.8 点对多式数据总线转换

- 资源共享:对于涉及较多的算术运算设计,如果有同样的操作在多处使用,必须避免相应的运算逻辑在多个位置重复出现。如图3.9是没有进行资源共享的例子。

图3.9 未进行资源共享

使用重复的逻辑会增大面积,而且增加功耗。如图3.10所示,通过 先 将其运算出来在进行复用可以 同样实现上述功能且使用资源和面积更小。

图3.10 逻辑复用后的代码

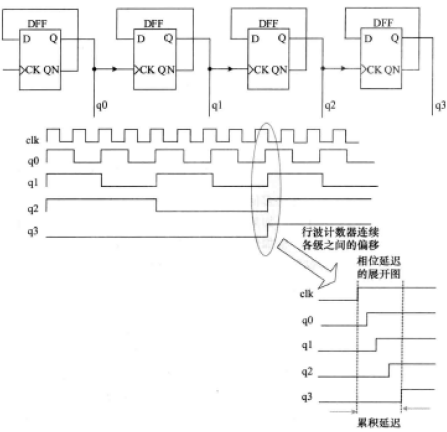

- 行波计数器降低功耗:行波计数器的 缺点和限制在时钟一栏已经讲解,不过它用于降低功耗是十分有效的。下面仔细讲讲其面对的挑战与可能解决的办法和降低功耗效果。

如图3.11所示,为行波计数器的电路结构和导致时钟偏移的时序图。

图3.11 四级行波计数器中的相位延迟

由于越高级的输出相位偏移累加越多,在时钟进行过程中计数器可能会产生不正确的值,产生坏的影响。例如下图3.12所示计数过程,数据由于 延迟 会从0111先变化为0110,0100,0000,最后才回变化为1000,而不是干净的直接变化为1000。

图3.12 计数器由于延迟变化

在许多的使用环境中,这种效应是在课接受 范围内的,是因为行波是快速发生的。比如驱动发光二极管,但是在用于驱动多路选择器或者索引指针时,就会有很大的问题。

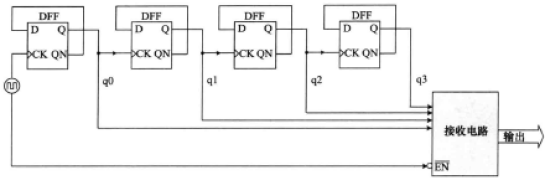

通过对输出数据进行时钟低有效输出,可以 避免行波计数器中毛刺的产生,如图3.13所示。

图3.13 避免毛刺产生的行波计数器

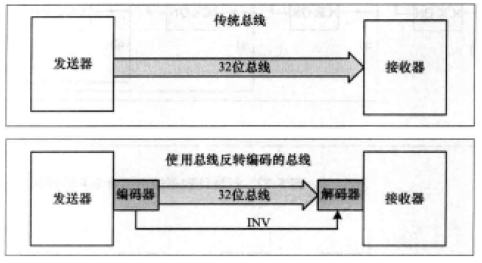

- 总线反转:在当前数据和下一个数据之间的汉明距离大于N/2(N是总线宽度)时,就将下一个数据反向后传输,以减少总线上 出现的转换后的位数量,这就是总线反转编码。针对减少大容量总线上的转换次数很有效。如图3.14所示。

图3.14 总线反转编码

如图3.15是反转后与未反转的数据转换对比图,可以看出反转后的数据转换次数减少不少。

图3.15 反转前后数据转换次数对比

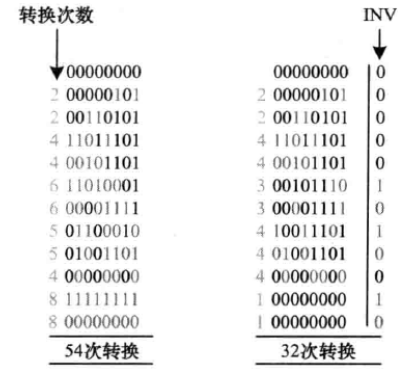

- 高活跃度网络:处理这类设计的思路是将活跃度较高的网络和活跃度较低的网络区分开来,然后将他们置于逻辑云中尽可能深的位置上。如图3.16所示,逻辑云为X1…..Xn和Y的函数,其中X1…..Xn的变化频率较低,Y却是高活跃网络。因此更改逻辑云,将低活跃与高活跃的X、Y分离,这样得到的新逻辑 云规模减少。

图3.16 逻辑云活跃度划分

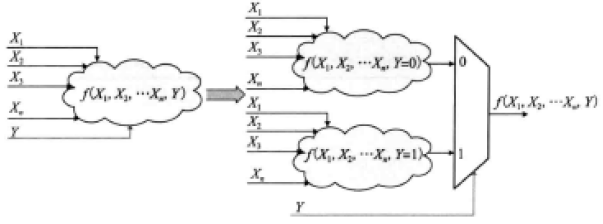

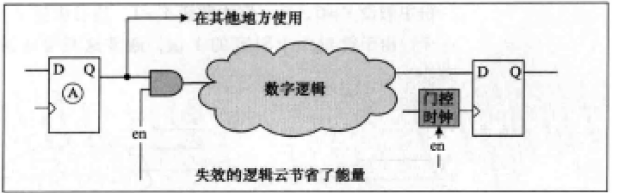

- 启用和禁用逻辑云:在操作大规模逻辑云(宽加法器、乘法器等)时,往往在需要的时候才将其打开。(加上使能信号进行控制)如图3.17所示,只有触发器B得到使能信号,逻辑云一直打开,并不会停止,后图中将使能信号控制逻辑云启动,从而降低逻辑云不使用时功耗。

图3.17 使能逻辑云