校招基础——IC设计

1、IC设计的基本流程

1.需求分析 分析用户或市场的需求,并将其翻译成对芯片产品的技术需求。(Office)

2.规格制定 芯片需要达到的具体功能和性能方面的要求。 (Office)

3.方案设计 根据设计的功能需求和算法分析的结果,设计芯片的构架,并对不同的方案进行比较,选择 性能价格最优的方案。这一阶段可以使用SystemC语言对芯片构架进行模拟和分析。(Office)

4.RTL设计 使用HDL语言完成对设计实体的RTL级描述。(Gvim)

5.功能仿真 验证RTL代码的质量和性能。(Modelsim/Questasim、NC-Verilog、VCS)

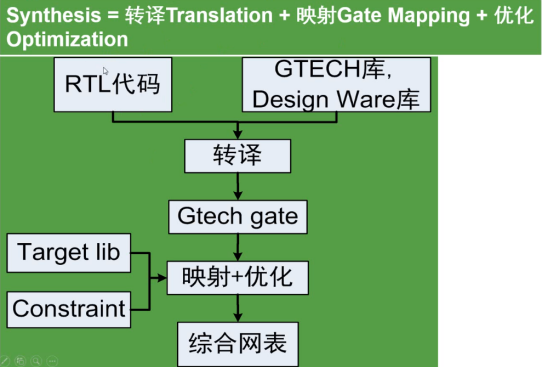

6.DC综合 从RTL代码生成描述实际电路的门级网表文件。(DC)

7.网表仿真 对综合产生的门级网表进行验证,如STA和形式验证。Candence、NC-Verilog、VCS)

8. 布局布线。后端设计对综合产生的门级网表进行布局规划、布局、布线,生成生产用的版图。(Candence)

9.版图后验证。根据后端设计后取得的新的延时信息,再次验证设计是否能够实现所有的功能和性能指标。

10.芯片生产。生产在特定的芯片工艺线上制造出芯片。

11.芯片测试。对制造好的芯片进行测试,检测生产中产生的缺陷和问题。

2、IC设计的基本的知识

(1)DFT

DFT,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT常用的方法是:在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。

(2)布局规划

布局规划就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。

(3)CTS

时钟树综合,简单点说就是时钟的布线。由于时钟信号在数字芯片的全局指挥作用,他的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。

(4)布线

这里的布线就是普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的0.13um工艺,或者说90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟道长度。

(5)寄生参数提取

由于导线本身存在电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压的波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。

(6)版图物理验证

对完成布线的物理版图进行功能和时序的验证,验证项目很多,如LVS验证,简单说,就是版图与逻辑综合后的门级电路图的对比验证。

3、什么是CTS?为什么要CTS?

概念:CTS,clock tree synthesis,即时钟树综合。

作用: (1)均衡时钟skew;

(2)增加驱动能力;

(3)减小功耗

4、代码覆盖率

覆盖率是对仿真进度的评估,其中代码覆盖率是客观的,功能覆盖率是主观定义的。

代码覆盖率常常被拿来作为衡量测试好坏的指标,必须达到80-90%。Modelsim代码覆盖率能报告出:

(1)语句(statement)

(2)分支(branch)

(3)条件(condition)

(4)表达(expression)

(5)信号翻转(toggle)

(6)有限状态机(fsm)

代码覆盖率分析包括以下这些内容:

(1)语句覆盖率

(2)条件覆盖率

(3)路径覆盖率

(4)有限状态机覆盖率

(5)触发覆盖率

(6)表达式覆盖率

5、什么是DFT?为什么要DFT?

概念:DFT,design for test,即可测试设计的意思;

作用:(1)提高产品质量;(2)缩短产品上市时间;(3)降低测试成本

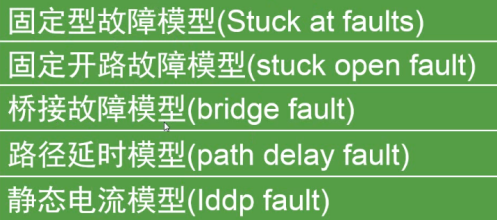

6、DFT有哪些故障模型?

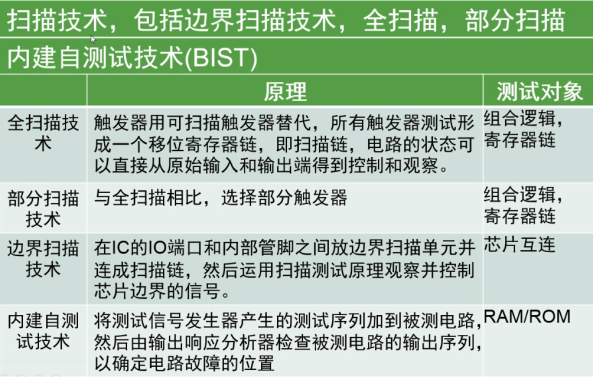

7、DFT技术有哪些?

8、DC综合的流程是怎么样的?

9、是否接触过自动布局布线?请说出一两种工具软件。自动布局布线需要哪些基本元素?(2012士兰微)

1、读入网表,跟foundry提供的标准单元库和Pad库以及宏模块库进行映射;

2、整体布局,规定了芯片的大致面积和管脚位置以及宏单元位置等粗略的信息;

3、读入时序约束文件,设置好timing setup菜单,为后面进行布局布线做准备;

4、详细布局,力求使后面布线能顺利满足布线布通率100%的要求和时序的要求;

5、时钟树综合,为了降低clock skew而产生由许多buffer单元组成的“时钟树”;

6、布局布线,先对电源线和时钟信号布线然后对信号线布线,最大程度地满足时序;

常用的工具有Synopsys的ASTRO,Cadence的SE,ISE,Quartus II也可实现布局布线。

10、下面设计流程中的步骤有哪些完全不需要功能仿真激励?(ABD)

A、综合

B、静态时序分析

C、功耗分析

D、形式验证

11、4bit二进制计数器,其翻转率(Toggle Rate,每时钟都翻转按照100%来算)大约是?(B)

A、0.125

B、0.47

C、0.3

D、0.64

解析:(1/8+1/4+1/2+1)/4 = 0.47,最低位是肯定会翻转的,以此类推。