数电(4):组合逻辑电路

组合逻辑电路:

- 任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

- 电路中不包含存储单元。

一、编码器

1、普通编码器

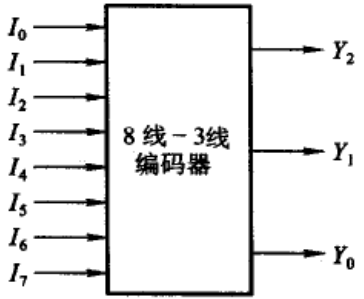

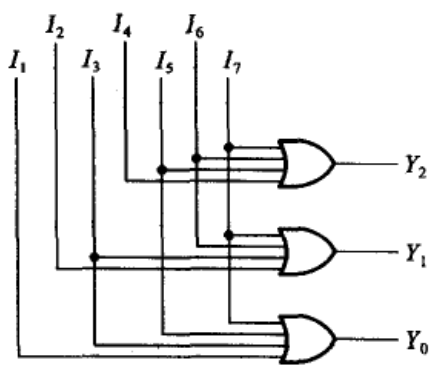

例如:3位二进制编码器(8 - 3编码器)

(1)框图

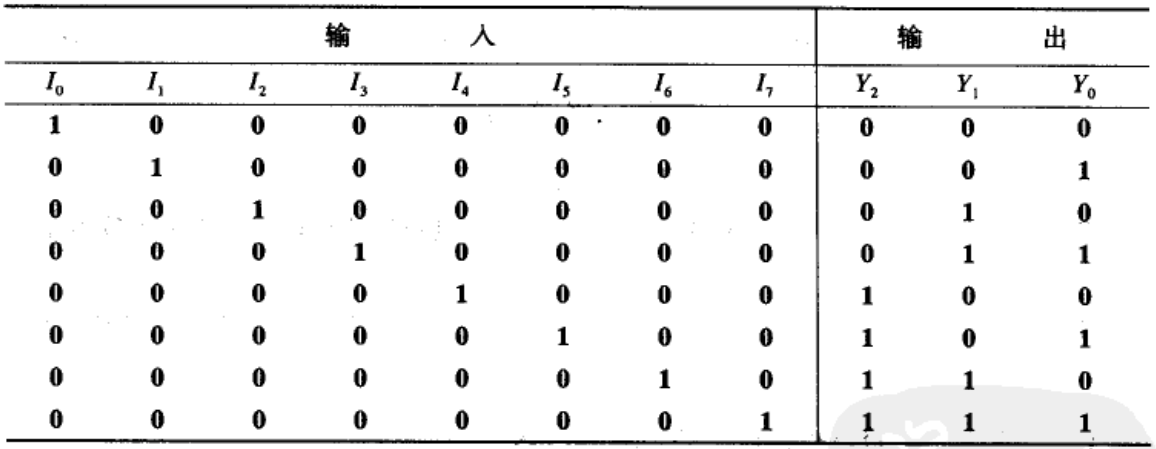

(2)真值表

类似:输入是独热玛,输出是顺序二进制

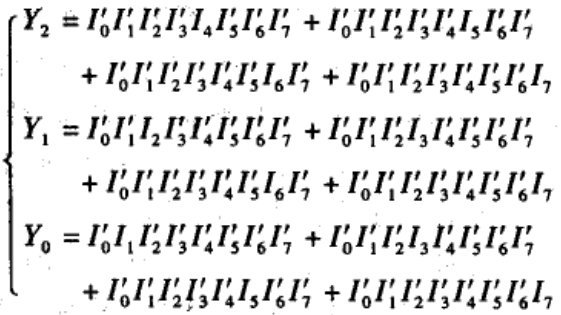

(3)逻辑式

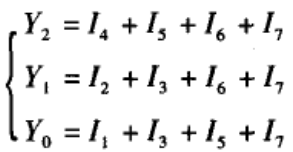

(4)逻辑式化简

(5)逻辑图

2、优先编码器

略

二、译码器

1、二进制译码器

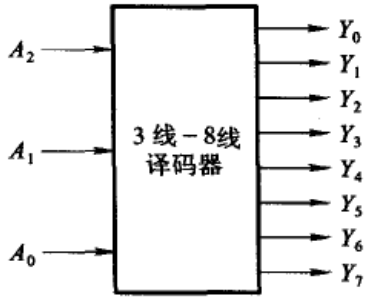

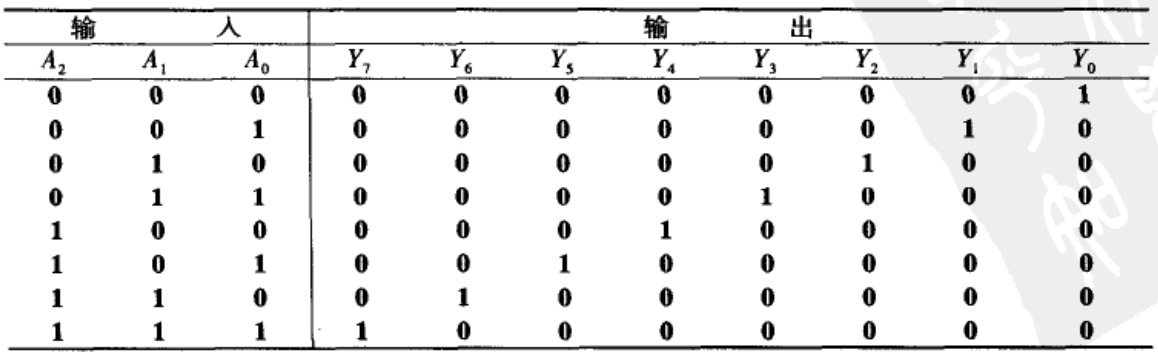

例如:3位二进制译码器(3 - 8译码器)

(1)框图

(2)真值表

类似:输入是顺序二进制,输出是独热玛。

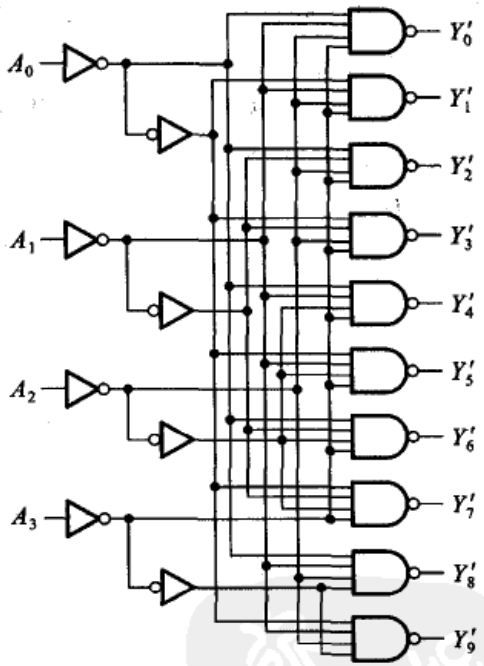

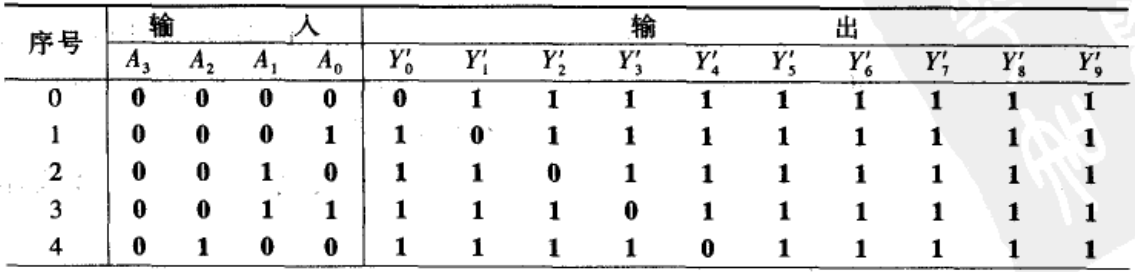

2、二 - 十进制译码器

即输入是4位的顺序BCD码,输出的是独热玛再取反,超出的是伪码,拒绝翻译。

3、显示译码器(数码管)

略

三、数据选择器(多路开关)

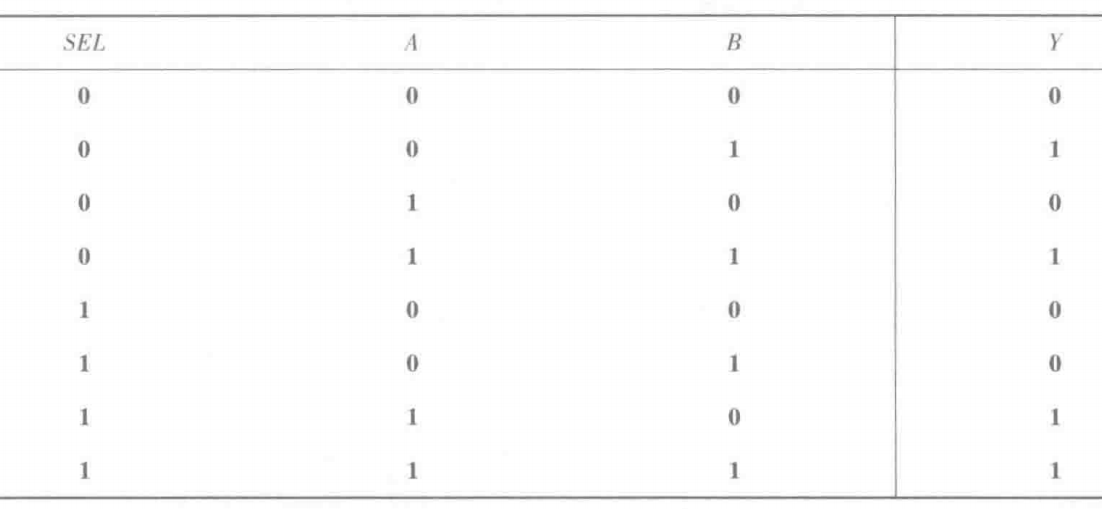

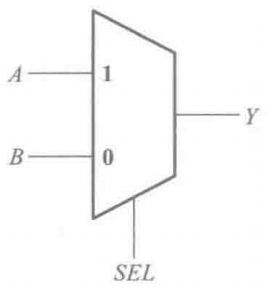

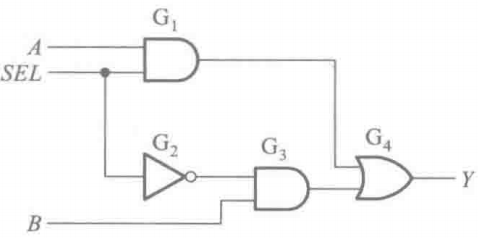

1、二选一

①逻辑式:Y = SEL · A + SEL' · B

②真值表

③符号图

④门电路

2、4选1

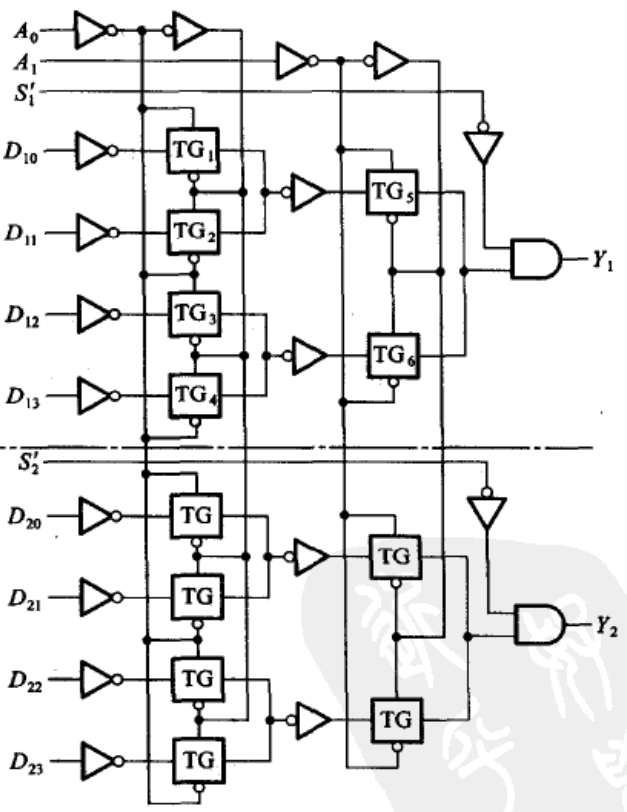

- (1)D是 data_in,Y是输出数据 data_out。

- (2)A1、A0 是地址 addr。

- (3)S1'、S2'是 CS 片选。

以前大二的时候不懂,现在一目了然,不就这么个玩意儿吗?

3、例题

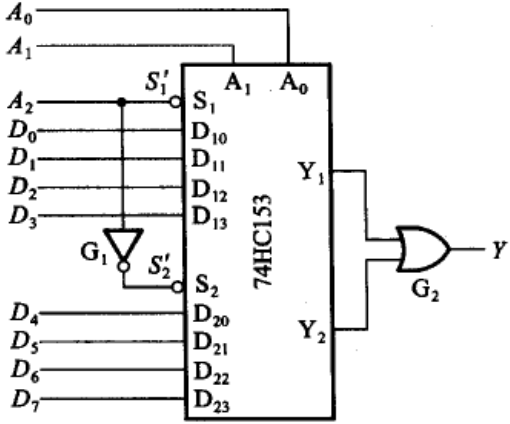

用两个带附加控制的 4-1 数据选择器组成一个 8 -1 数据选择器。

思路:两个 4-1 的 2 位地址位要共用,然而 8-1 必须要 3 位地址,所以再将两个 4-1 的片选 S 合并成最高的地址位

四、加法器

1、1位加法器

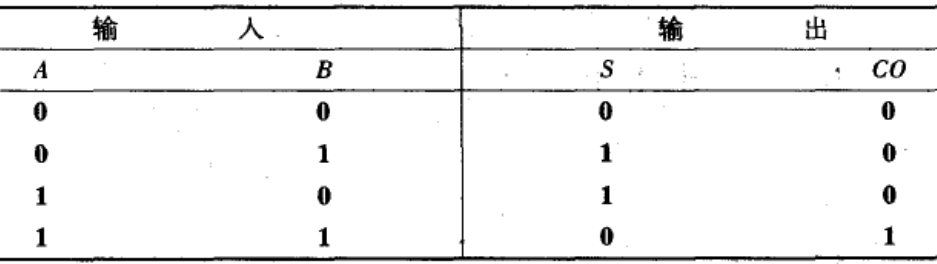

(1)半加器:不考虑来自低位的进位。

例如:A加B等于S,进位是CO

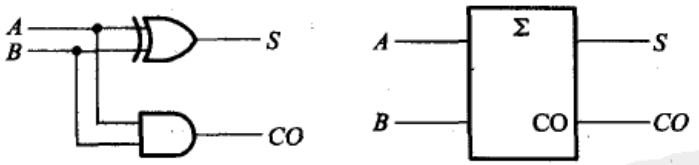

①逻辑式

S = A ⊕ B (没看错,就是异或)

CO = A · B

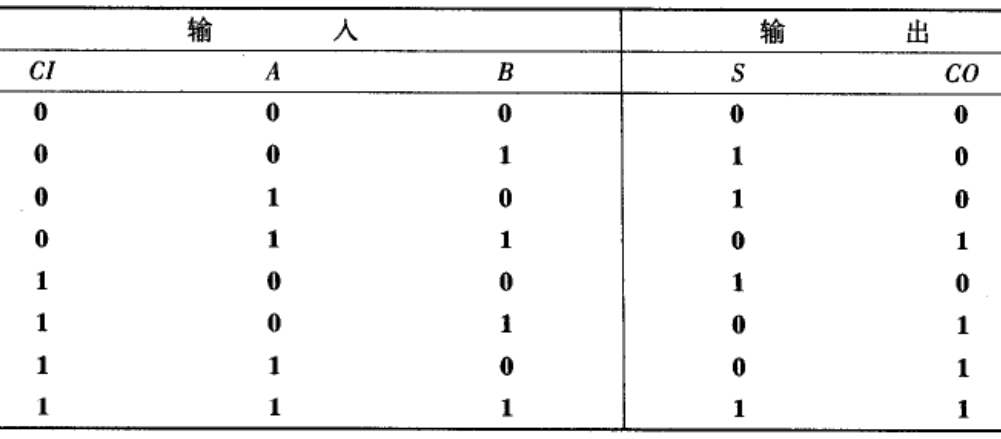

②真值表

③逻辑图

(2)全加器:考虑来自低位的进位

2、多位加法器

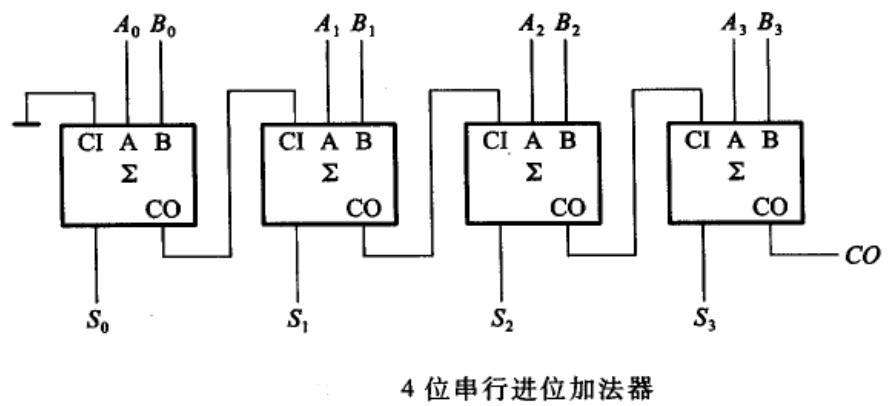

(1)串行(行波)进位加法器

说白了就是正常人类做算术题的加法器,从低到高,考虑进位。

(2)超前(快速)进位加法器

通过逻辑电路实现的得出每一位全加器的进位信号,无需再从低到高传递进位信号。

- 优点:运算时间缩短。

- 缺点:复杂程度增加。

说白了,正常人类难以手动做出来,别看了,看了也不会考。

五、数值比较器

就是比较数值的大小。

1、1位比较器

- A>B,可化为:AB' = 1。

- A<B,可化为:A'B = 1。

- A=B,可化为:A⊙B = 1。

2、多位比较器

必须自高而低的逐位比较,高位相等时继续判断下一位,和正常人类思维一样。

六、竞争 - 冒险

1、现象和原因

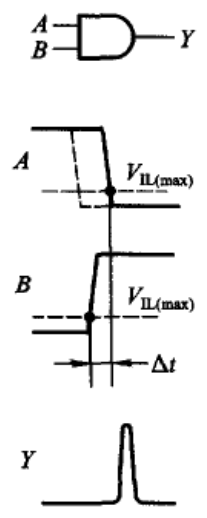

(1)电压毛刺(噪声)

Y=AB,原先 A=1,B=0,变成A=0,B=1时,由于各种原因,二者的变化完成时间不一致,B先变化完成,A后变化完成,这个时间差为△t,这时 Y (考虑了门电路的传输延时时间)就产生了极窄的尖峰脉冲,或称为电压毛刺,是系统内部的一种噪声。

(2)竞争

门电路两个输入信号同时向相反的逻辑电平跳变的现象。

(3)竞争 - 冒险

由于竞争而在输出端可能产生尖峰脉冲的现象。

2、检查方法

(1)两个输入信号

只要输出端的逻辑函数在一定条件下能化简成 Y = A+A' 或 Y = A·A‘,则可判定存在竞争-冒险现象。

(2)多个输入信号

- ①计算机辅助分析

- ②实验检查

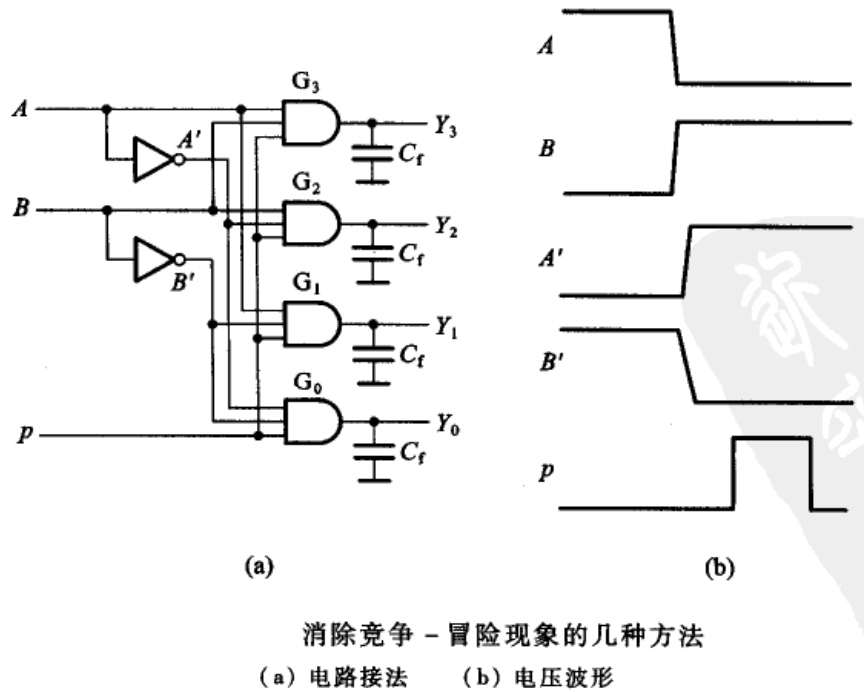

3、消除方法

(1)接入滤波电容

- 优点:简单易行。

- 缺点:增加了输出电压波形的时间,使波形变坏。

(2)引入选通脉冲

即引入一个选通脉冲 p,但最后的输出 Y 也会变成脉冲信号了。其实就可以把 p 看成数据输出的使能信号。

(3)修改逻辑设计(增加冗余项)

例如 Y = AB + A'C = AB + A'C + BC,引入 BC 作为冗余项,A的状态变换就不会再引起竞争-冒险了。

参考资料:阎石. 数字电子技术基础(第5版)[M]. 高等教育出版社, 2006.