DDR2(1):一些预备知识

本次设计其实是从《DDR2(2):Quartus DDR2 IP 官方例程仿真》开始,但是在这之前,需要掌握一些预备知识。

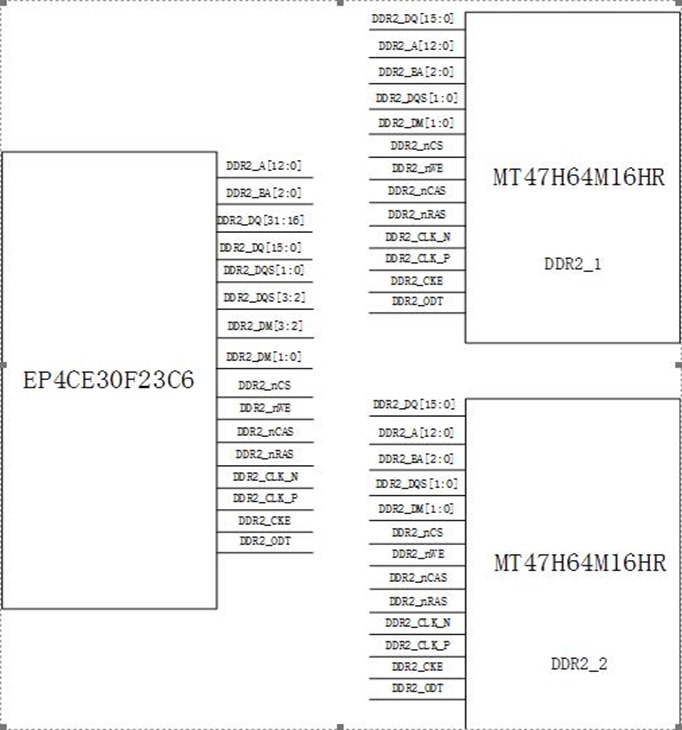

一、电路设计

这方面的知识我比较欠缺,可以看一下小梅哥写的博客《【小梅哥FPGA进阶学习之旅】基于Altera FPGA 的DDR2+千兆以太网电路设计》。其中比较重要的一点,而我之前总是疑惑的地方:双 DDR2 的使用。

很多开发板都带有双 DDR2,一开始我以为就是有两套 DDR2 的接口,不管是管脚还是 IP,都是两套,这种想法是错的!根据小梅哥的这篇博客,原来两片 DDR2 的很多引脚在电路设计上都是合并的,因此在使用它们时,也是例化一个 IP 就行,在设置 IP 时根据实际情况选择合适的参数即可。

从小梅哥的图可以看到,很多信号合并了。例如两片 DDR2, 一片DDR2的存储容量为 1Gb,数据位宽为 16bit,两片 DDR2 共用控制线和地址线,数据线并列组成了 32 位的 2Gb 存储器。双 DDR2 提升了存储容量,最明显的就是地址 ADDR 和数据 DQ 增大了。

二、内存分类

内存有很多种,常见的如下所示:

ROM ( Read Only Memory )是只读存储器,由于断电信息不会丢失,所以 ROM 通常用来存储那些不经常改变的信息。RAM ( Random Access Memory )是随机存储器,存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关,由于断电信息会丢失,所以 RAM 通常用来存储那些短时间使用的程序。按照存储单元的工作原理,随机存储器又分为静态随机存储器(StaticRAM,SRAM)和动态随机存储器( Dynamic RAM,DRAM)。

- SRAM:是利用触发器的两个稳态来表示信息 0 和 1,每个存储单元由六个晶体管组成,不需要刷新;

- DRAM:是利用电容有无电荷来表示信息 0 和 1,每个存储单元由一个晶体管和一个电容器组成,为防止电容漏电而导致读取信息出错,需要有规律地进行刷新;

由于 SRAM 不需要刷新,有更高的速率,所以它常常用于高速缓冲存储器。由于 DRAM 每个存储单元晶体管比较少,有更高的密度,所以它常常用于计算机中的内存。在计算机市场上 DRAM 又可以分为 SDRAM(Synchronous DRAM) 和 DDR SDRAM(Dual Data Rate SDRAM)。

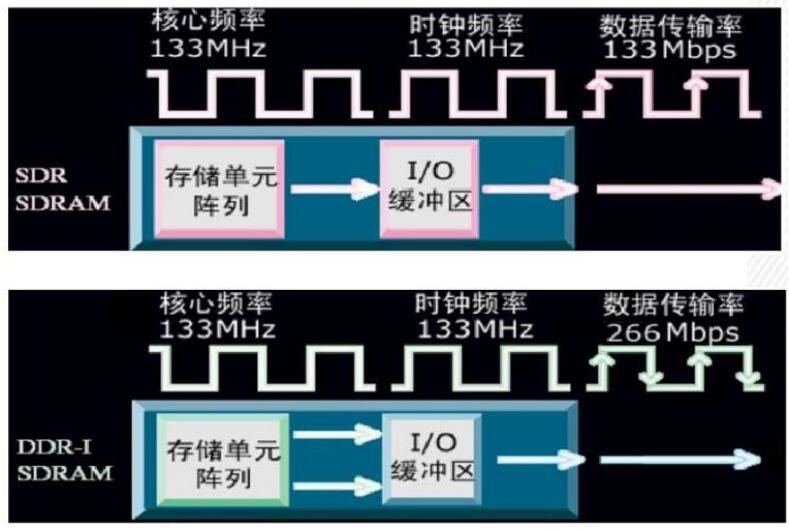

三、SDRAM 和 DDR

SDRAM在之前的博客已经详细记录了,而 DDR 是在 SDRAM 内存基础上发展而来的,DDR 在时钟信号上升沿与下降沿各传输一次数据,这使得 DDR 的数据传输速度为传统 SDRAM 的两倍,如图下所示:

DDR 与SDRAM 的不同主要体现在以下几个方面:

1、时钟

SDRAM 的读写采用的是单一的时钟,DDR 的读写采用的是差分时钟,即 CLK 和 CLK#。CLK# 能起到触发时钟校准的作用。由于数据是在 CLK 的上下沿触发的,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确性,这就要求对 CLK 的上下沿间距要有精确的控制。但由于温度、电阻性能的改变等原因,CLK上下沿间距可能发生变化,此时与其反相的 CLK# 就起到了纠正的作用,CLK 上升沿快下降沿慢,CLK# 则是上升沿慢下降沿快。

2、数据选取脉冲(|DQS)

DQS 是 DDR SDRAM 中的重要信号,其功能主要是用来在一个时钟周期内准确地区分每个传输周期,并使数据得以准确接收,每一块 DDR SDRAM 芯片都有一个双向的 DQS 信号线。

3、写入延迟

SDRAM 的写入延迟是 0,而 DDR 的写入延迟不再是 0 了,DDR在发出写入命令后,DQS 与写入数据要等待一段时间才会送达。这个周期被称为 DQS 相对于写入命令的延迟时间( tDQSS )。之所以会有这样的延迟,这是因为同步,毕竟在一个时钟周期内进行两次传送需要很高的控制精度,它必须要等接收方做好充分的准备才行。

4、突发长度

在 DDR 中,突发长度只有 2、4、8 三种选择,没有了突发长度 1 和全页式突发。之所以去掉突发长度 1 主要是因为 DDR 预读取位数是 2,L_BANK 一次就存取两倍于芯片位宽的数据,所以芯片至少也要进行两次传输才可以,否则内部多出来的数据很难被处理。之所以去掉全页式突发主要是因为PC内存中很难用得上。

5、延迟锁定回路(DLL )

DDR 有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上这两个时钟应该是同步的,但由于实际物理种种原因,所以导致这两个时钟并不同步,这就需要根据外部时钟动态修正内部时钟延迟来实现内部时钟与外部时钟的同步,为此专门设置了DLL,利用DLL可以使内部时钟与外部时钟保持同步。

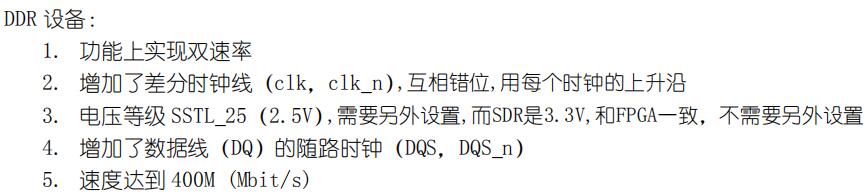

另外,小梅哥补充了一些:

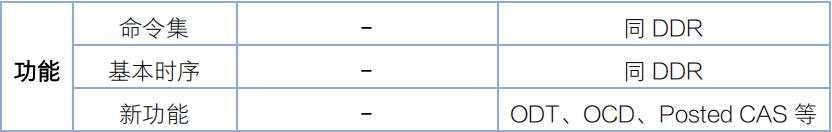

四、DDR和DDR2

DDR2 全称是 Double Data Rate 2 SDRAM,翻译成中文是第二代双倍数据速率同步动态随机存取存储器。它也属于 SDRAM 家族的存储器产品,提供了相较于 DDR 更高的运行效能与更低的电压,是 DDR SDRAM 的后继者,DDR2 和 DDR 一样,也是在时钟信号上升沿与下降沿各传输一次数据,但是最大的区别在于DDR2内存可进行 4bit 预读取。这就意味着 DDR2 拥有两倍于 DDR 的预读系统命令数据的能力,因此 DDR2 具有两倍于DDR的完整的数据传输能力,如图所示:

DDR2与DDR的不同主要体现在以下几个方面

1、片内驱动调校( OCD, Off Chip Driver )

OCD 的主要用意在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值。目的是让 DQS 与 DQ 数据信号之间的偏差降低到最小。

2、片内终结( ODT, On Die Termination)

所谓的终结,就是让信号被电路的终端被吸收掉,而不会在电路上形成反射,造成对后面信号的影响。.

3、前置CAS (Post CAS)

为了解决 DDR 内存中指令冲突而设计的功能,它允许 CAS 信号紧随 RAS 发送,相对于以往的DDR等于将CAS前置了,这样地址线可以立刻空出来,便于后面的行有效命令发出,避免造成命令冲突而被迫延后的情况发生。

知道了DDR2的基本概念,下面我们再来看下锆石开发板的DDR2芯片。以 Micron Technology (镁光科技)公司生产的 MT47H64M16HR-25E DDR2 芯片为例,此芯片的容量为 1Gb,内部结构如图所示:

从该图中可以看出,DDR2 存储单元阵列部分可以说和 DDR、SDRAM基本相同,唯一不同的就是 I/O 输出和输入缓冲区部分了。这部分内容主要包含了差分选取脉冲( DQS )、延迟锁定回路(DLL)和片内终结(ODT )等电路,这和我们前面介绍的是一致的。由于 UDM 和 LDM 只连接到写操作上,所以 DDR2 是支持写入数据屏蔽,并不支持读出数据屏蔽。

另外,小梅哥补充了一些:

五、突发长度的区别

- SDR SDRAM 的突发长度为1、2、4、8、page

- DDR SDRAM 的突发长度为2、4、8 (2bit预读, 2起步)

- DDR2 SDRAM 的突发长度为4、8 (4bit预读,4起步)

关于 2bit 预读、4bit 预读的概念,另外搜索吧,这里不说了。

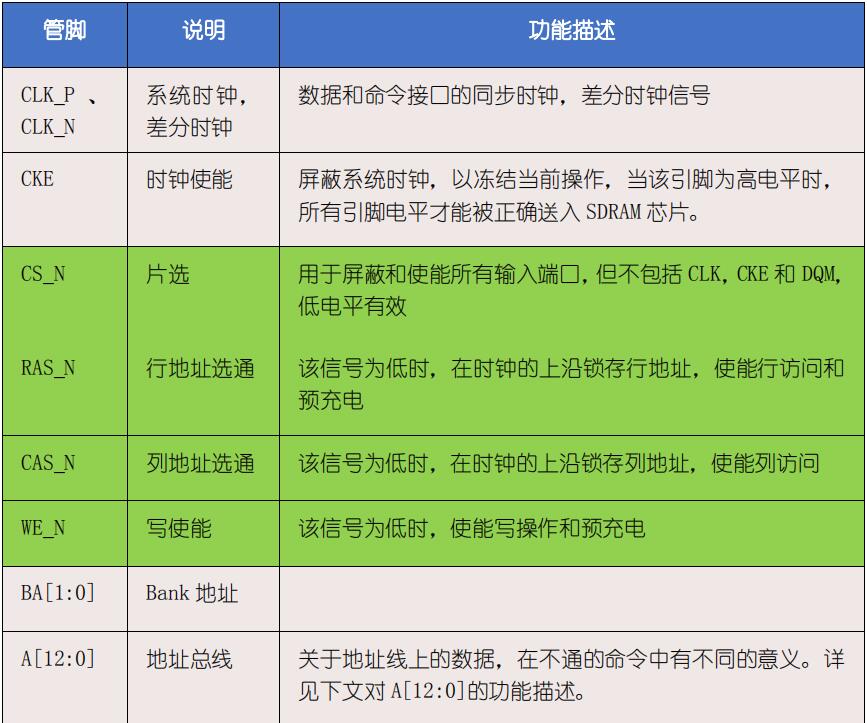

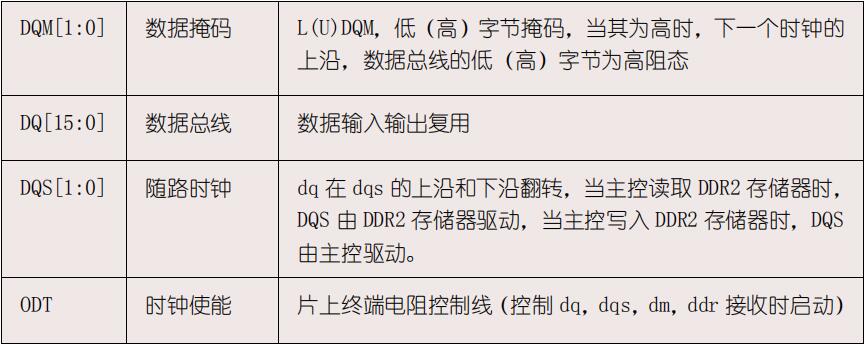

六、端口信号

简单解释如下所示:

.mem_odt (mem_odt ), //DDR2片上终结信号 .mem_cs_n (mem_cs_n ), //DDR2片选信号 .mem_cke (mem_cke ), //DDR2时钟使能信号 .mem_addr (mem_addr ), //DDR2地址总线 .mem_ba (mem_ba ), //DDR2BANK信号 .mem_ras_n (mem_ras_n ), //DDR2行地址选择信号 .mem_cas_n (mem_cas_n ), //DDR2列地址选择信号 .mem_we_n (mem_we_n ), //DDR2写使能信号 .mem_dm (mem_dm ), //DDR2数据掩膜信号 .mem_clk (mem_clk ), //DDR2时钟信号 .mem_clk_n (mem_clk_n ), //DDR2时钟反相信号 .mem_dq (mem_dq ), //DDR2数据总线 .mem_dqs (mem_dqs ), //DDR2数据源同步信号

小梅哥给出了具体解释:

懂了一些基本知识后,就可以进行 DDR2 的开发了,下篇见。

参考资料:

1、锆石科技FPGA教程

2、小梅哥《DDR2简明教程》