SignalTap II——基本使用和高级技巧

本文以4个led灯闪烁,来介绍 SignalTap II 的使用。

一、Verilog案例

led灯以1秒的时间循环左移,代码如下:

1 module led 2 //========================< 参数 >========================================== 3 #( 4 parameter TIME = 26'd5000_0000 //1s 5 ) 6 //========================< 端口 >========================================== 7 ( 8 input wire clk , //时钟,50Mhz 9 input wire rst_n , //复位,低电平有效 10 output reg [ 3:0] led //4位led灯 11 ); 12 //========================< 信号 >========================================== 13 reg [25:0] cnt ; 14 wire add_cnt /*synthesis keep*/ ; 15 wire end_cnt /*synthesis keep*/ ; 16 17 //========================================================================== 18 //== 0.2秒计数 19 //========================================================================== 20 always @(posedge clk or negedge rst_n) begin 21 if(!rst_n) 22 cnt <= 'd0; 23 else if(add_cnt)begin 24 if(end_cnt) 25 cnt <= 'd0; 26 else 27 cnt <= cnt + 1'b1; 28 end 29 end 30 31 assign add_cnt = 1'b1; 32 assign end_cnt = add_cnt && cnt== TIME-1'b1; 33 34 //========================================================================== 35 //== led灯循环左移 36 //========================================================================== 37 always @(posedge clk or negedge rst_n) begin 38 if(!rst_n) begin 39 led <= 4'b1110; 40 end 41 else if(end_cnt) begin 42 led[3:0] <= {led[2:0],led[3]}; //右移:{led[0],led[3:1]}; 43 end 44 end 45 46 47 endmodule

二、SignalTap II 的使用

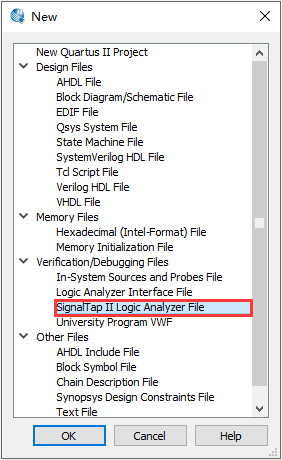

1、选择 File > New 打开 SignalTap II 窗口,选择 SignalTapII Logic Analyzer File 并单击OK。

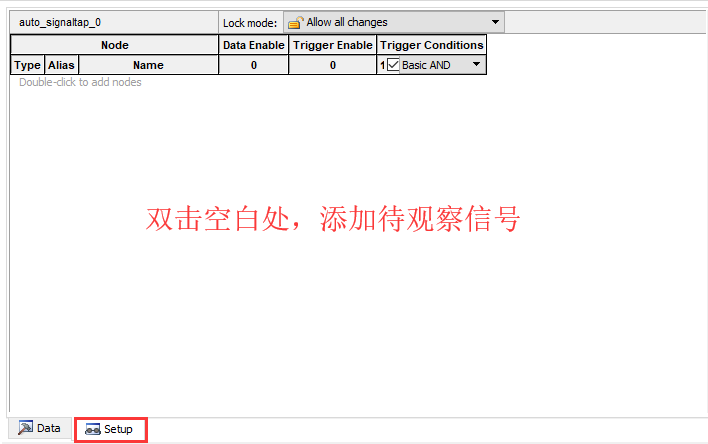

2、SignalTap II界面如下图所示,保存文件并命名为 led.stp,接下来弹出的两个对话框分别点击 OK 和 Yes。

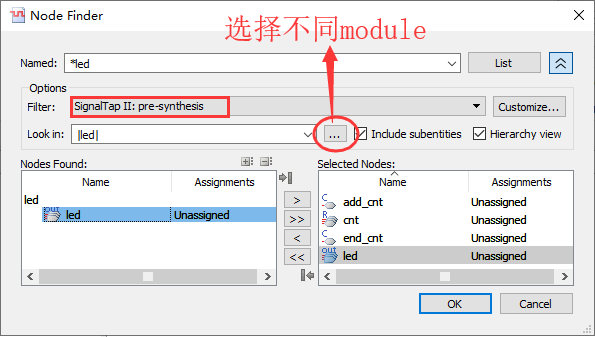

3,添加待观察信号。在 Setup 标签页中,双击空白处打开 Node Finder 窗口,在 Filter 区域中选择SignalTap II:pre-synthesis,输入信号名字后然后单击 List 即可找到能被观察到的节点。我们选中 led 和 key,然后单击 ”>” 按钮,最后单击OK。

接着设置这些信号之间的逻辑关系与和或,下面则是对单个信号设置触发条件,如这里将 end_cnt 的触发条件设置为上升沿触发,其他信号则为 Don't care。

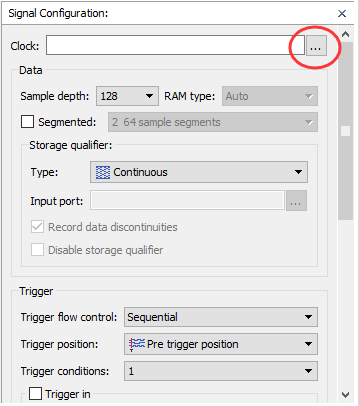

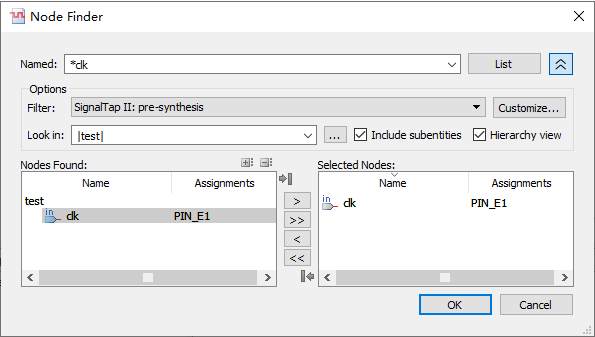

4、添加时钟信号。在 Signal Configuration 面板中的单击 Clock 部分右边的 ”…” 打开Node Finder窗口,在 Filter 处选择SignalTap II:pre-synthesis。输入时钟名字后然后单击 List 即可找到需要的时钟信号。我们选中 clk,然后单击 ”>” 按钮,最后单击OK。

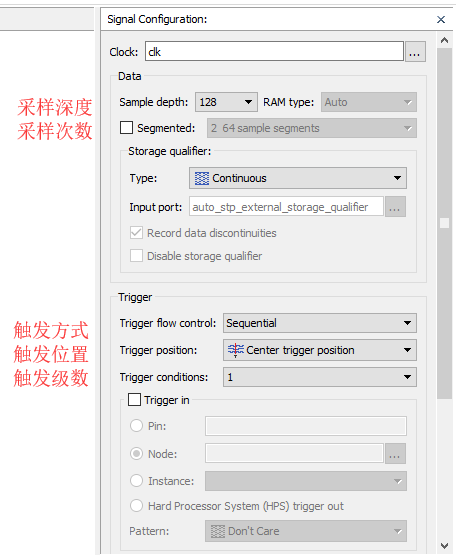

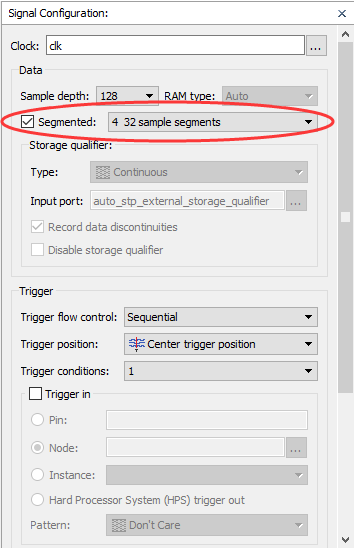

5,设置采样和触发的相关信息。

采样深度:值越大,所能观察信号的时间范围就越大,消耗的RAM资源也越多。此处选择128。

采样次数:不勾选则默认为1。如果选择为 4 32,则SignalTap会连续累计到4次采样成功后,显示这4次的波形,每次波形深度为32。此处不勾选。

触发方式:有 Sequential 和 State-based,此处选择Sequential。

触发位置:Pre为触发点前的深度小于触发点后的深度,Center为触发点的前后深度相等,Post为触发点前的深度大于触发点后的深度。此处选择Center。

触发级数:默认为1,共可选择1-10级触发,此处选择1级。

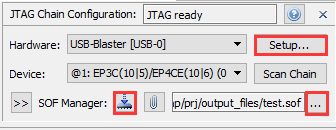

6,SignalTap II与板卡连接。首先保存这次的SignalTap设置,然后回到 Quartus 点击编译工程生成 sof 文件。之后在 SignalTap II 窗口右上方中的 Hardware 部分单击Setup 选择 USB-Blaster,最后点击 SOF Manager 部分单击“...”选择 sof 文件,再点击 ↓ 将该 sof 文件下载到板卡上。

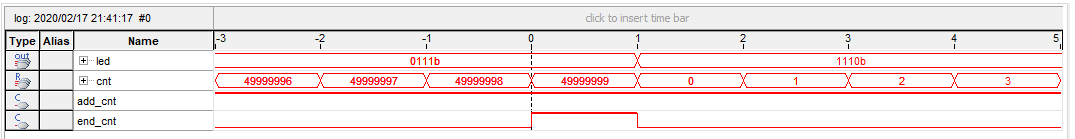

7,点击如下按钮即可看到在 Data 处看到触发后的波形。

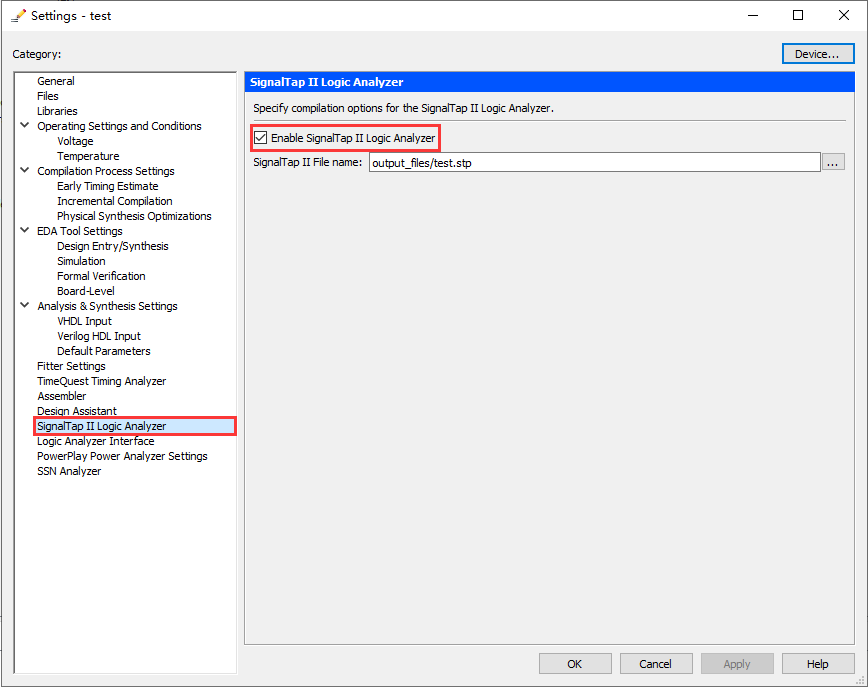

8,删除 SignalTap II。带有 SignalTap 的工程编译时间会变久,因此使用完后需要删除工程中的 SignalTap II 文件,有以下两种常用方法。

方法1:在Quartus II界面中选择 Assignments > Settings > SignalTap II Logic Analyzer,把 Enable SignalTap II Logic Analyzer前面的勾去掉。

方法2:在 Quartus II 界面的 Files 点击 .stp 文件,右键选择 Remove File from Project,直接从工程中去除 SignalTap II 文件。

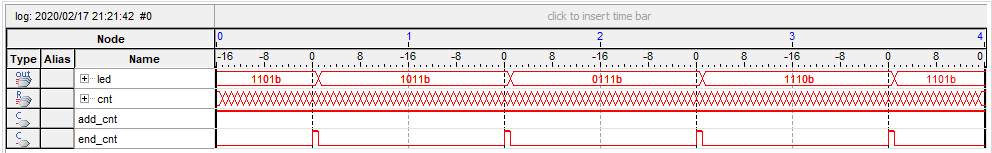

三、多次触发

多次触发即上面第5条说的采样次数,如果选择 4 32,那么连续满足4次采样条件后,SignalTap 就会显示这4次的波形,每次深度是32。如下所示:

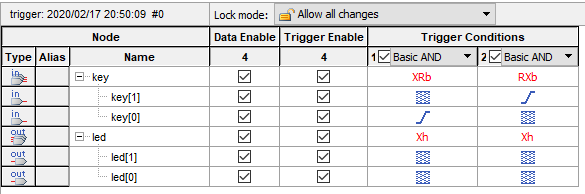

四、多级触发

上文说到的多级触发其实是一种高级的 SignalTap II 使用方法。和多次触发有所区别,多次触发是指同一个触发条件,多次满足后才显示波形。而多级触发是依次满足一级、二级、三级....触发条件后,波形才会显示。SignalTap II 中最多支持10级触发,其顺序为从左到右。

例如现在有一个工程,两个key按键分别控制两个led灯的亮灭,SignalTap II 中多级触发选择为2,在触发条件中的设置如下所示。那么在捕捉触发时,只有先按下按键0再按下按键1这个条件被满足,SignalTap II 中才会显示波形。

五、信号丢失的解决办法

除开端口信号外,程序内部定义的 wire 和 reg 信号有时会被 Quartus 编译综合时优化掉,导致在 SignalTap II 中添加信号时找不到。解决办法是在待观察的 wire 信号后的分号前加上 /*synthesis keep*/;对于 reg 信号则加 /*synthesis noprune*/ 或 /*synthesis preserve*/,如下所示:

wire [15:0] a /*synthesis keep*/; reg [15:0] b /*synthesis noprune*/; reg [15:0] c /*synthesis preserve*/;

两者的不同之处在于:/*synthesis noprune*/ 是避免 Quartus II 优化掉没 output 的reg,而 /*synthesis preserve*/ 避免 Quartus II 将 reg 优化为常数或者合并重复的 reg,若是想观察整个模块中的 reg 信号,则在module之后添加/*synthesis noprune*/。

module test(clk,rst,data)/*synthesis noprune*/ ;

好像......上面的方法有时候会失效,试试加载 wire/reg前......

六、SignalTapII失效的解决办法

有时按照步骤,根据提示进行编译,编译完成后下载程序,点击触发仍然显示需要编译。再次编译下载点击触发又说要编译,怎么回事?

原因:该 SignalTap 文件其实已经被工程移除的,也可能是自己在文件夹里删除了 .stp 文件。

办法:在该 Signaltap 页面中 save as,另保存一下即可。