SDRAM(3):刷新和仲裁

初始化完成后,我们就可以对 SDRAM 进行其他的操作了,首先需要设计的是刷新和仲裁模块。

一、SDRAM工作原理和仲裁实现

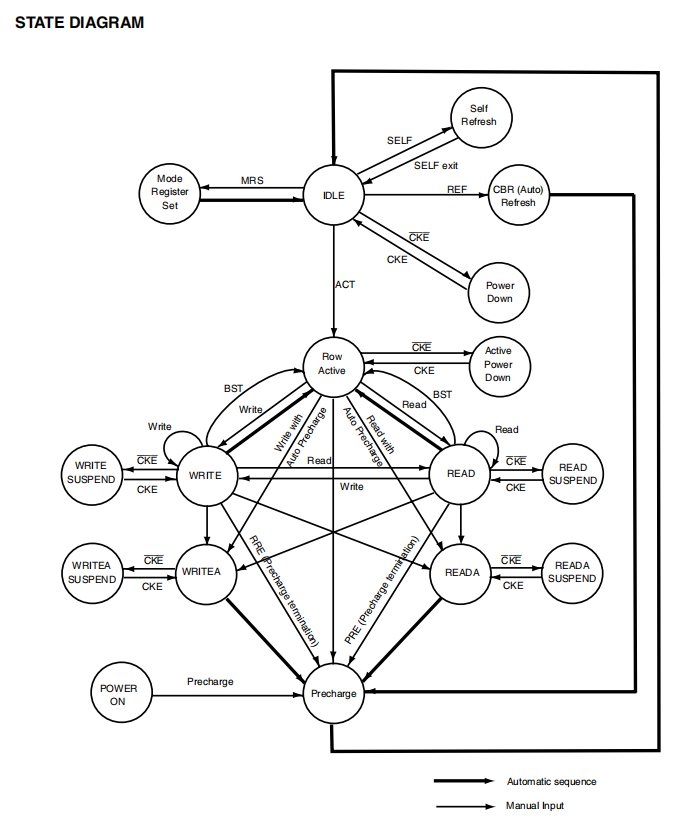

SDRAM 内部有自己的工作状态机,如下所示。其中粗线表示自动跳转,细线表示要满足某些条件后才跳转。

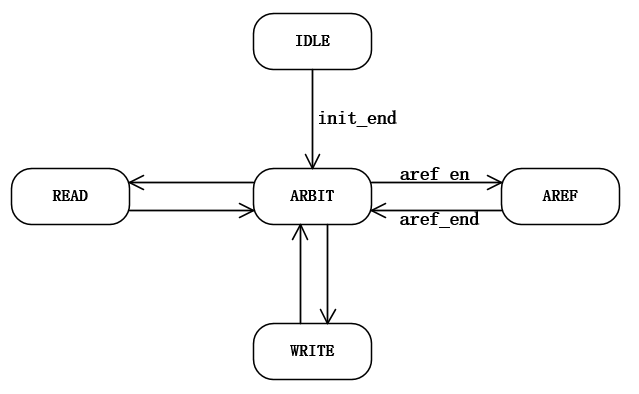

这个状态机非常复杂,但我们如果只是简单应用 SDRAM 则不需要实现里面所有操作。上电 POWER ON后,我们进行了初始化,实际上就是进行了预充电 Precharge,状态机到了 IDLE,又给了两次 Auto Refresh,此时状态机饶一圈又到 IDLE,然后给了一次 LMR 记载模式寄存器,之后状态机自动回到 IDLE。也就是说,经过上电和出似乎还后我们停在了 IDLE这,IDLE右边的 Self Refsh 和 Power Down 不用理会。后面 SDRAM 正常工作需要考虑的操作是:1、自动刷新;2:写操作;3:读操作。这三个操作靠仲裁来实现,此外需要注意优先级:自动刷新 > 写操作 > 读操作。由此我们设计代码时可以另写一个适合我们的仲裁状态机:

二、SDRAM刷新

1、刷新原理

关于 SDRAM 刷新,数据手册是这样说的:

解读一下:

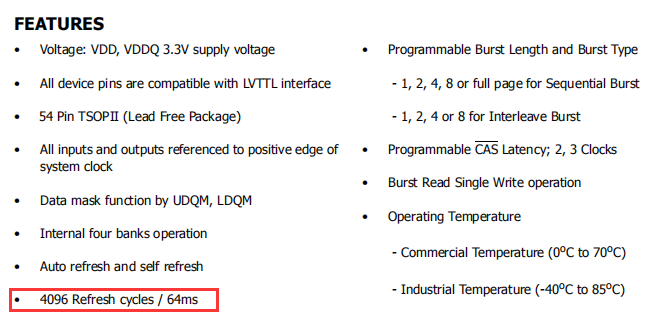

① SDRAM 必须在 64ms 内需要刷新 4096 次(不同芯片次数不同),SDRAM 需要不断的刷新,来保证其内部的电量来达到保存数据不丢失的作用,SDRAM 内部的电容能保持电量的最长时间是 64ms,即SDRAM保存数据不丢失的时间是 64ms。

② SDRAM刷新是所有 Bank 同时一行一行的刷新,SDRAM 内部有行计数器,在刷新完第0行时,会自动计数到第1行。假如0时刻刷新完第0行,那到第二次刷新第0行时要求在64ms里,而我们的行地址有12根地址线A11-A0:12‘b1111_1111_1111 = 4095,共4096行,即在64ms里面需要把4096行刷新。

③ 两次刷新之间的间隔是 64000us/4096 = 15.625us,本次设计取 15us。

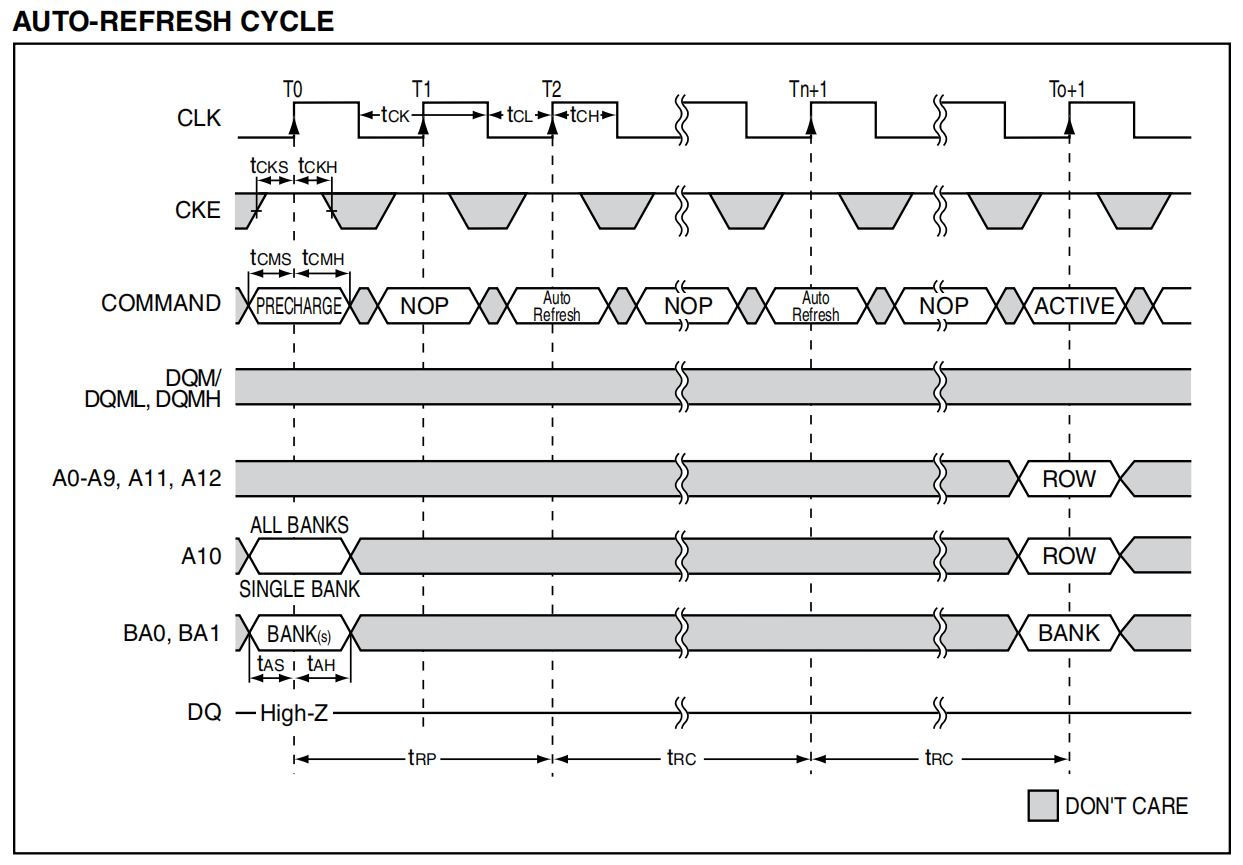

2、刷新时序

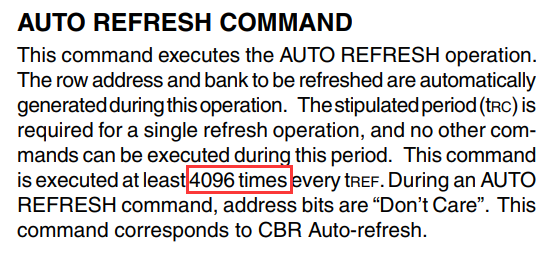

从 SDRAM 数据手册上可知,实现 AUTO-REFRESH 就一个步骤:给出一个命令:Auto Refresh,然后等待时间 tRC,之后 SDRAM 刷新结束。

这张图让很多人引起误解,第一点:图中很多指令其实是不用管的。开头的 PRECHARGE 命令在初始化、写、读的模块本身里面已经产生,这里不用再给。第二点:图中看似标出了两个 Auto Refresh 命令,但这两个命令中间是有省略符“~~”的,它的意思是中间很多个的 Auto Refresh 命令,即产生多次刷新,而我们设计一次的刷新只需要给一个 Auto Refresh 命令即可。第三点:后面的 ACTIVE 命令是为了接后面的其他操作的,并不是刷新操作本身需要的。

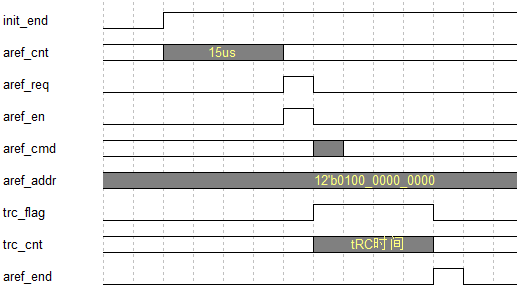

由此我们可以得出刷新模块的设计时序:

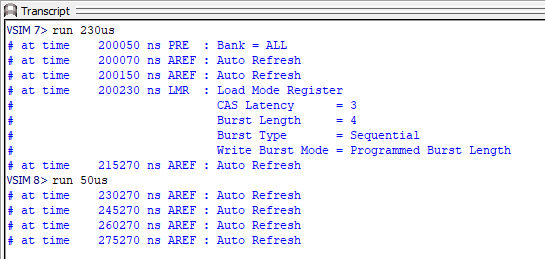

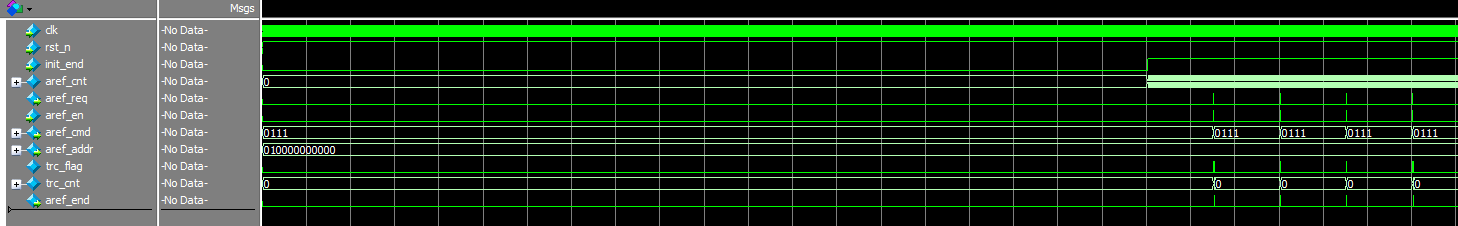

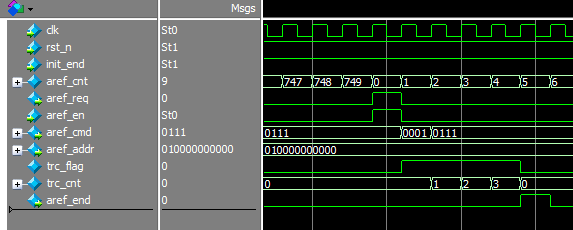

三、仿真

可以看到波形和我们的设计是完全一致的,刷新模块设计成功!

参考资料:

[1]威三学院FPGA教程

[2]开源骚客FPGA教程