DDR3(1):IP核调取

本系列整理一下基于 Xilinx A7 芯片的 DDR3 的使用,此处采用的 DDR3 IP核为软核,即采用 FPGA 逻辑单元、寄存器、查找表等搭建出来 IP核。从 IP 核的调取开始,接着读写测试,最后争取实现一个基于 DDR3 的完整小项目。

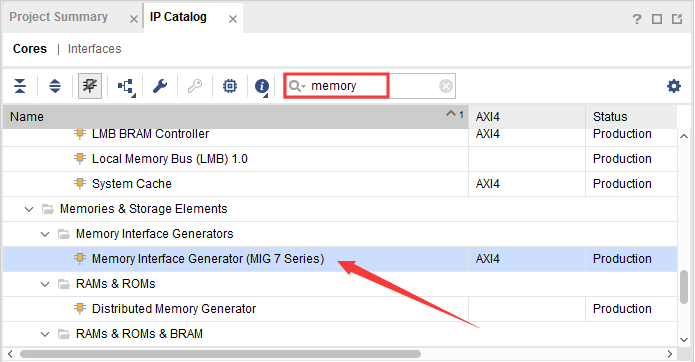

1、建立工程,点击 IP Catalog,在界面右侧输入 memory,选择 IP,双击打开。

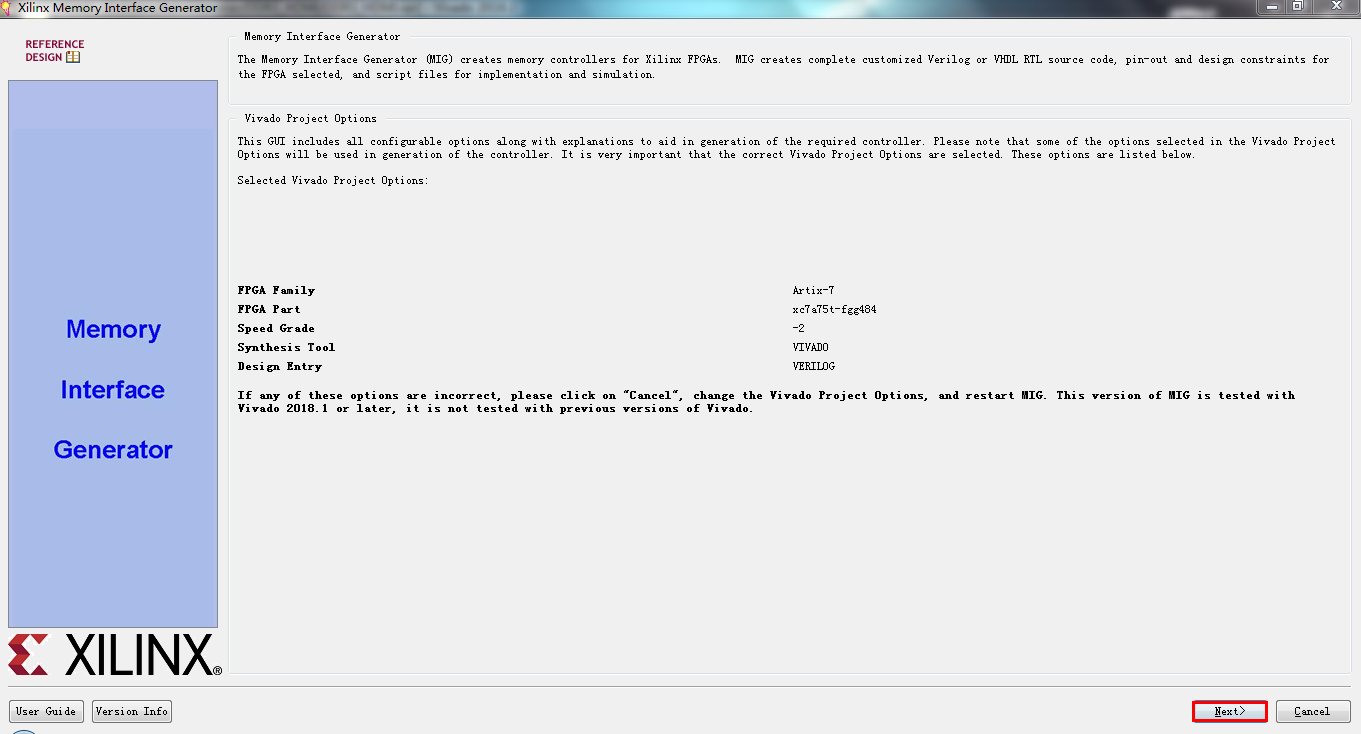

2、打开 DDR3 IP 核调取界面,该界面中主要是总结了所选芯片的型号等,点击 Next。

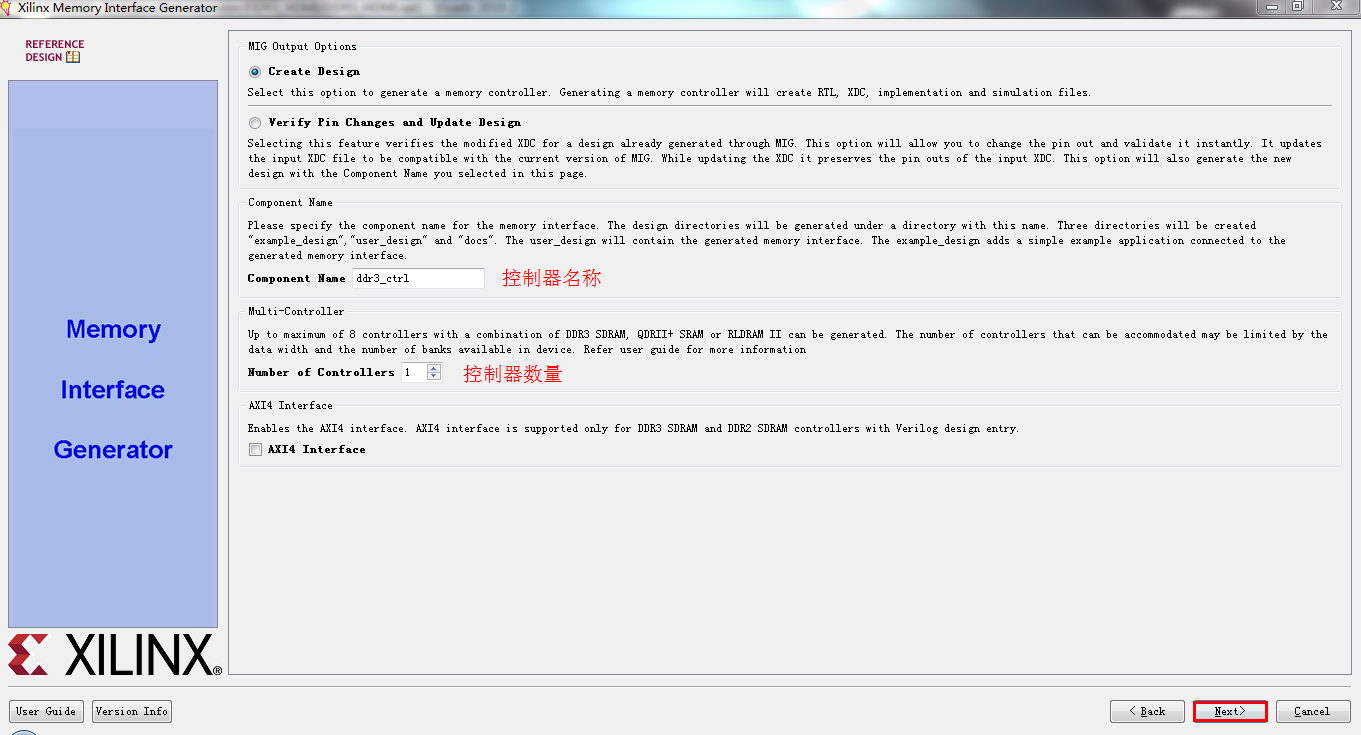

3、定义控制器名称,输入控制器数量,Next。(AXI4 Interface 是AXI格式的MIG核,不勾是传统的接口信号格式。)

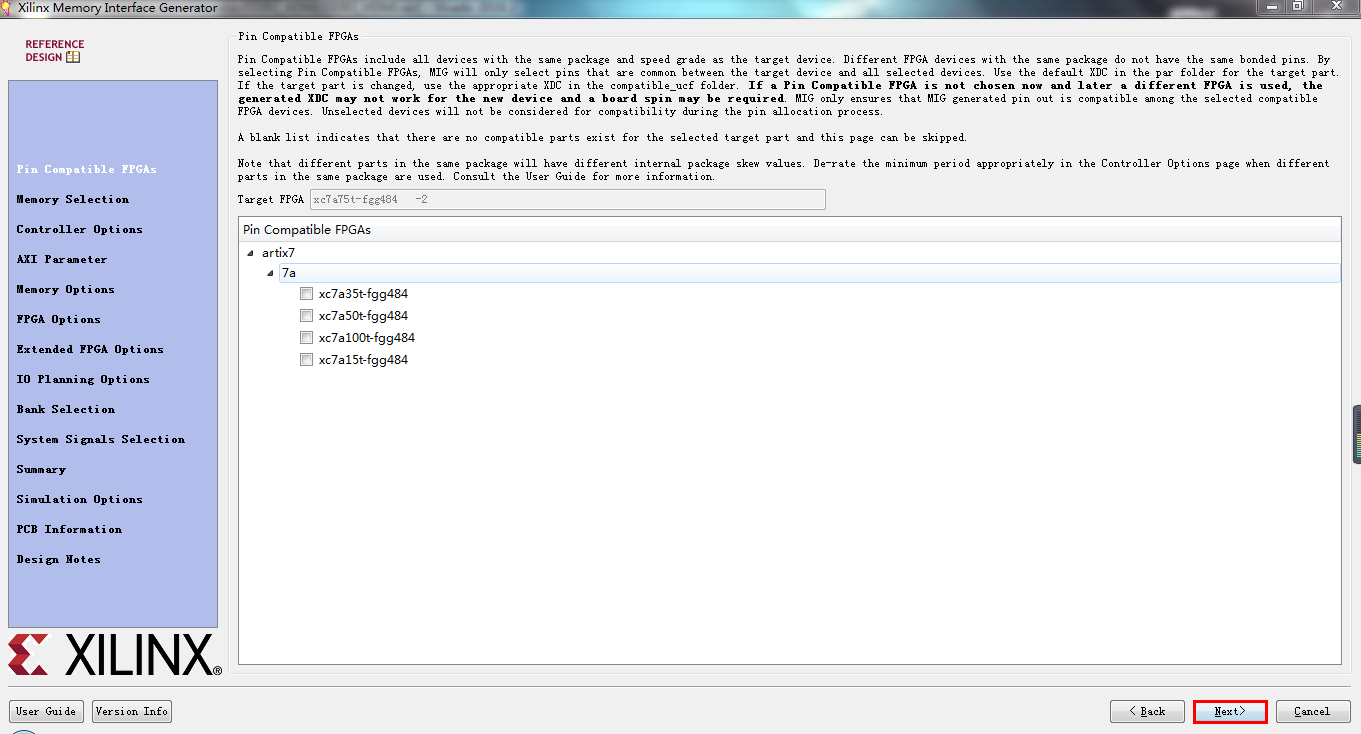

4、如果有我们的芯片型号则勾选,没有则不选,Next。

5、选择控制器类型,LP意思是low power,用于低功耗常见的特殊DDR,Next。

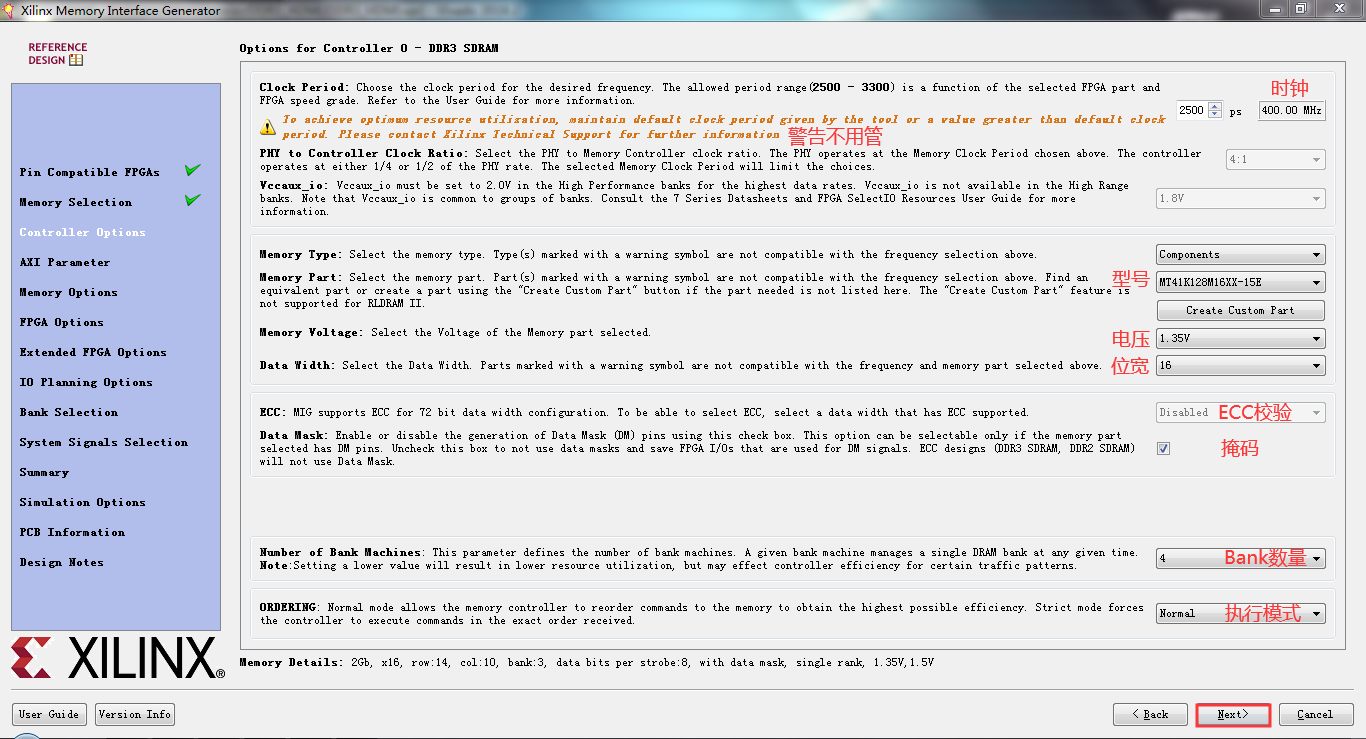

6、设置 DDR3 控制器的若干参数,Next。

Clock Period : 给DDR3的同步的时钟,此时钟再产生DDR3的800M(400M时钟双沿传递),不用管warning,在此我们设置为 400MHz,若是 FPGA 芯片速度等级不同,则可能该工作频率的范围不一样 Memory Part : 选择 DDR3 SDRAM 的芯片类型,此处需要根据开发板上的芯片类型来选择,若是列表内没有相应的芯片类型,则可以在 Create Custom Part 中根据 DDR3 芯片参数来设定 DDR3的带宽计算 : 400 * 2 * 16 = 12.8 Gbps (400: 控制器 PHY 的时钟, 2: DDR 双沿采样, 16: 16bit,bus 的位宽。)

DDR3控制器是半双工模式(分时读写),平均分配的话每个操作占有 6.4Gbps 的理论带宽,实际没有那么多,因为刷新、激活、读写指令等也都会占用周期。因此实际应用我们会*0.8来考虑。

7、设置 DDR3 控制器的若干参数。在此设定该控制器的输入时钟频率为 200MHz,倍频即为之前的400Mhz,控制器的突发类型为顺序性,其他默认即可,Next。

8、设置系统时钟和参考时钟,Next。

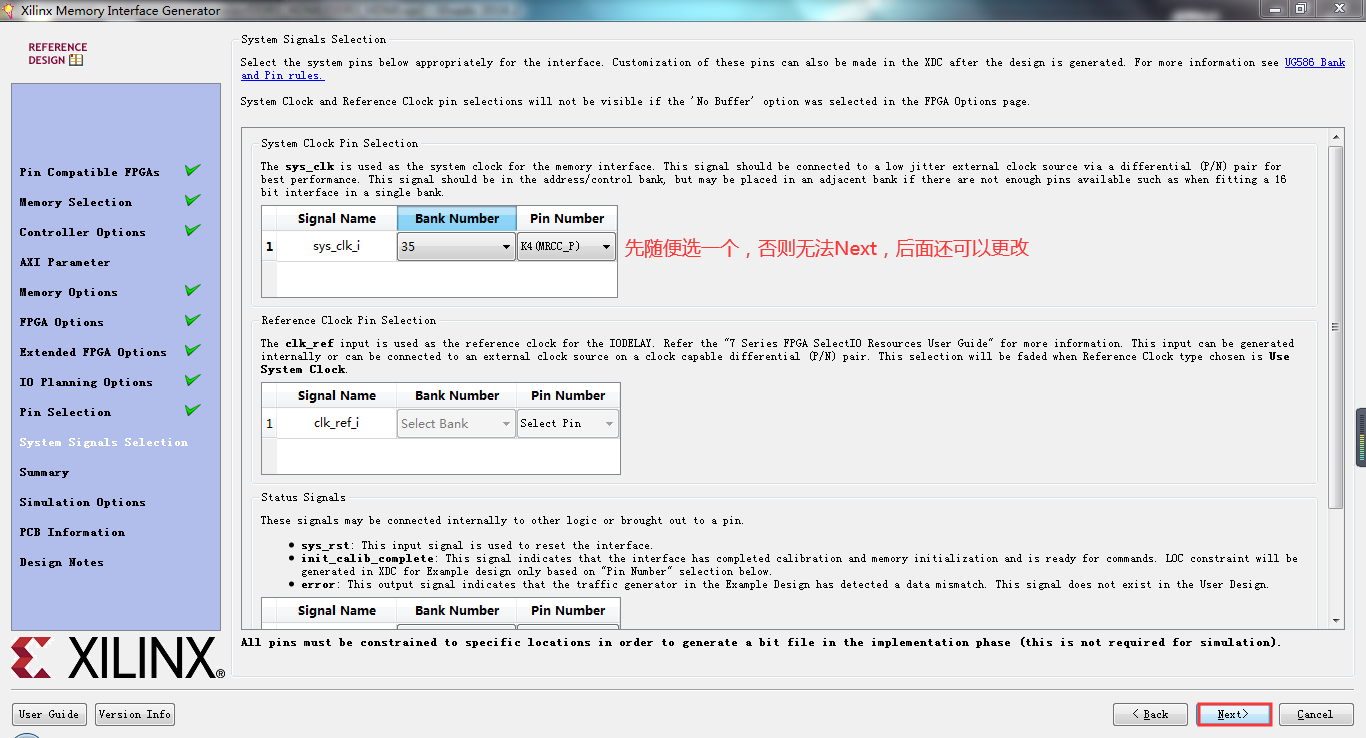

系统时钟 -------------------------------------------------------------------------- single_ended :来源于引脚的单端时钟 deferential :差分时钟 no buffer :来源于 FPGA 内部的时钟。 参考时钟 -------------------------------------------------------------------------- single_ended、deferential、no buffer, use system clock:只有在 system clock 时钟频率为199MHZ~201MHz 时,才存在该选项。

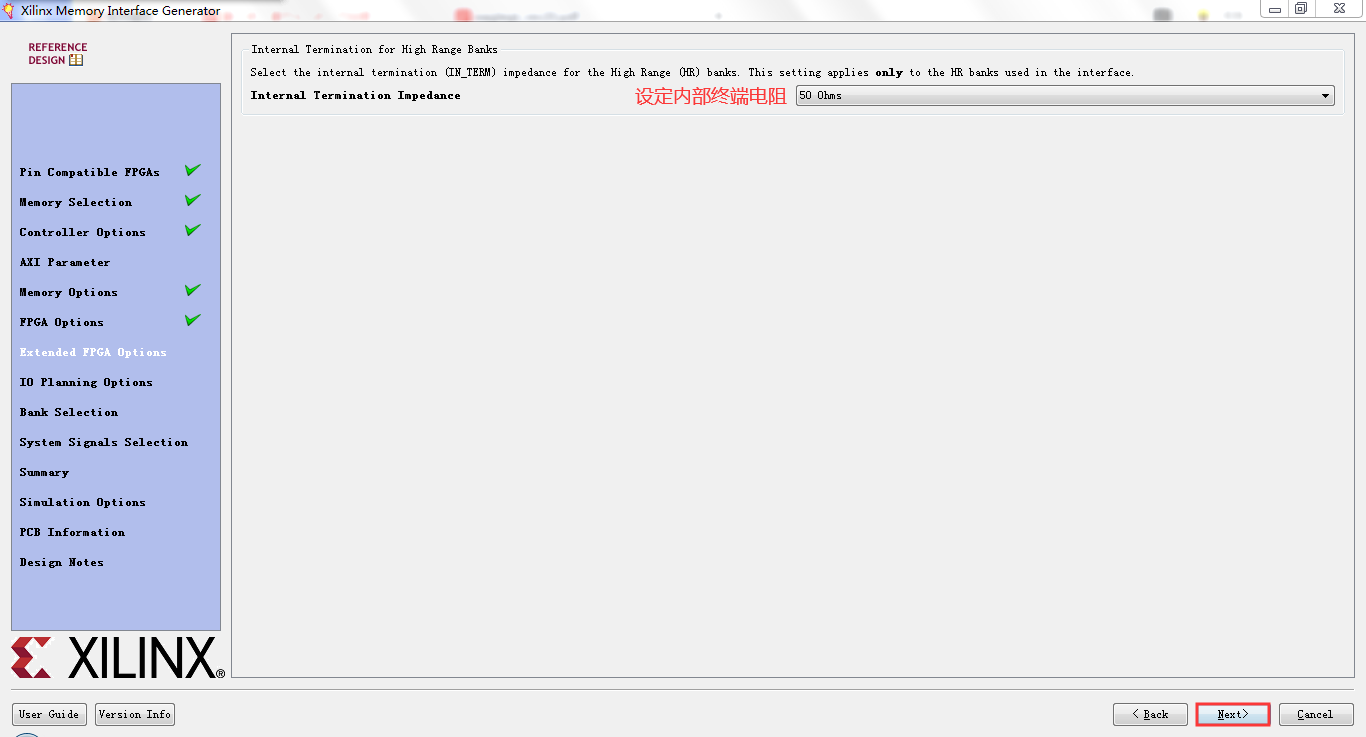

9、设置内部终端电阻值,此处根据 DDR3 SDRAM芯片手册选择,默认问题也不大。Next。

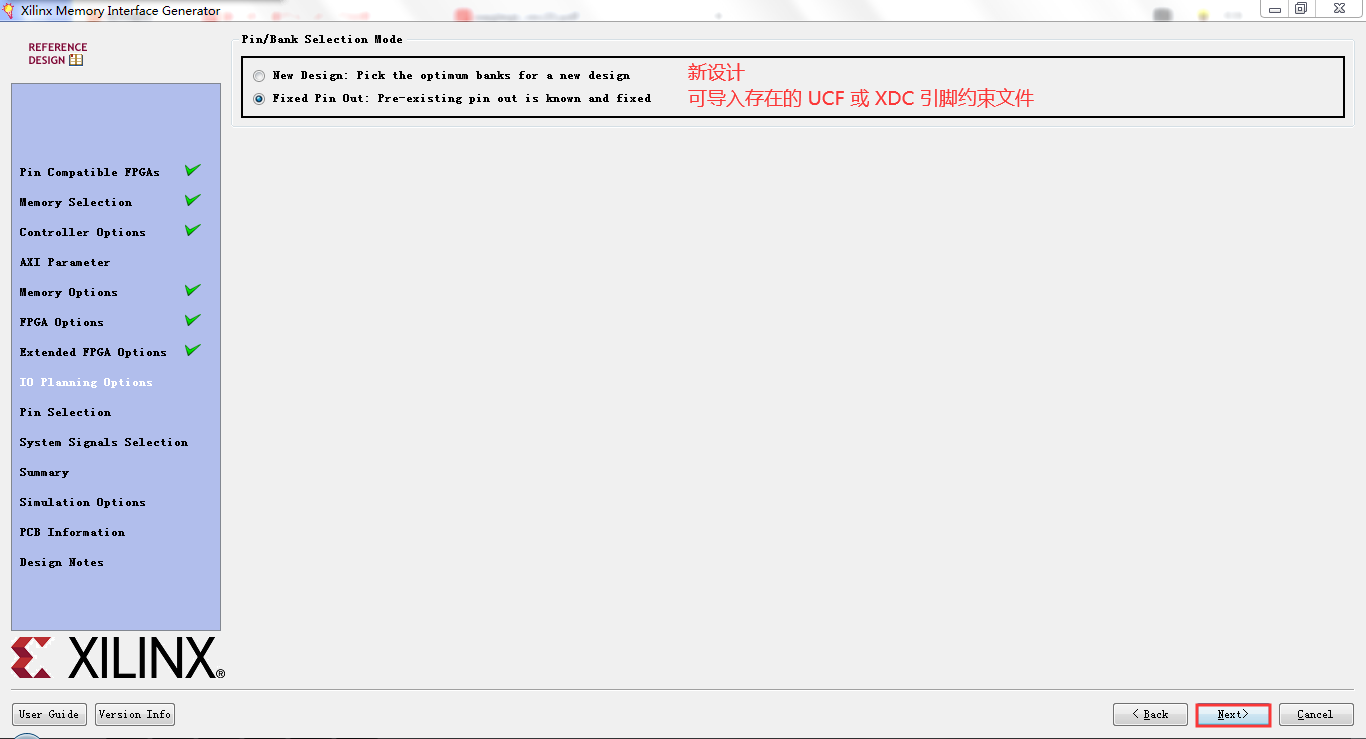

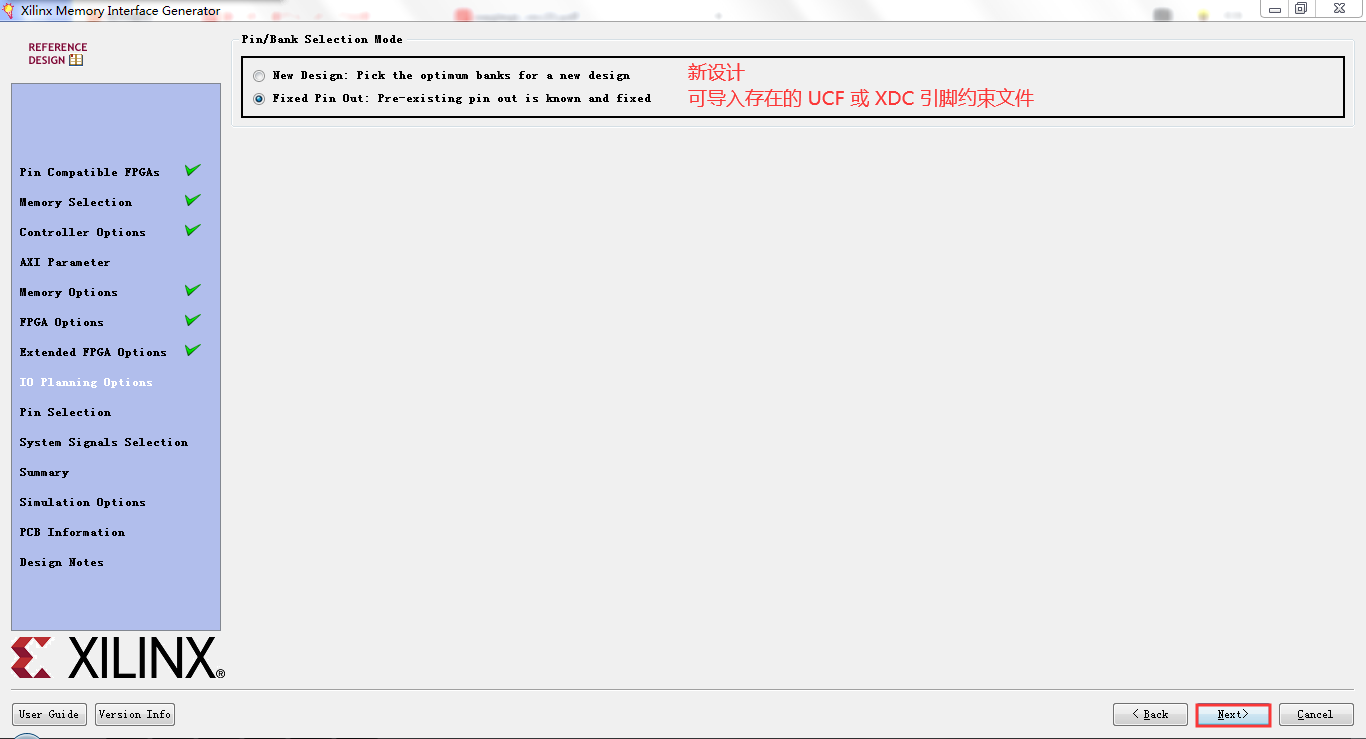

10、第一项为新设计,第二项为可导入已存在的 UCF 或 XDC 引脚约束文件。Next。

11、先点击 Read XDC/UCF 导入相应的引脚约束文件,再点击 Validate 进行验证,然后点击 Next。

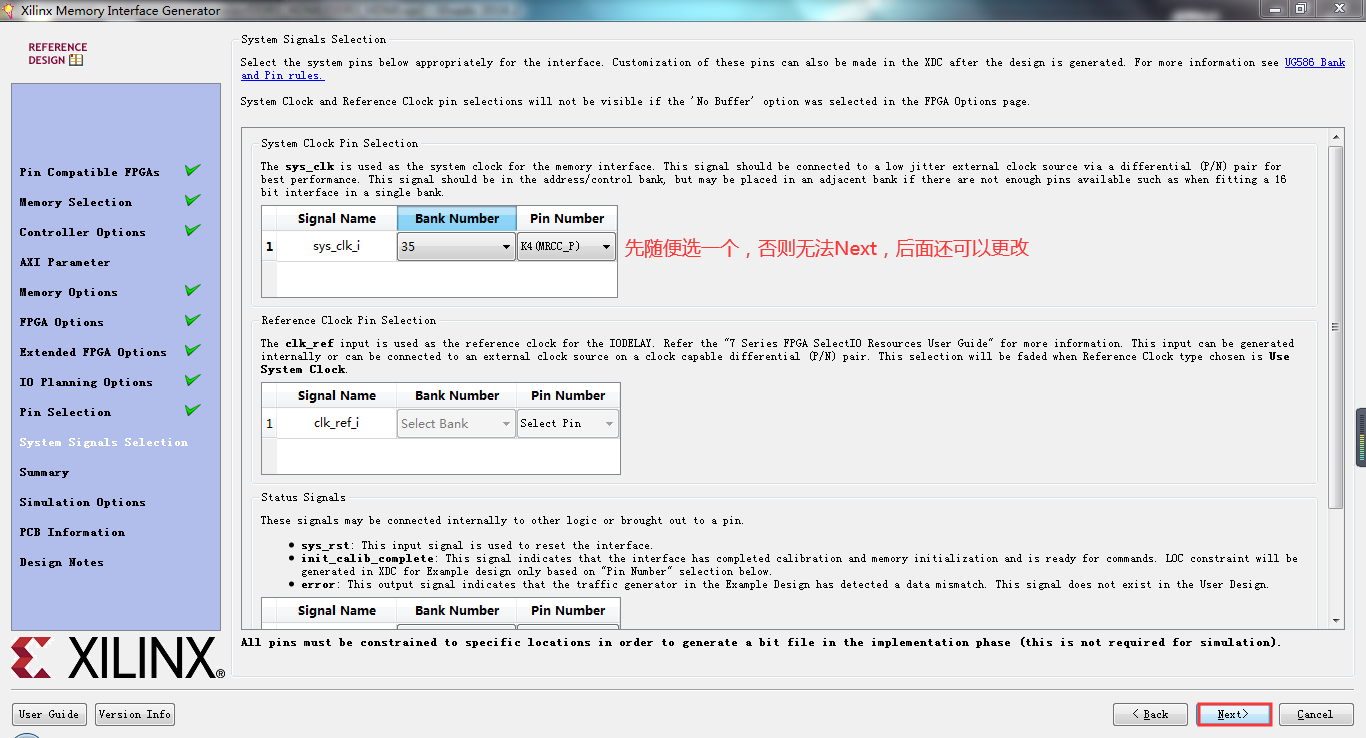

12、型号名称和一些设置,可以默认,若无法 Next,则随便选一个,后面还可以更改,Next。(应该是时钟类型错选了 single ended才出现这个,改回no buffer就没这个了)

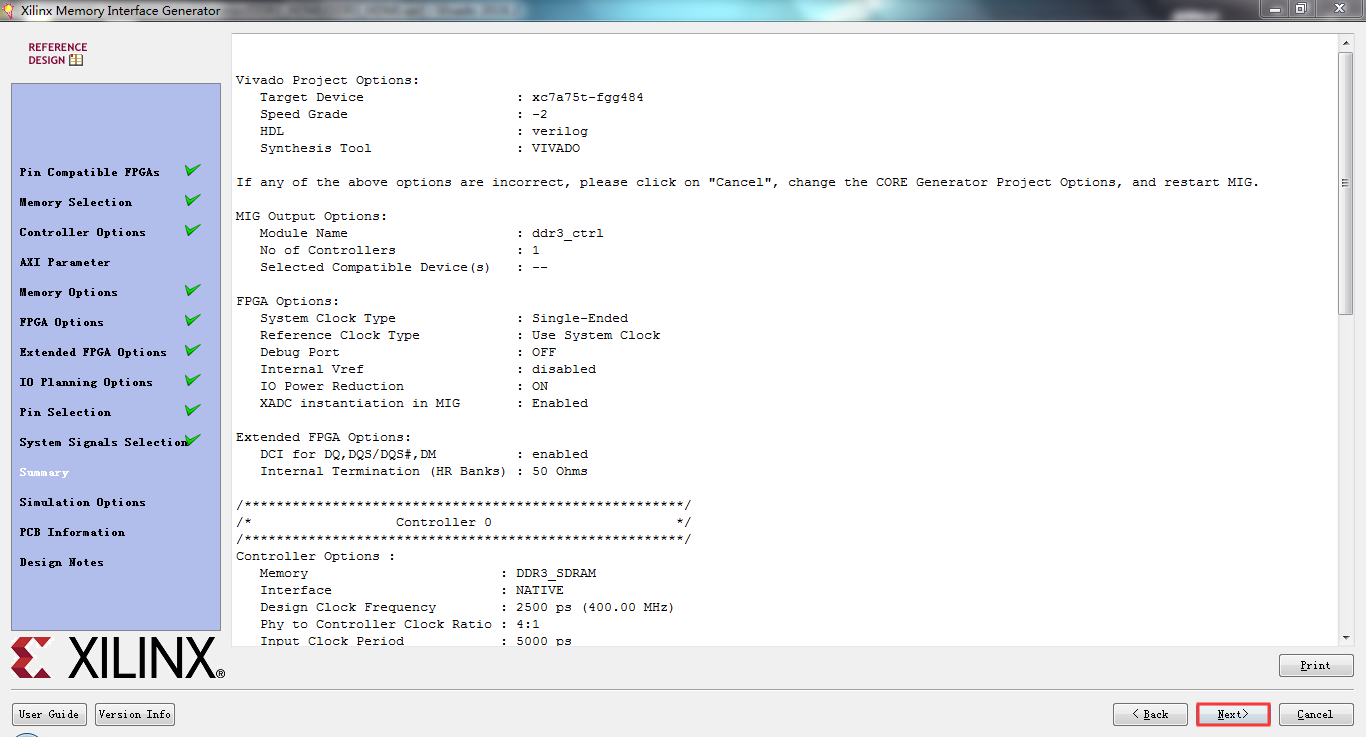

13、总结页面,Next。

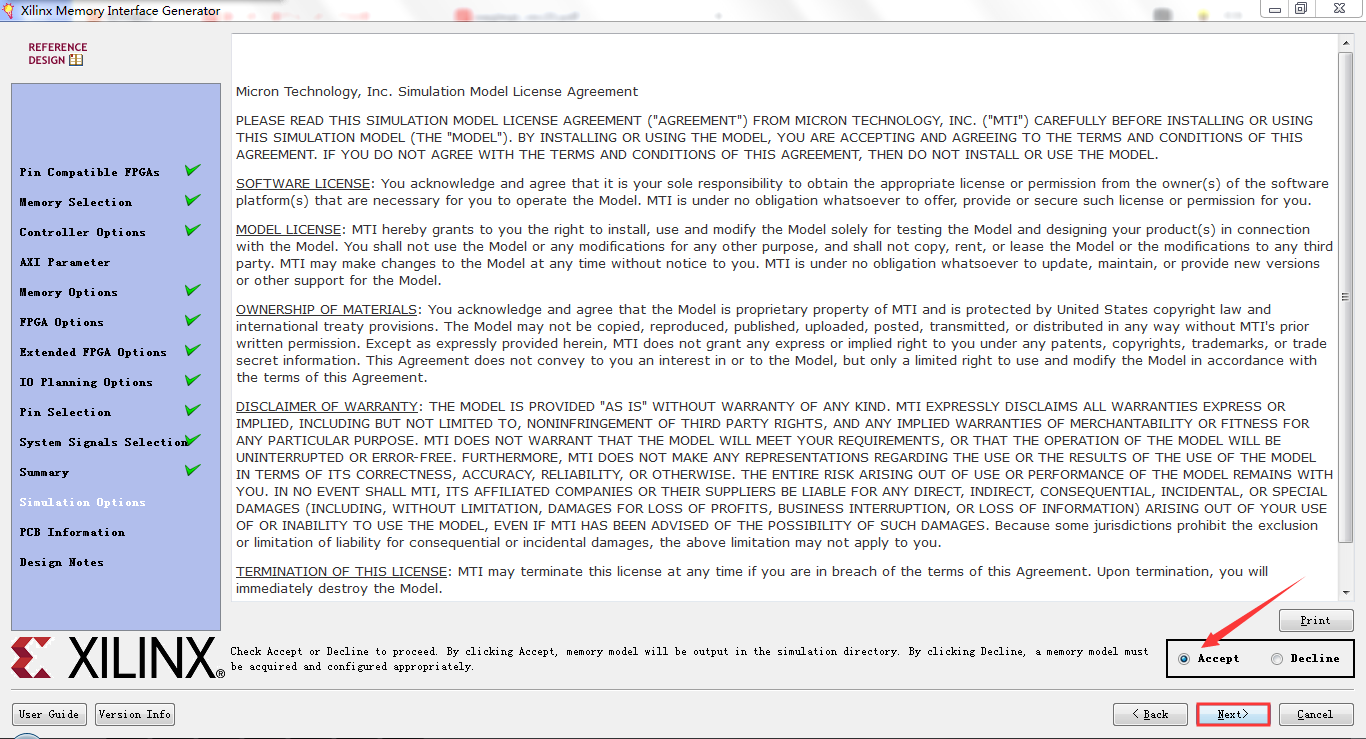

14、选择 Accept,Next。

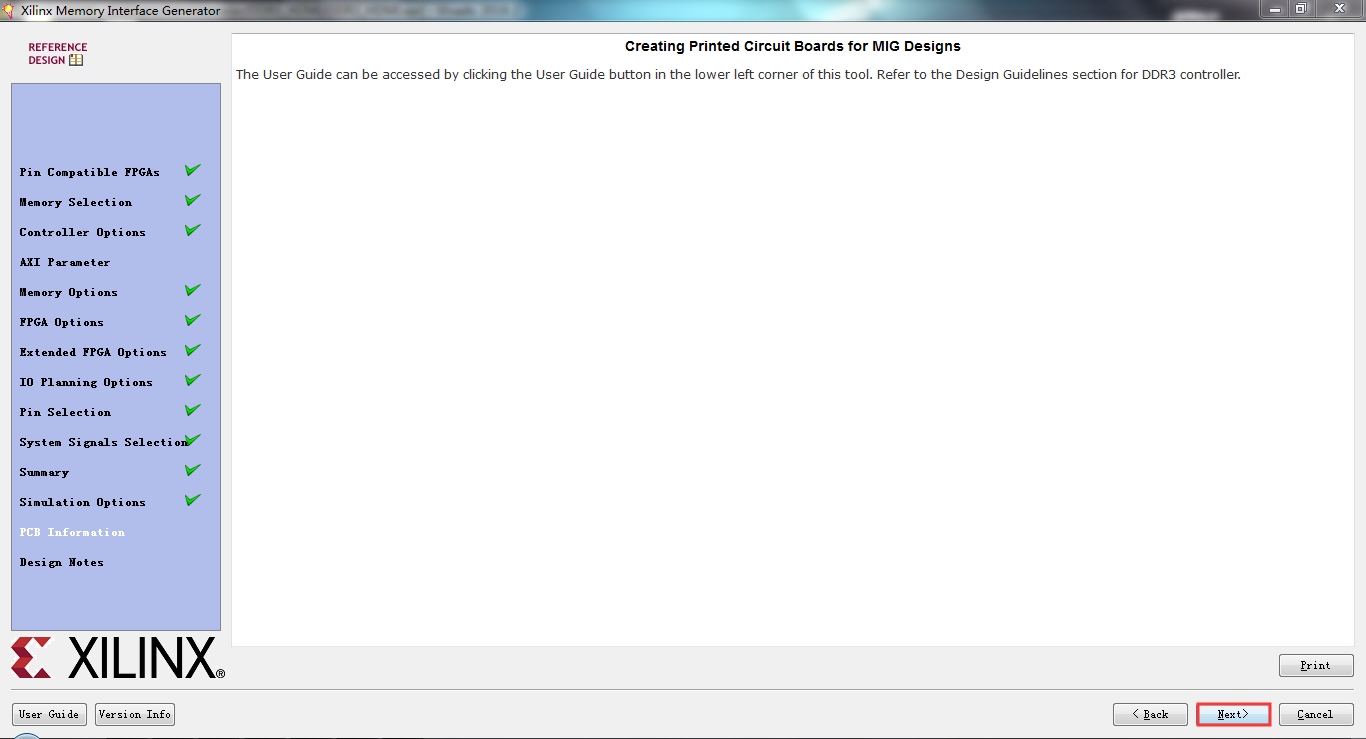

15、直接 Next。

16、点击 Generate 生成 IP 核。

17、生成后,在本次的目录 DDR3_HDMI\DDR3_HDMI.srcs\sources_1\ip\ddr3_ctrl\ddr3_ctrl 中可以看到生成的3个文件夹,说明我们此次 DDR3 IP 核调取成功。

docs : 该IP核相关文档,如使用方法等。

example_design : 该IP核参考例程,仿真模型等。

user_design : 用户可使用的文件,如综合文件、约束文件。

以上。

参考资料:威三学院FPGA教程