ZYNQ笔记(6):普通自定义IP封装实现PL精准定时中断

软件的定时中断很难控制精准触发沿的位置,可以通过 PL-PS 的中断完成精准的定时中断。PL 的中断通过 Verilog 代码产生,这样紧密结合 PS-PL 的处理,发挥各自的优势。

一、PL 侧定时中断

1.实际要求

① 上升沿中断; ② 高电平宽度不小于1us; ③ 中断计数器的时钟为 200Mhz; ④ 有两个中断: 3ms 和 0.5ms

2.Verilog中断代码

1 //************************************************************************** 2 // *** 名称 : genintr3ms05ms.v 3 // *** 作者 : xianyu_FPGA 4 // *** 博客 :https://www.cnblogs.com/xianyufpga/ 5 // *** 日期 :2019-08-10 6 // *** 描述 : 3ms和0.5ms精准延时 7 //************************************************************************** 8 9 10 module genintr3ms05ms 11 //==================<端口>================================================== 12 ( 13 //input ----------------------------------------- 14 input wire clk , //时钟,200Mhz 15 input wire rst , //复位,高电平有效 16 //output ---------------------------------------- 17 output reg intr3ms , //3ms中断 18 output reg intr05ms //0.5ms中断 19 ); 20 //==================<参数>================================================== 21 parameter CNT3MS_END = 600000 ; 22 parameter CNT05MS_END = 100000 ; 23 parameter PULSEW = 200 ; //中断高电平维持时间 24 //==================<信号>================================================== 25 reg [23:0] cnt3ms ; 26 wire add_cnt3ms ; 27 wire end_cnt3ms ; 28 reg [23:0] cnt05ms ; 29 wire add_cnt05ms ; 30 wire end_cnt05ms ; 31 32 //========================================================================== 33 //== 0.5ms延时 34 //========================================================================== 35 always @(posedge clk) begin 36 if(rst) 37 cnt3ms <= 0; 38 else if(add_cnt3ms) begin 39 if(end_cnt3ms) 40 cnt3ms <= 0; 41 else 42 cnt3ms <= cnt3ms + 1; 43 end 44 end 45 46 assign add_cnt3ms = 1; 47 assign end_cnt3ms = add_cnt3ms && cnt3ms== CNT3MS_END-1; 48 49 always @(posedge clk) begin 50 if(rst) begin 51 intr3ms <= 0; 52 end 53 else if(end_cnt3ms) begin 54 intr3ms <= 1; 55 end 56 else if(add_cnt3ms && cnt3ms==PULSEW-1) begin 57 intr3ms <= 0; 58 end 59 end 60 61 //========================================================================== 62 //== 3ms延时 63 //========================================================================== 64 always @(posedge clk) begin 65 if(rst) 66 cnt05ms <= 0; 67 else if(add_cnt05ms) begin 68 if(end_cnt05ms) 69 cnt05ms <= 0; 70 else 71 cnt05ms <= cnt05ms + 1; 72 end 73 end 74 75 assign add_cnt05ms = 1; 76 assign end_cnt05ms = add_cnt05ms && cnt05ms== CNT05MS_END-1; 77 78 always @(posedge clk) begin 79 if(rst) begin 80 intr05ms <= 0; 81 end 82 else if(end_cnt05ms) begin 83 intr05ms <= 1; 84 end 85 else if(add_cnt05ms && cnt05ms==PULSEW-1) begin 86 intr05ms <= 0; 87 end 88 end 89 90 91 92 endmodule

3.PL中断封装成私有IP

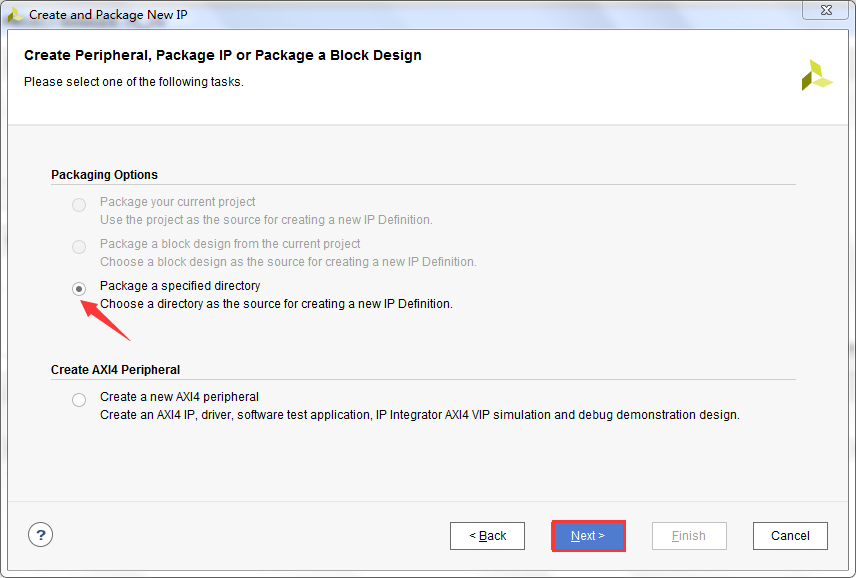

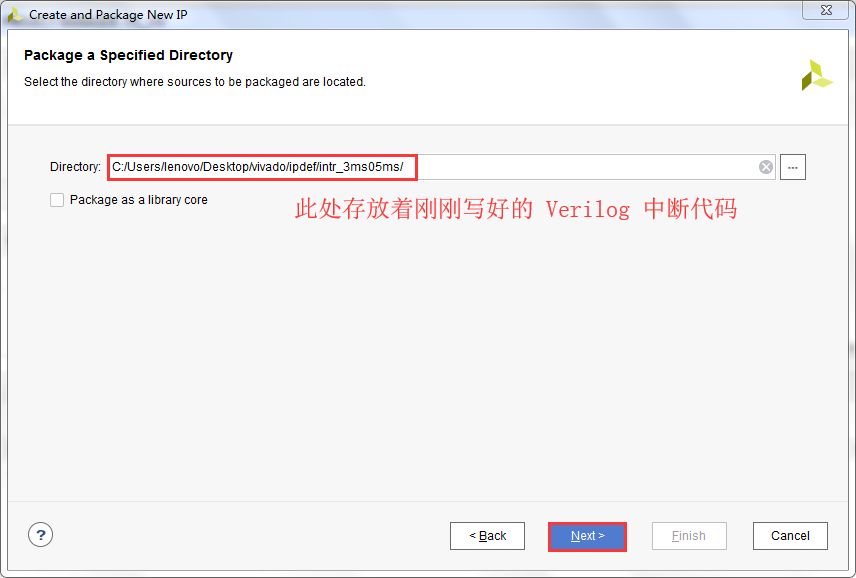

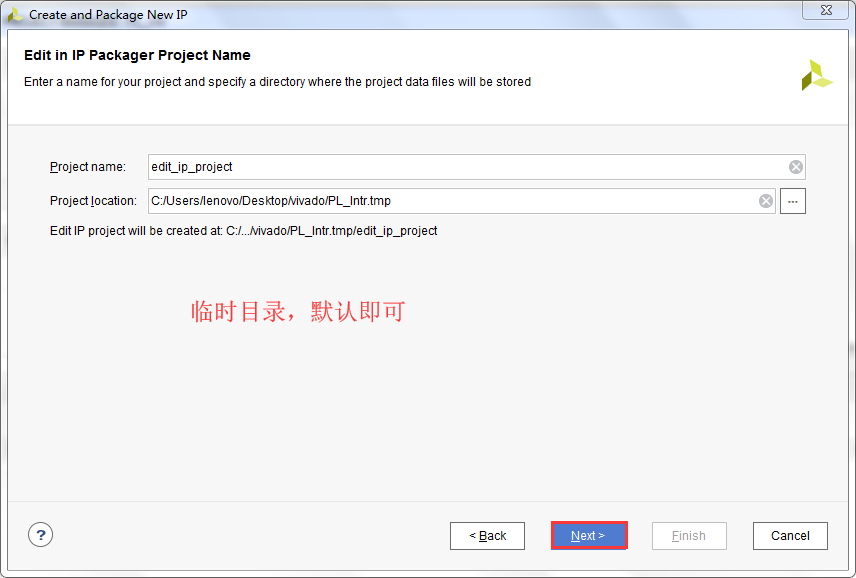

①打开 Vivado,新建工程,然后选择菜单栏 Tools --- Create and Package New IP...

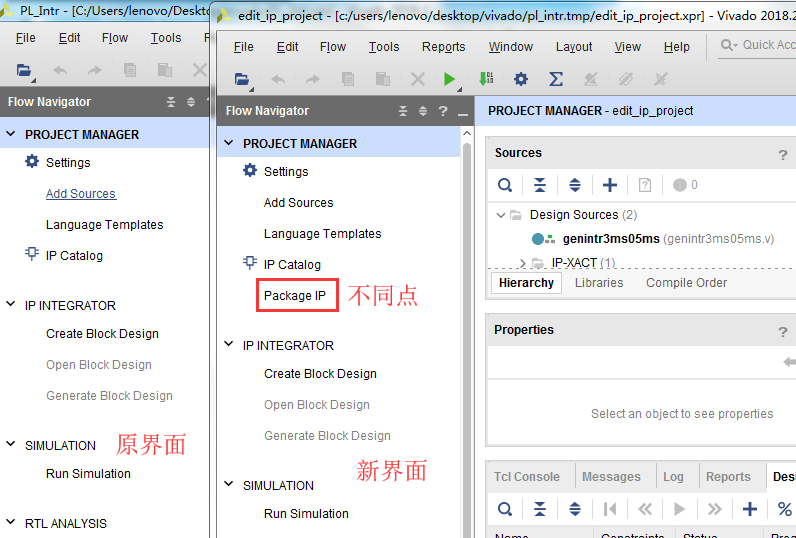

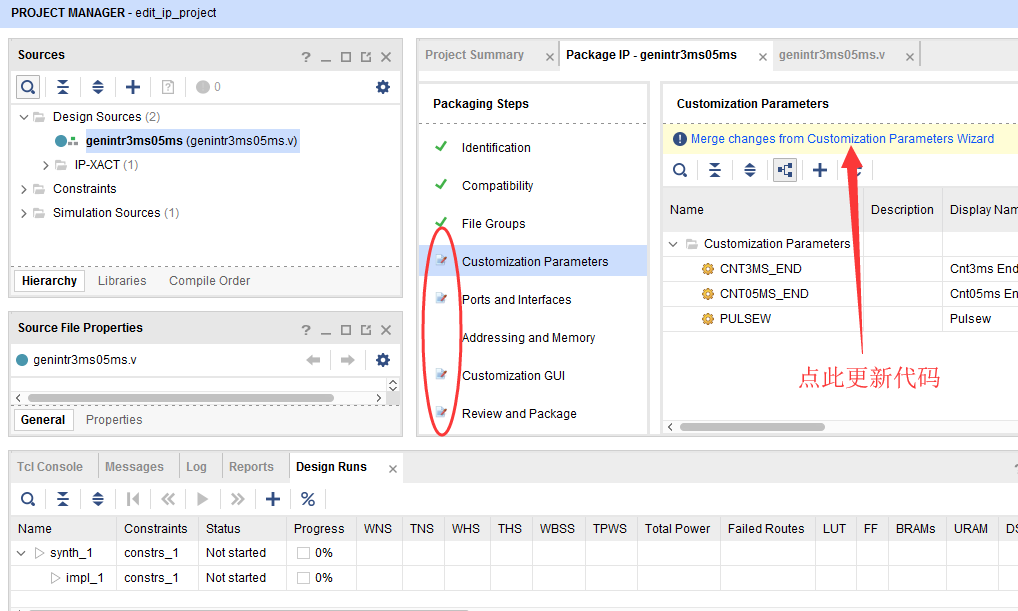

②Vivado 打开了一个新的界面,类似于原界面,但是多了一个选项

这时如果 Verilog 有语法错误,Source处会显示红色波浪线。也可以在此新界面修改代码,修改后保存,页面显示成编辑图标,必须点击更新才行。

③默认情况下,复位是低有效,我们可以手动改成高有效

④选择 Review and Package 可以看到 Package IP ,点击它即可完成 IP 的封装

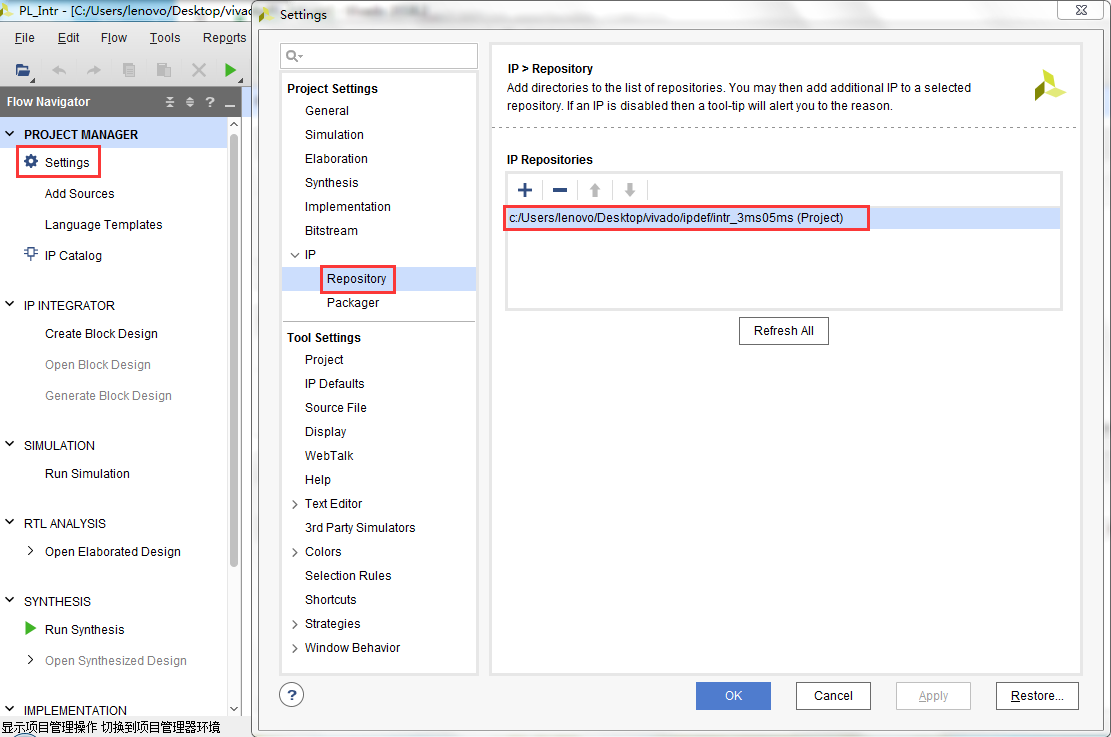

⑤此页面自动关闭,回到原页面,可以在 Settings --- IP --- Repository 中可以看到这个自定义 IP,此页面也可以手动添加第三方 IP

⑥生成 bit 文件并以此加载 SDK。

二、ZYNQ硬中断的使用

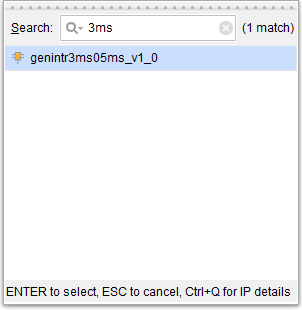

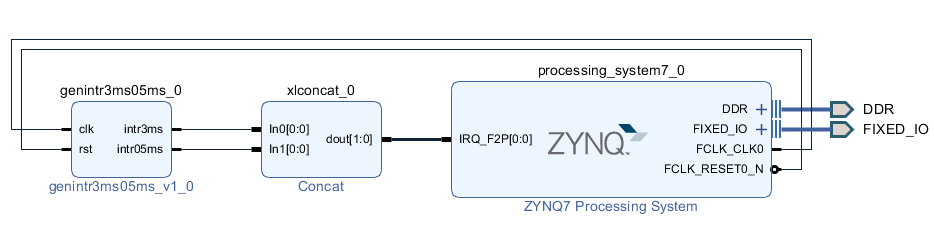

1.进入到 Create Block Design 中,输入 genintr3ms05ms 即可添加该自定义 IP

2.添加 ZYNQ,复位选上,时钟频率设置为 200Mhz,同时记得勾选中断

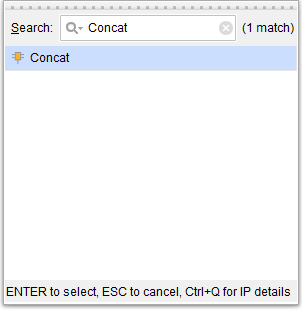

3.连线,两个中断,但只有一个接口,我们借用一个 Concat IP 即可

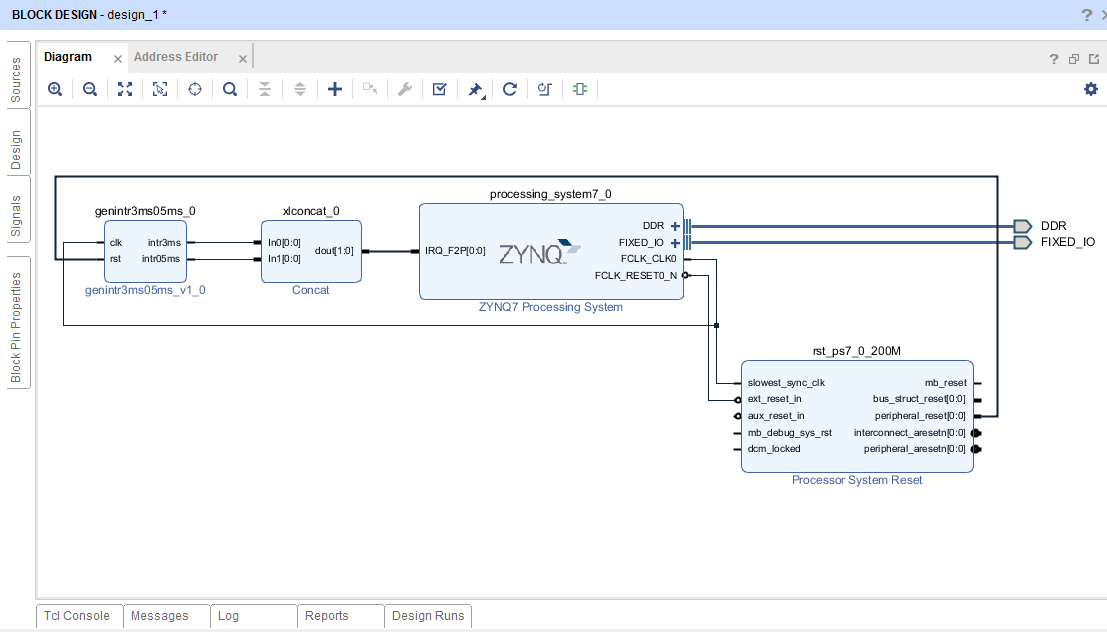

4.连线可以直接点击上方 Run 自动布线,会多出一个 Processor System Reset模块,中断复位是高有效,而ZYNQ复位是低有效,此模块会协调好。而手动布线则可能出错。

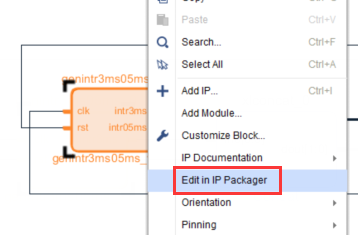

5.如果布线时发现自定义 IP 需要修改,可以选中该 IP,右键进入修改

之后就可以进入到SDK进行中断代码编写了,和普通PL中断是类似的。

参考资料:

[1]V3学院FPGA教程