ZYNQ笔记(1):PL端——led灯

ZYNQ分为PS和PL,本篇文章实际上是Vivado中一个完整的FPGA工程的创建,正所谓万事开头难。

PS:处理系统 (Processing System) 即ARM部分

PL:可编程逻辑(Programable Logic) 即FPGA部分

一、新建工程

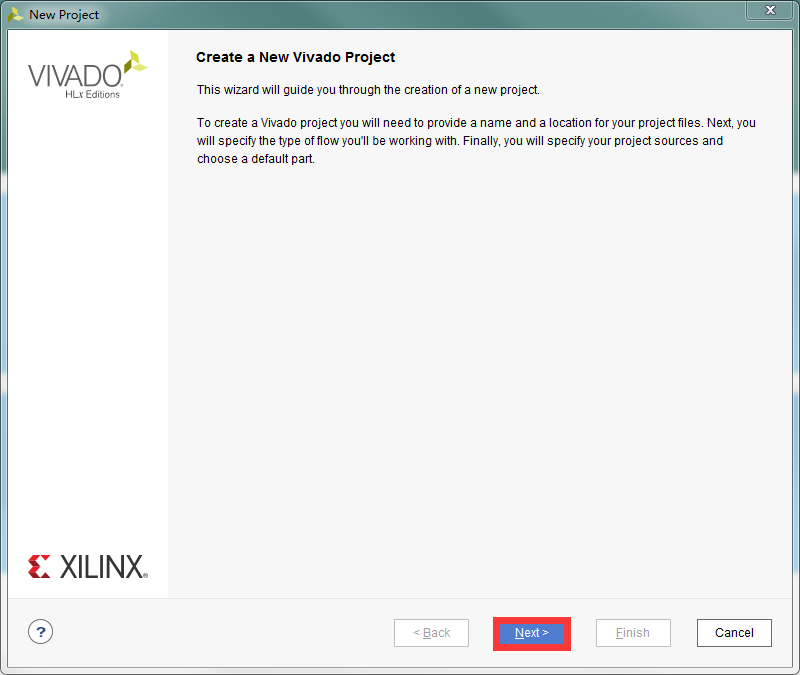

1.打开Vivado,新建一个工程,Next

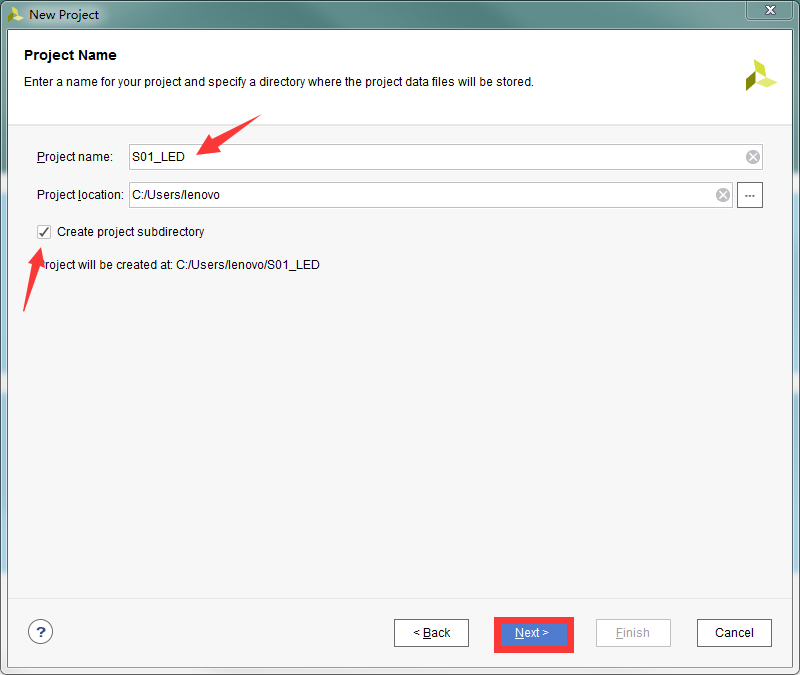

2.设置工程名称和工程所在目录,Next

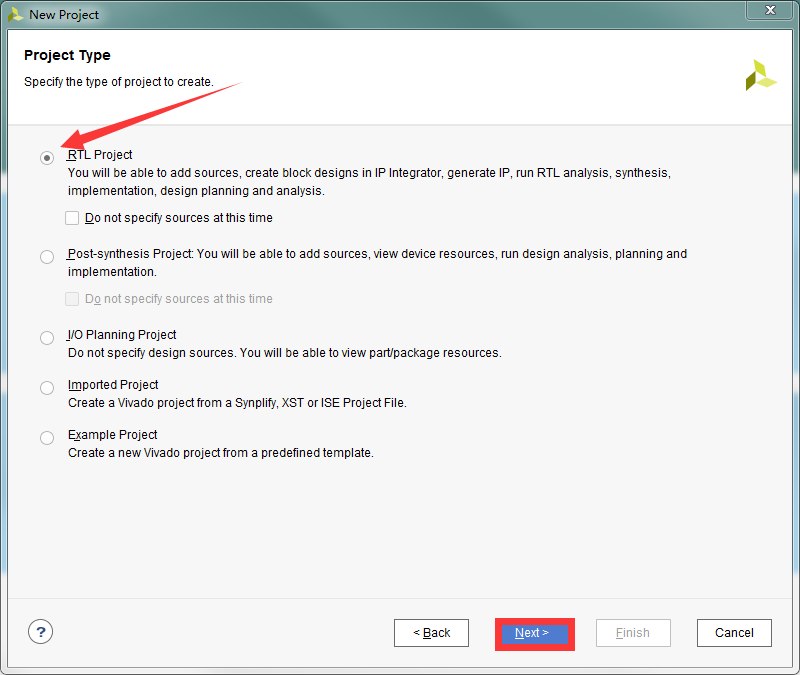

3.选择第一项:RTL Project,Next

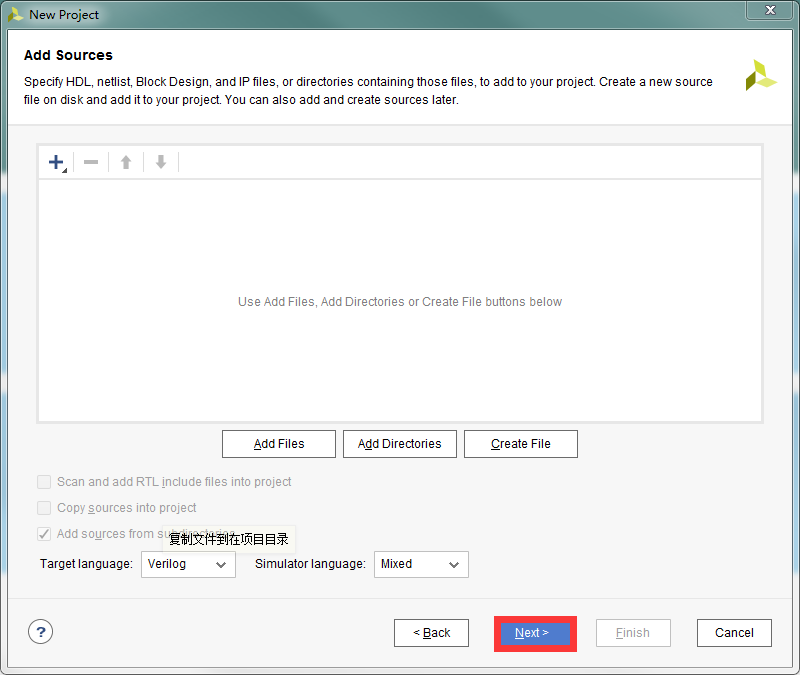

4.添加资源,可以直接Next

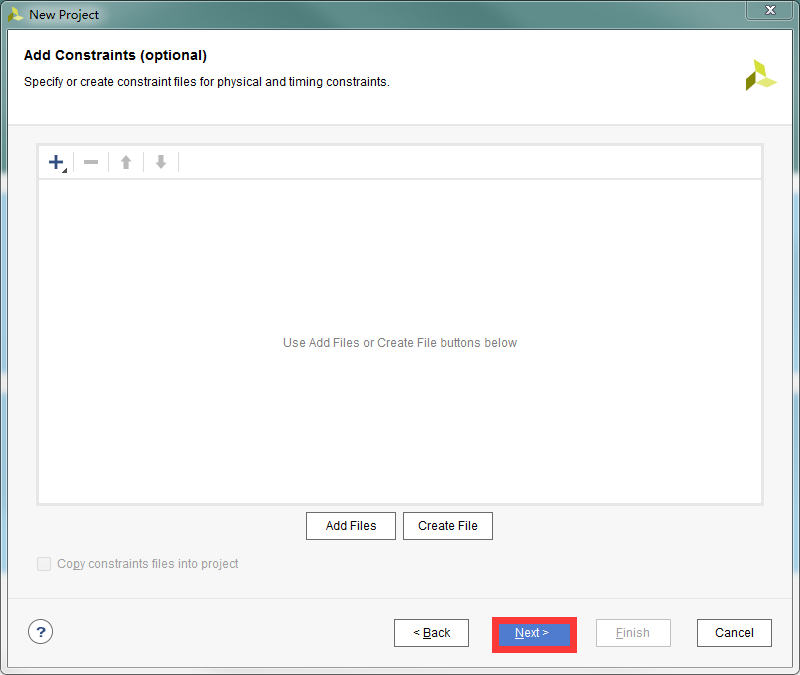

5.添加约束,可以直接Next

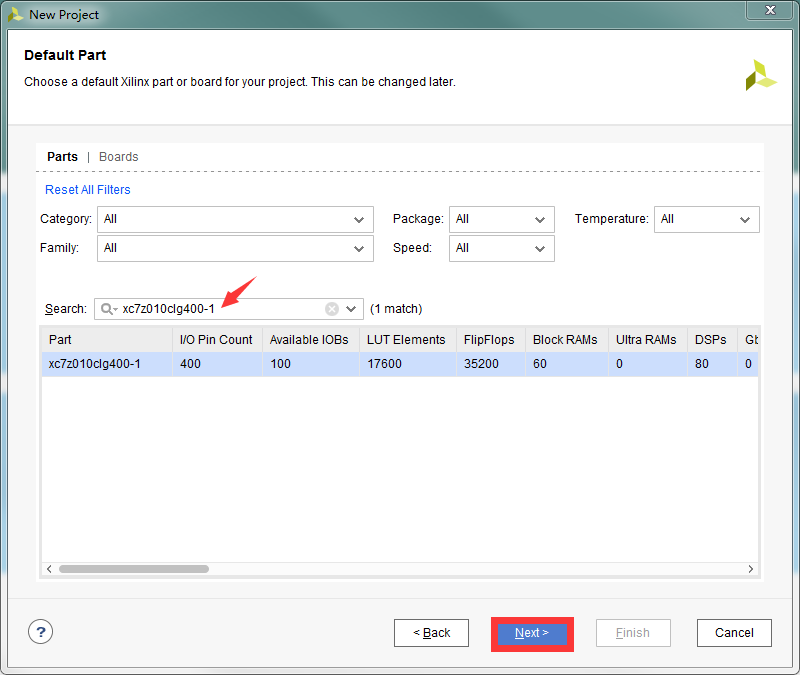

6.芯片型号选择xc7z020clg400-1,Next

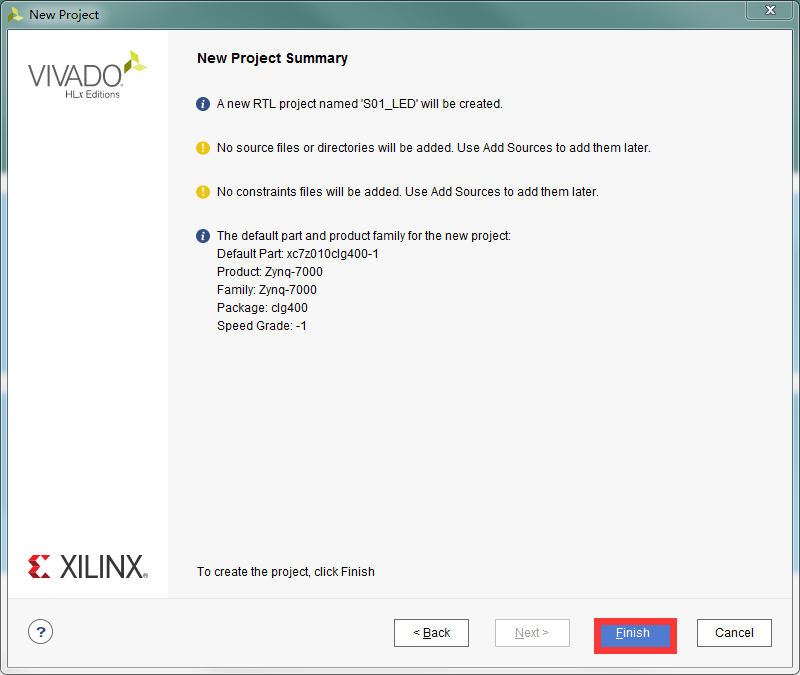

7.总结页面,Finish

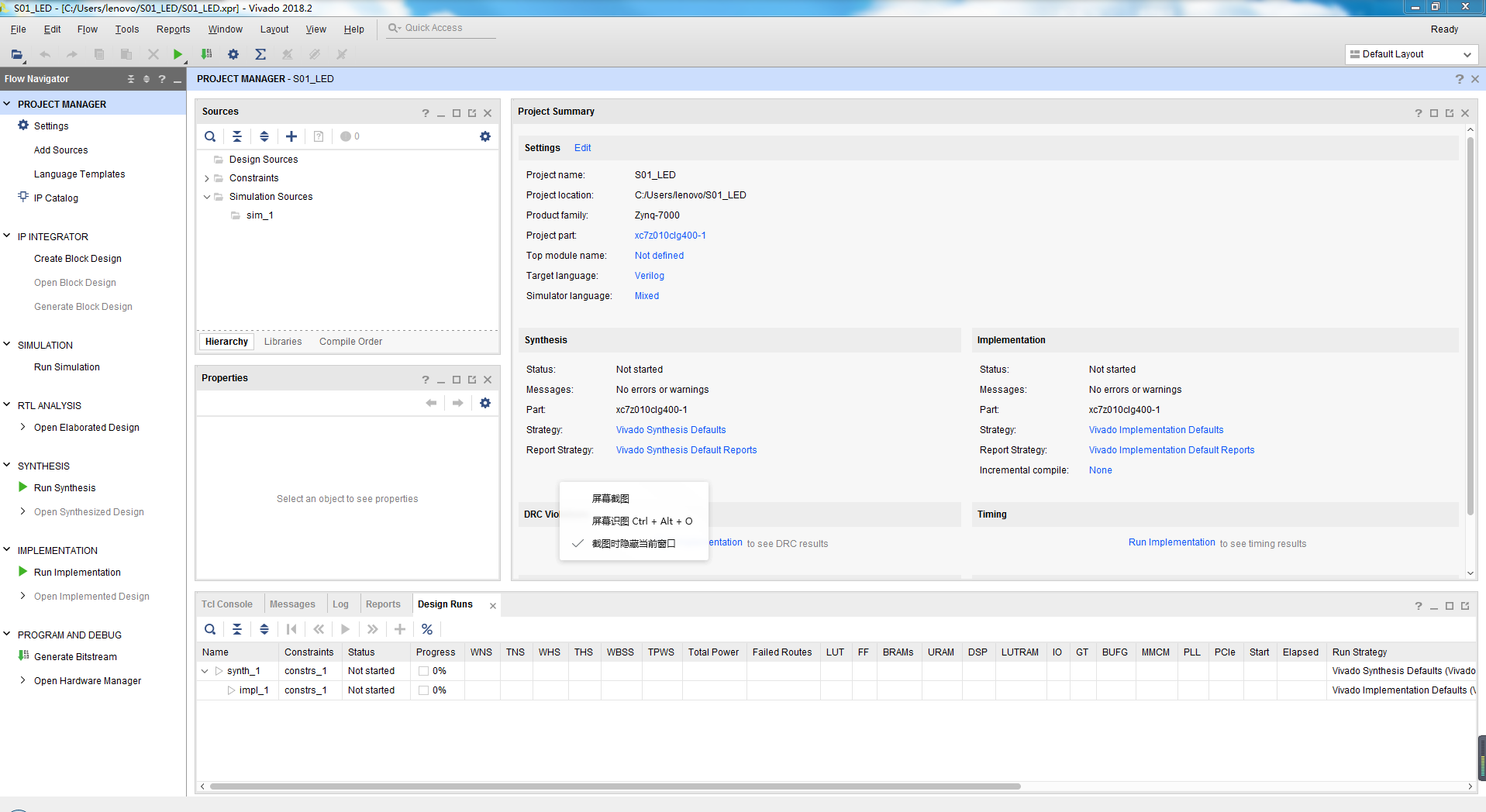

8.建好后的页面如下所示

二、PL端(FPGA)设置

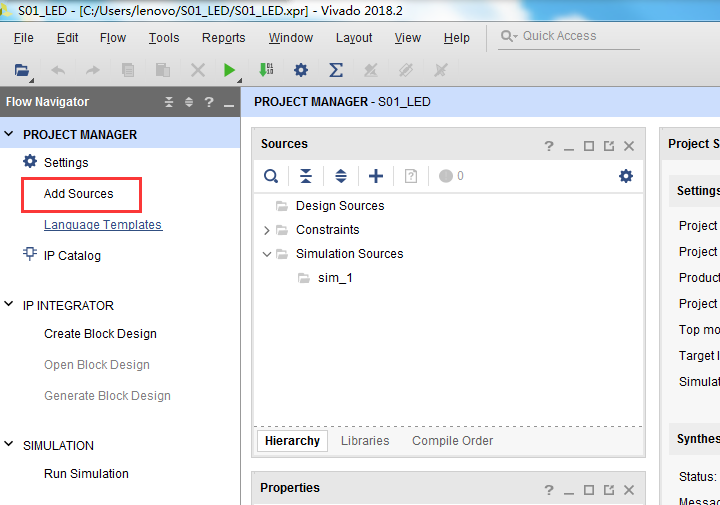

1.点击左侧导航栏的第一项PROJECT MANAGER --- Add Sources

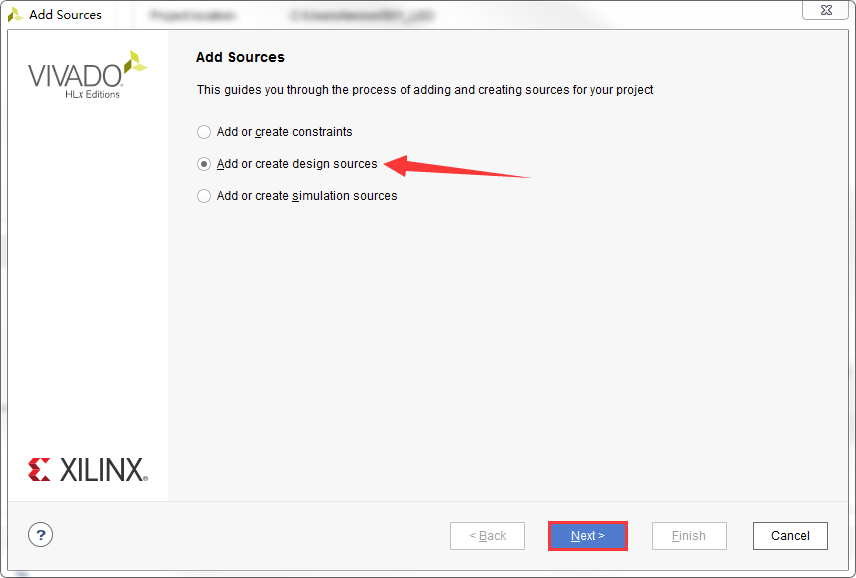

2.选择Add or create design sources,点击Next

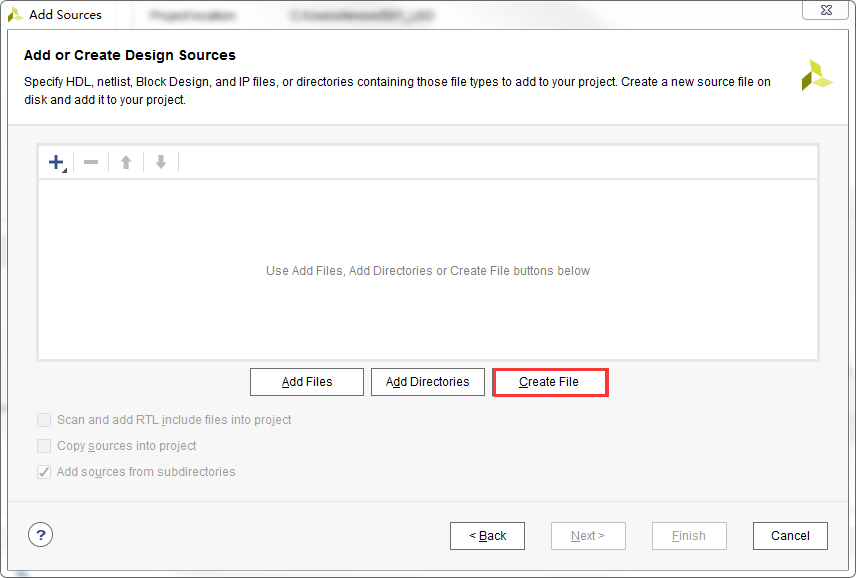

3.点击Create File来创建新的文件

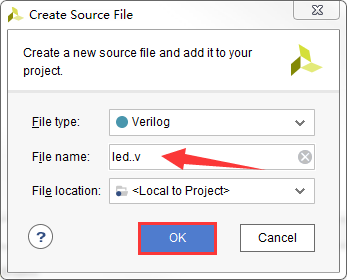

4.设置文件类型、文件名、文件位置,完了点OK

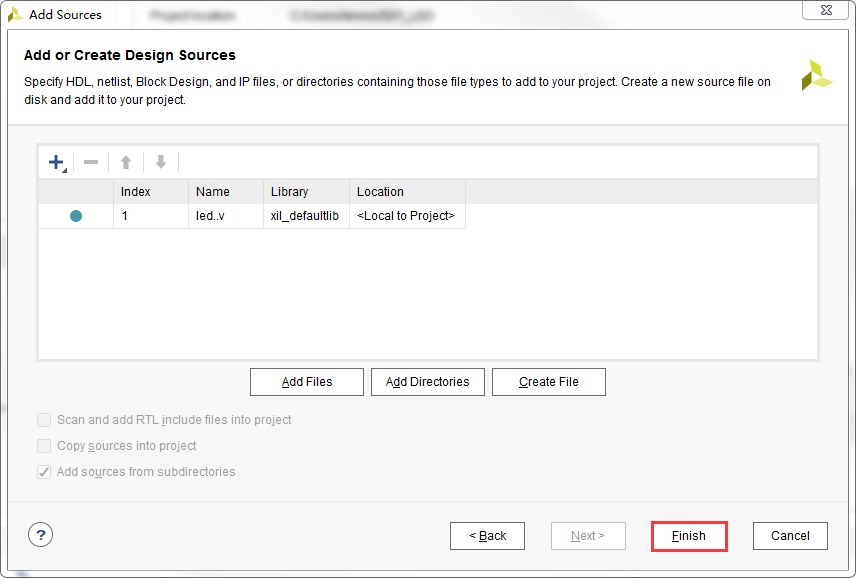

5.点击Finish

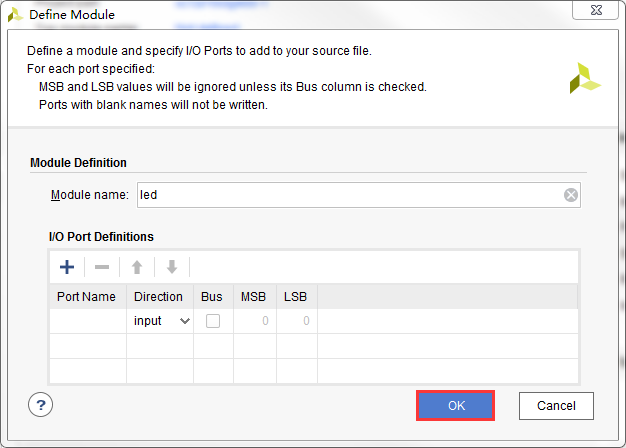

6.向导会提示定义 I/O 的端口,可以不定义,后面在程序中编写即可。

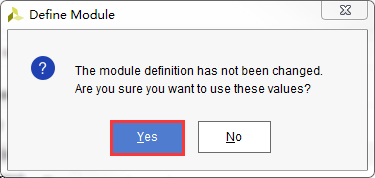

7.点击Yes

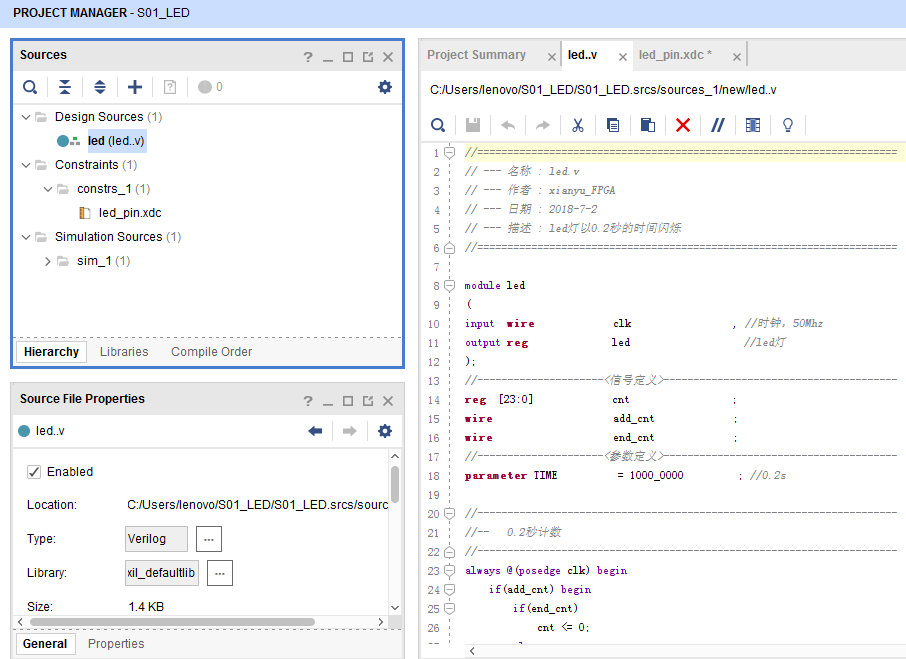

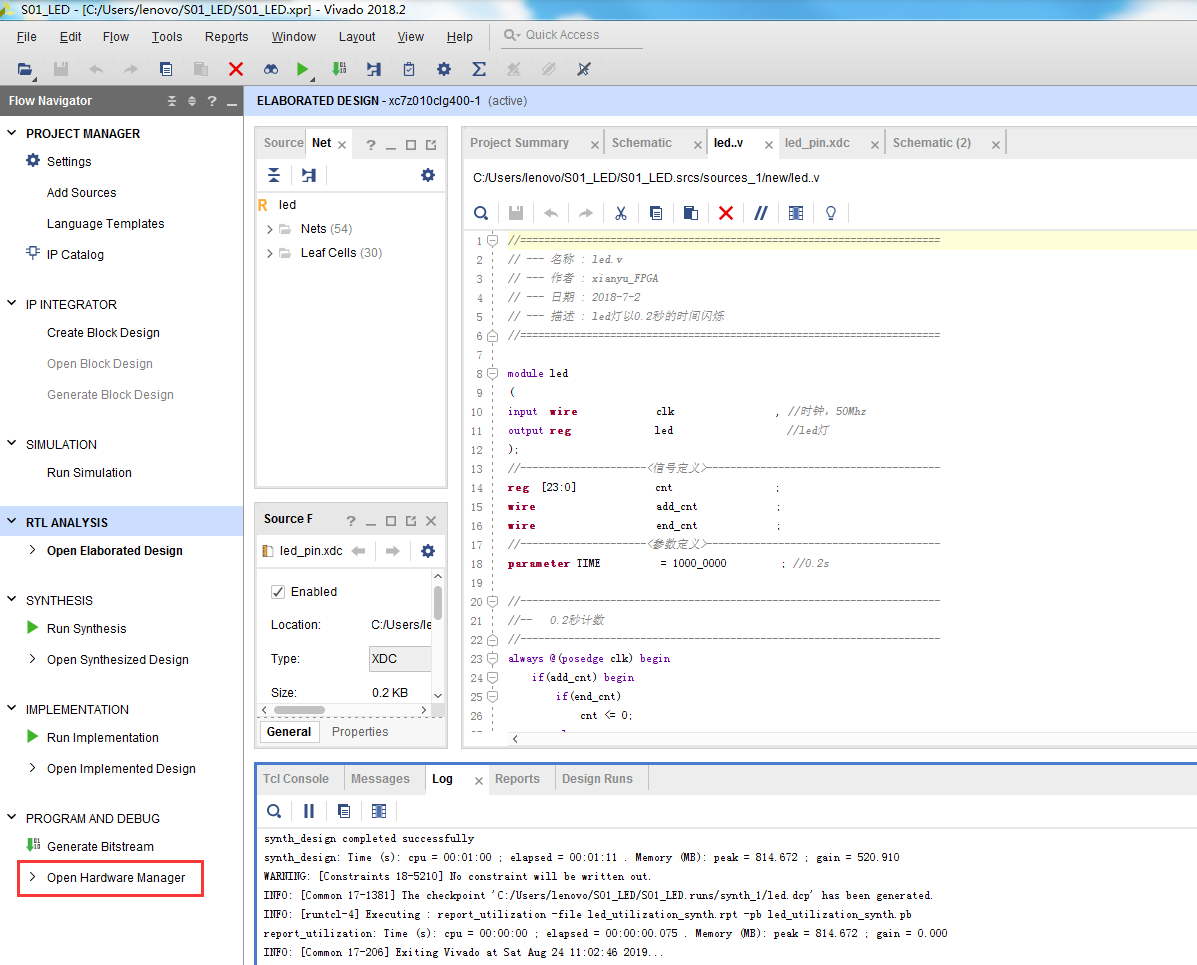

8.完成之后的页面如下所示,双击左侧 led 可以打开代码编辑页面,在里面编写Verilog代码,完成后按 Ctrl+S 保存

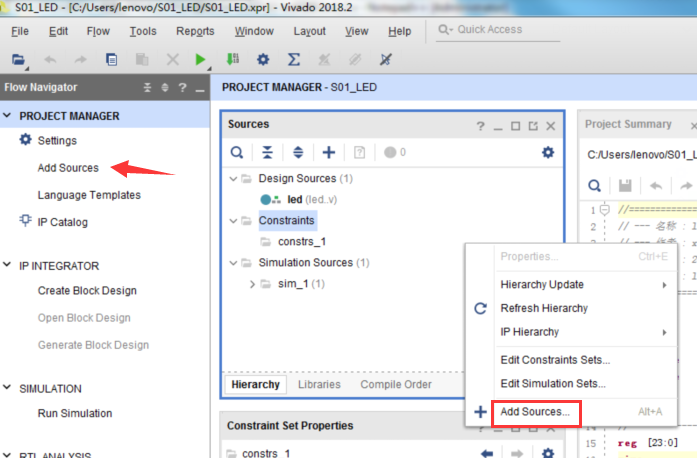

9.添加引脚约束文件,可以点击左侧导航栏的PROJECT MANAGER --- Add Sources,也可以直接在Sources空白处鼠标右键选择 Add Source

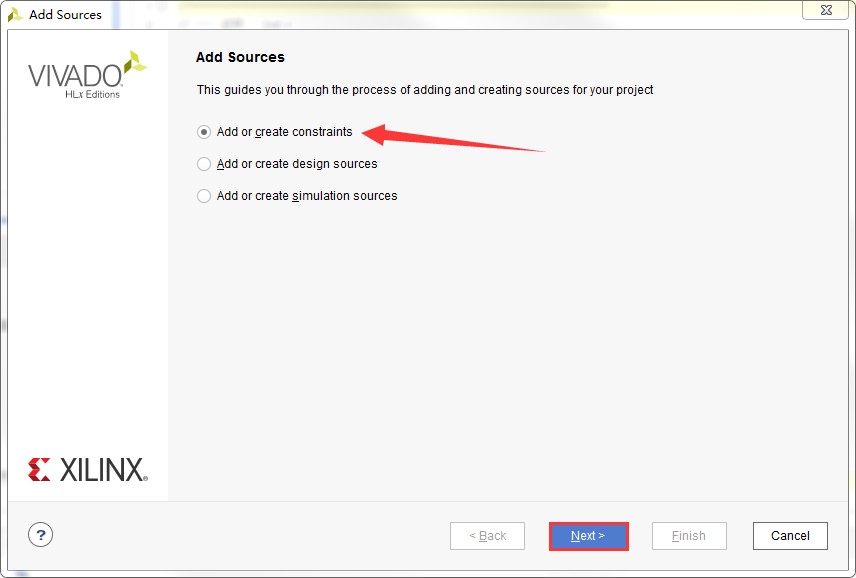

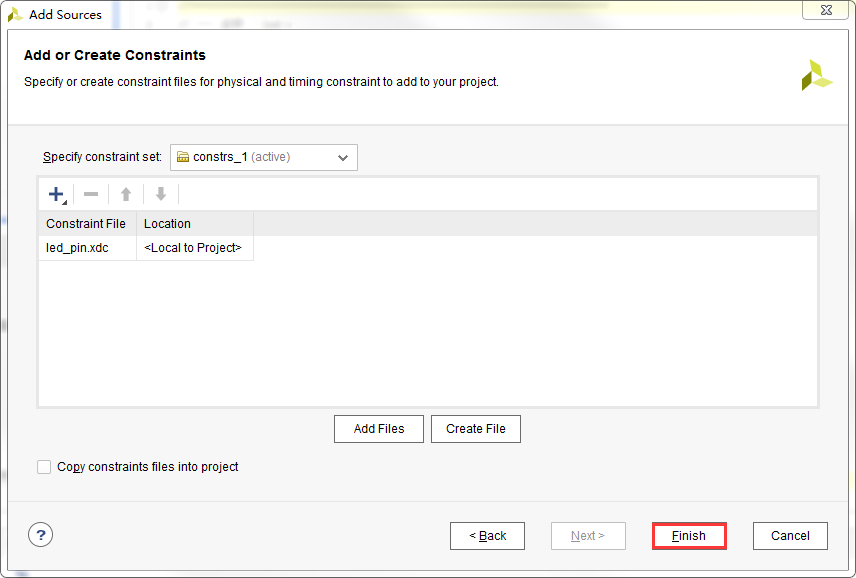

10.选择 Add or create constraints,点击Next

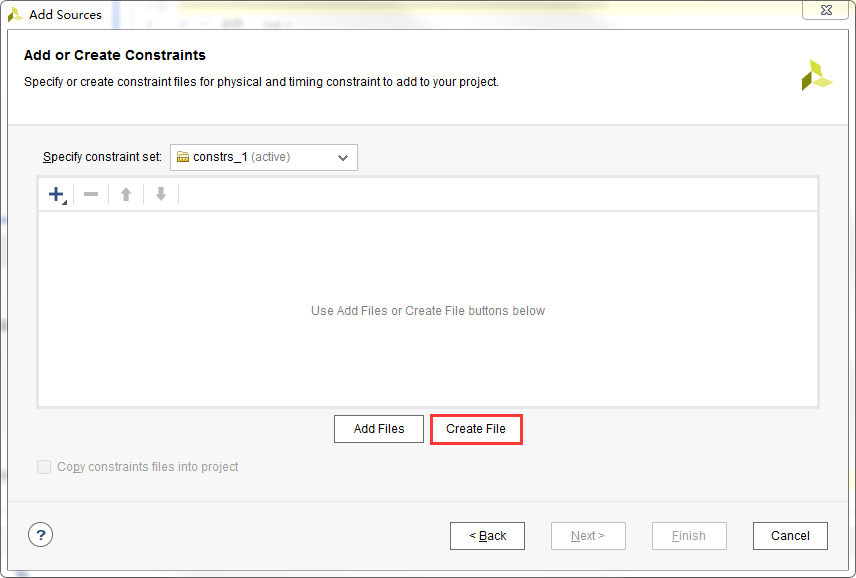

11.点击Create File来创建新的文件

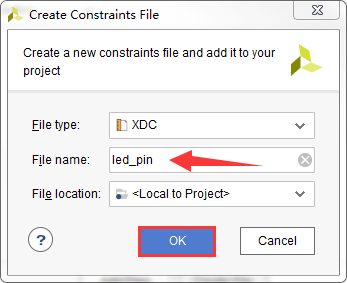

12.设置文件类型、文件名、文件位置,完了点OK

13.点击Finish

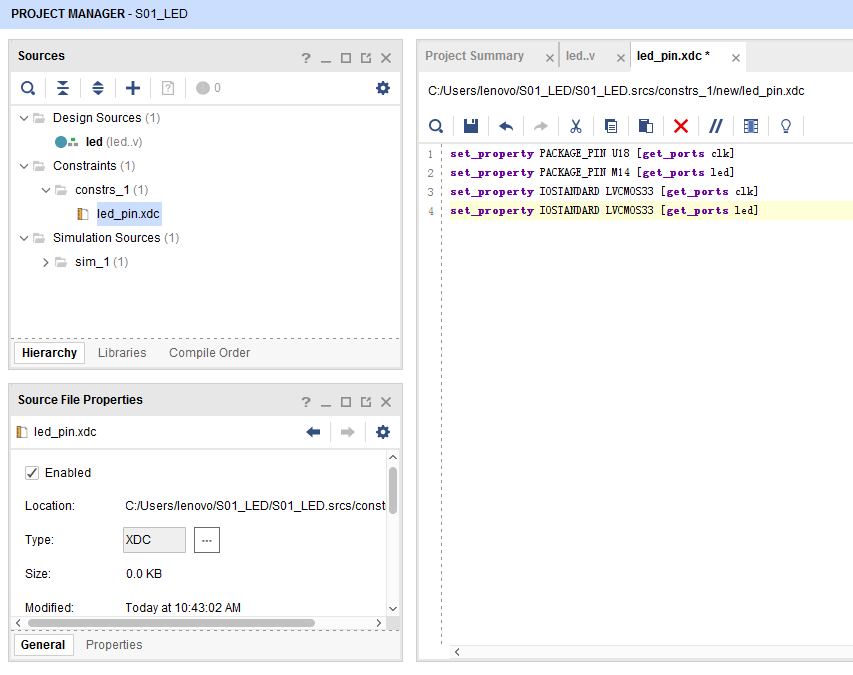

14.完成之后的页面如下所示,双击左侧 led_pin 可以打开代码编辑页面,在里面编写Tcl约束代码,完成后按 Ctrl+S 保存

最基本的XDC语法如下所示:

管脚约束:set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称”] 电平约束:set_property IOSTANDARD "电压" [get_ports “端口名称”]

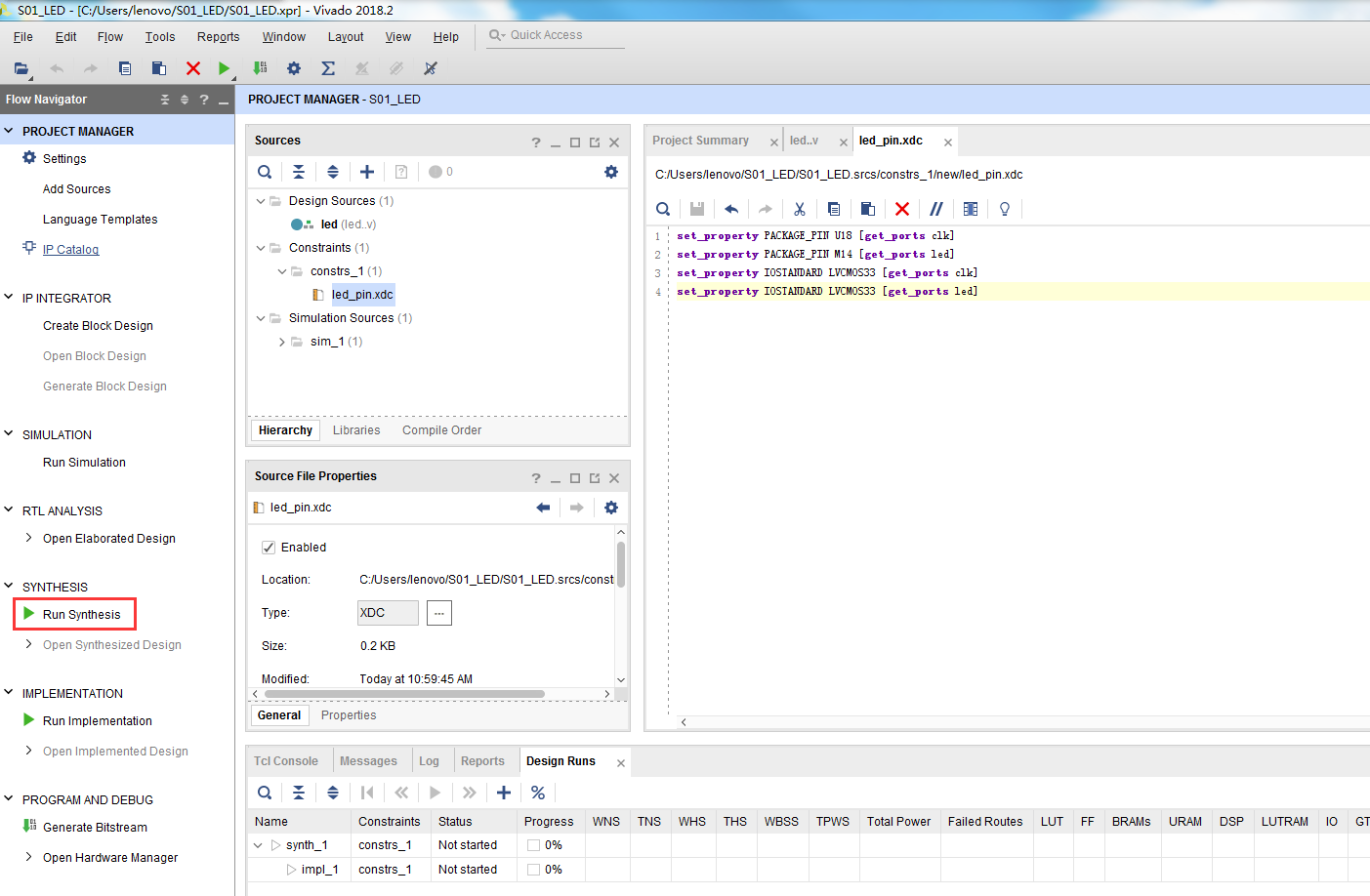

三、编译和综合

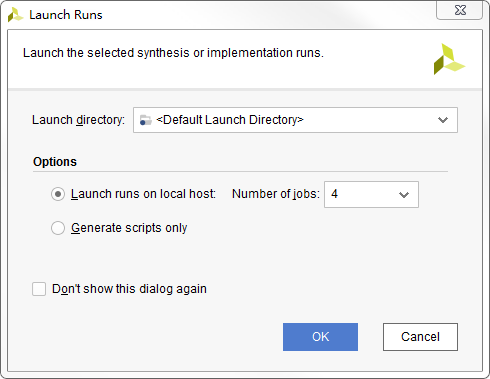

1.点击左侧导航栏的 RunSynthesis,即可开始综合并生成网表文件

2.线程按照自己电脑配置选择,一般能选多大就多大

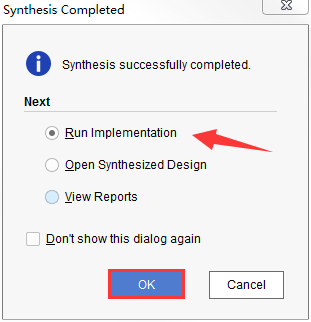

3.综合完成后弹出一个小窗口,选择 Run Implementation来开始布局布线

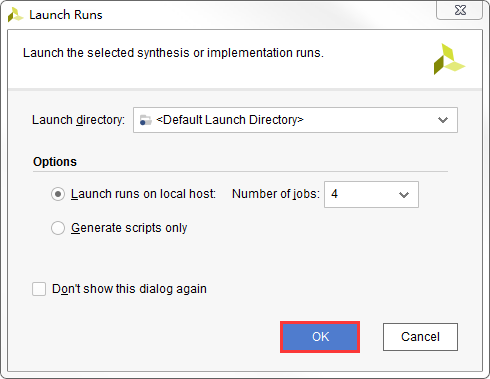

4.线程按照自己电脑配置选择,一般能选多大就多大

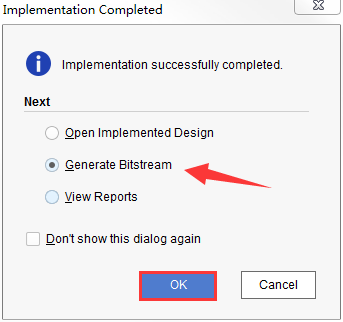

5.布线完成后弹出一个小窗口,选择 Generate Bitstream来生成下载用的bit文件

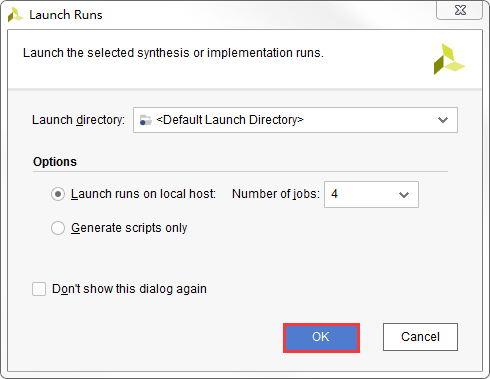

6.线程按照自己电脑配置选择,一般能选多大就多大

7.点击左侧导航栏的 Open Hardware Manager来下载bit流到板卡中

四、补充

1.编写完设计文件和约束文件后,编译和综合也可以直接点击左侧导航栏的按钮或者主页上方的快捷按钮。

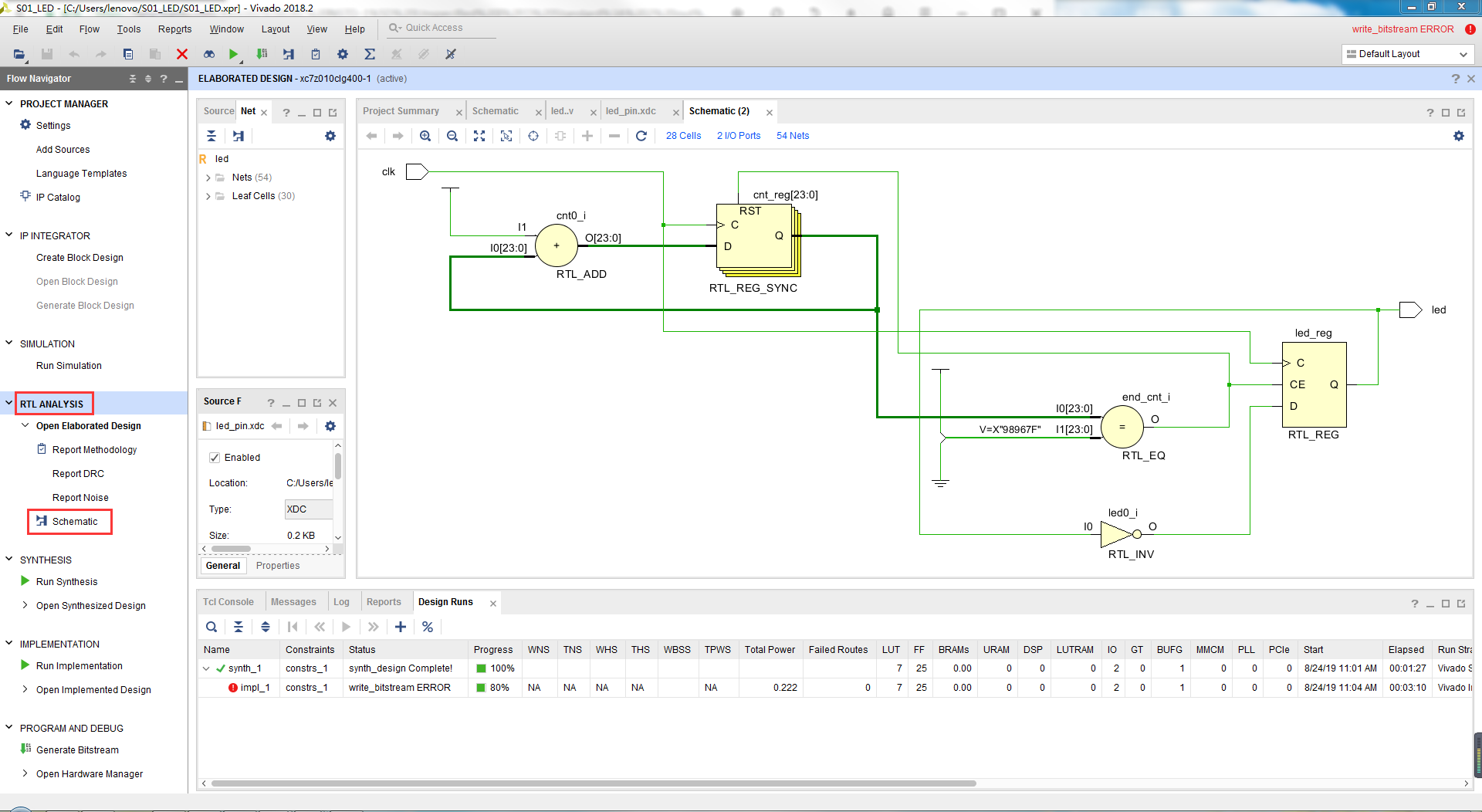

2.点击左侧导航栏的RTL ANALYSIS --- Schematic可以看到 RTL 视图,有时候 RTL 视图还是挺重要的。

3.添加约束文件可以打开RTL视图后,点击RTL视图上方的“I/O port”进行手动添加,保存后也可生成XDC文件。

参考资料:

[1]V3学院FPGA教程

[2]何宾, 张艳辉. Xilinx Zynq-7000嵌入式系统设计与实现[M]. 电子工业出版社, 2016.