【转】ISE——完整工程的建立

FPGA公司主要是两个Xilinx和Altera(现intel PSG),我们目前用的ISE是Xilinx的开发套件,现在ISE更新到14.7已经不更新了,换成了另一款开发套件Vivado,也是Xilinx的产品,intel的开发套件是Quartus II系列,我们实验室这两款公司的开发板都有,不过对于入门来说,选择ISE有两个原因,一是它比Vivado快多了,二是它和Quartus II相比不用自己写测试文件(激励)。实验室的板子这两个公司都有,代码都是可以移植的,学习的话都要学的,软件不是问题,重点是FPGA的设计思想。本篇呢就用一个实例,基于FPGA 的流水灯来介绍一下ISE的使用完整流程。

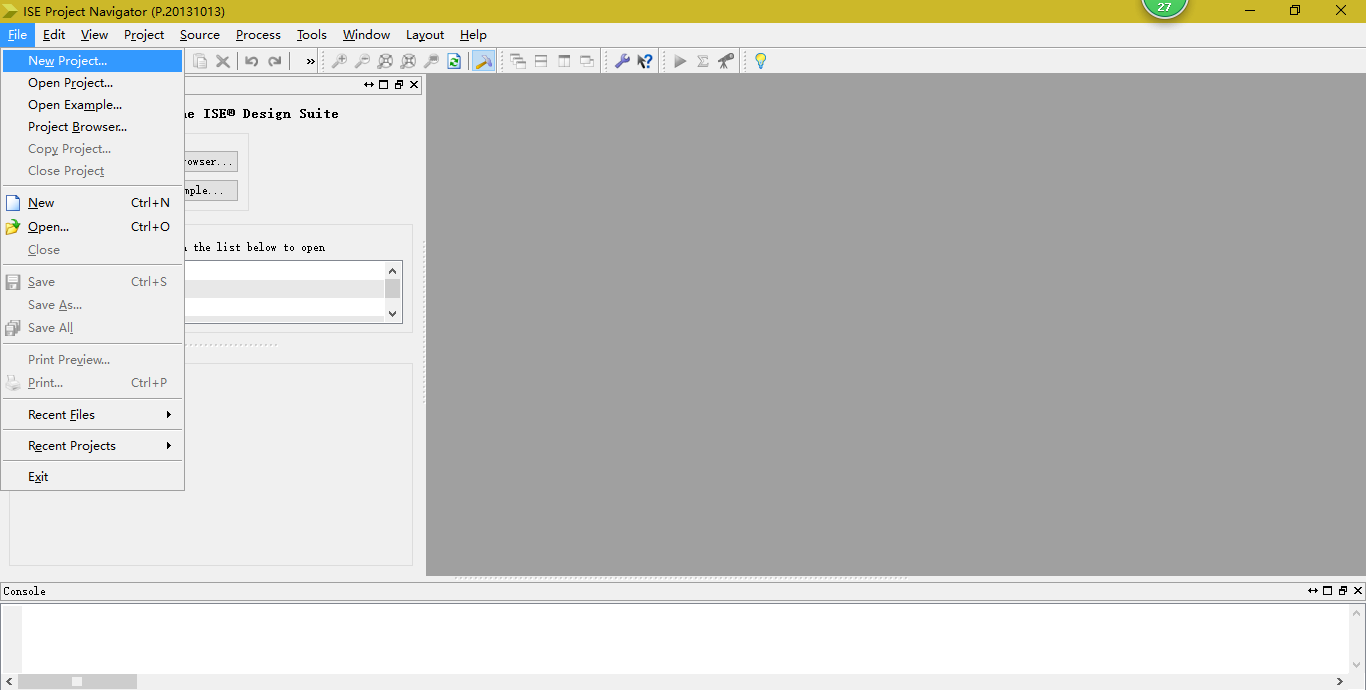

打开软件,点击file——new project。

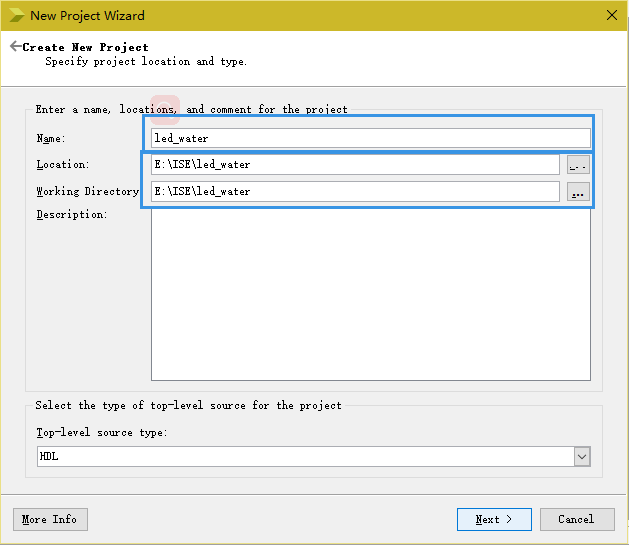

建立一个新的工程,工程名为led_water,next~。

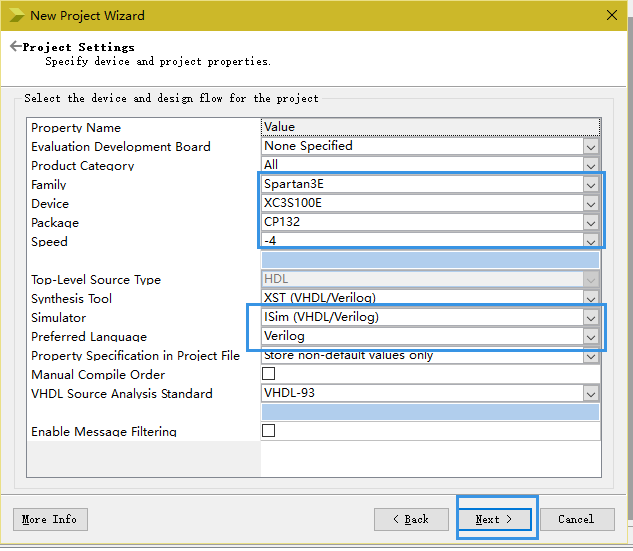

这里设置板卡信息,我使用的板子是basys2,语言为verilog HDL,next~。

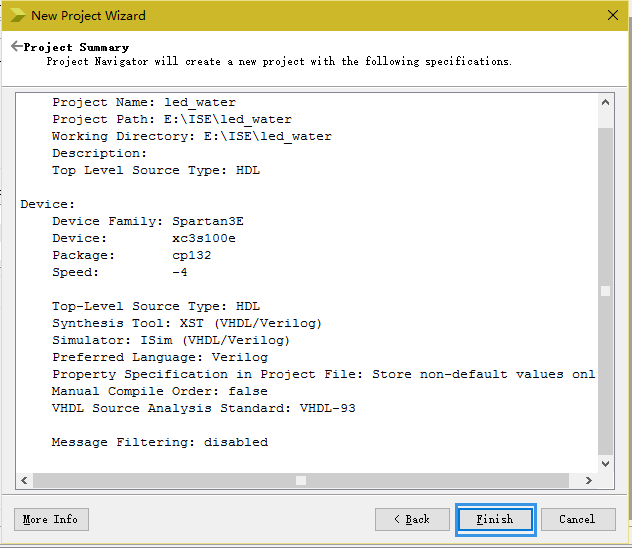

这里是总结界面,点击finish。

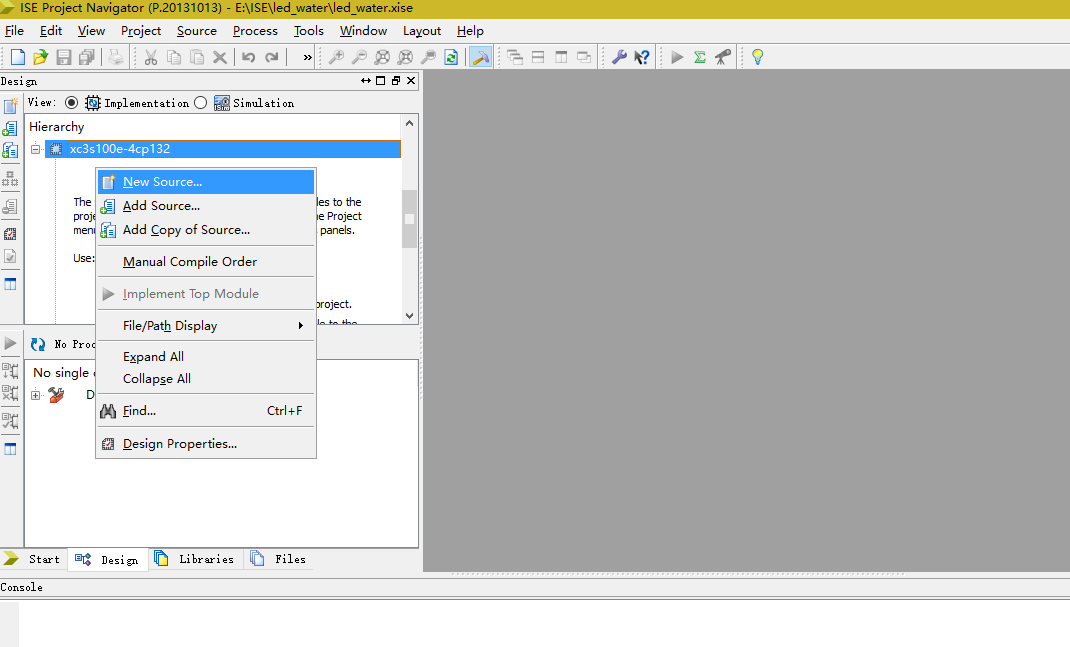

右键点击new source。

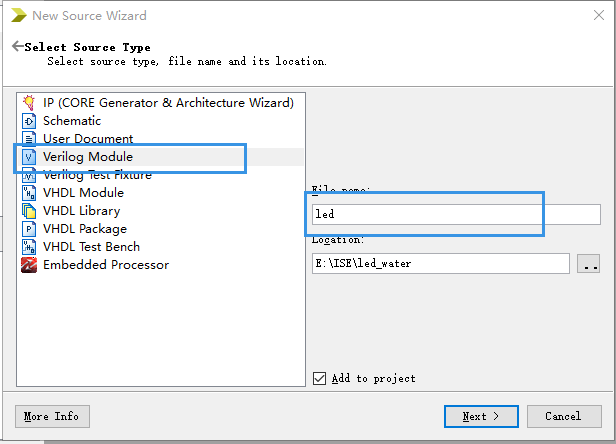

选择verilog module。文件名输入为led

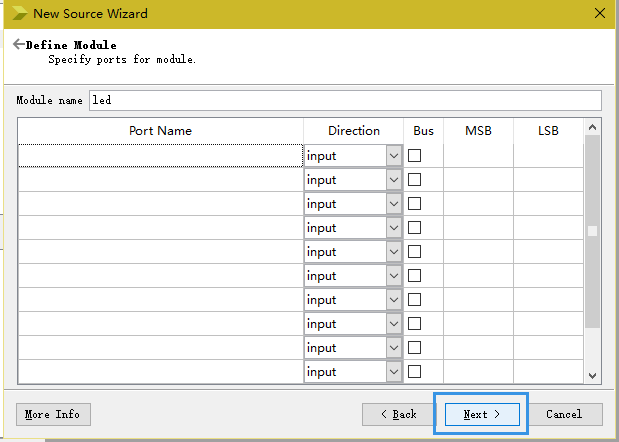

Next~

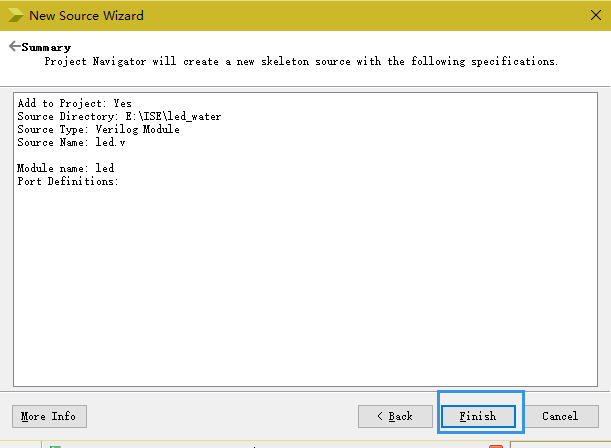

Finish~

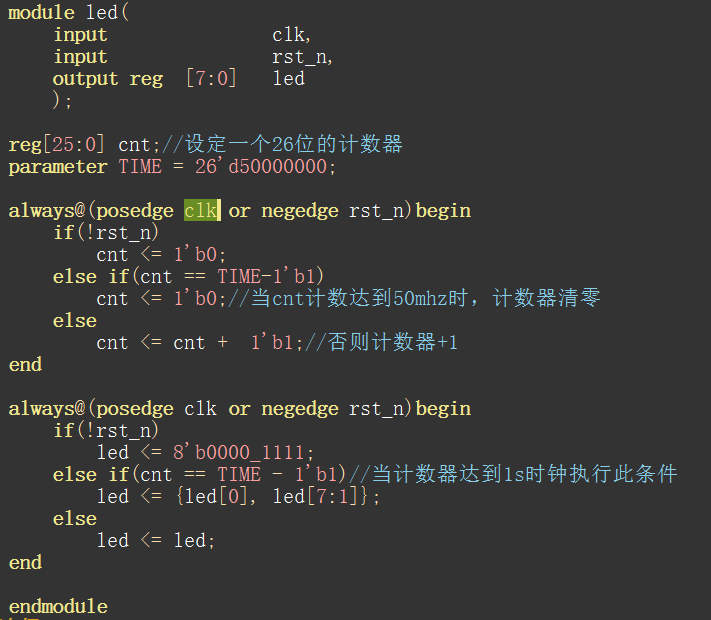

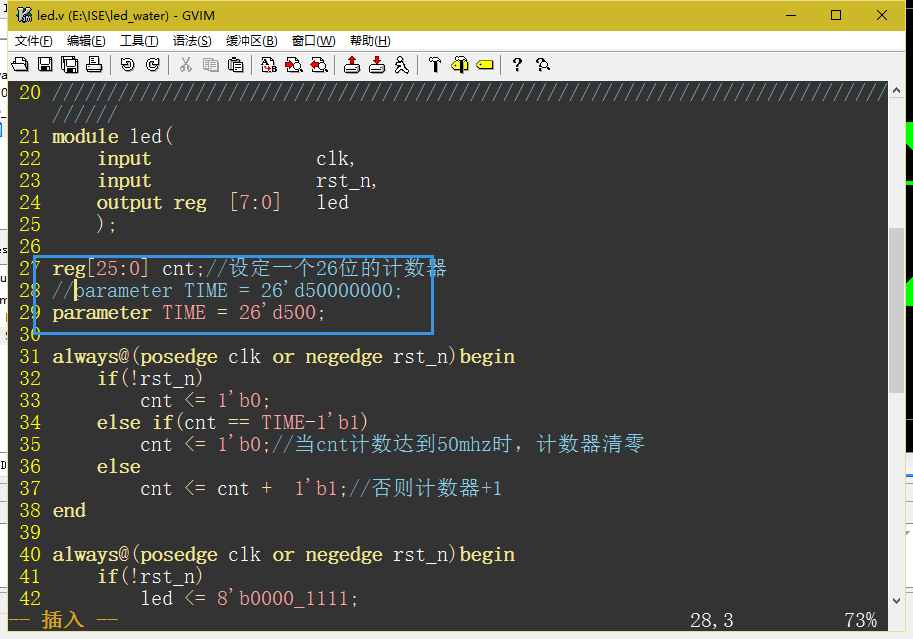

这是流水灯的代码,

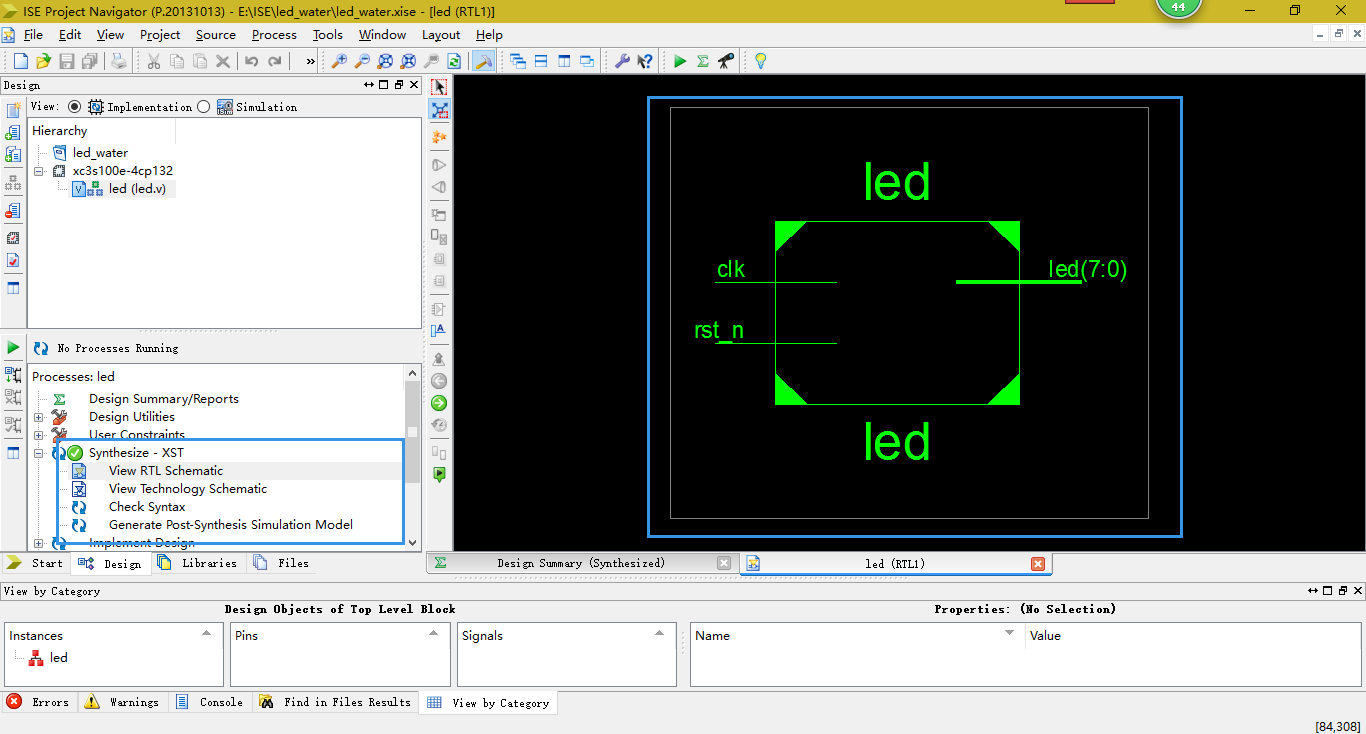

代码编写完成后,点击view RTL Schematic即可进行编译,可查看原理图。

原理图生成了,便没有语法错误,接下来尽心时序仿真,检查逻辑错误。

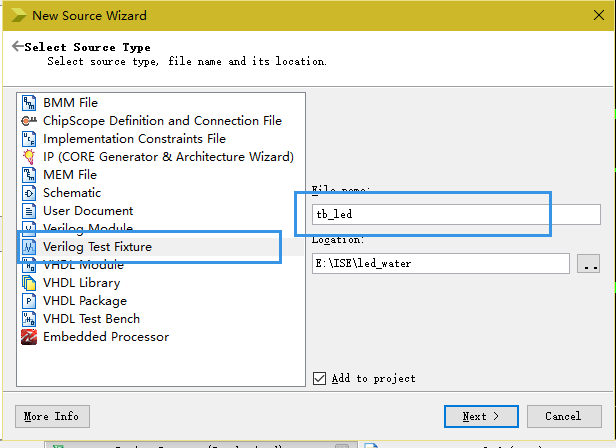

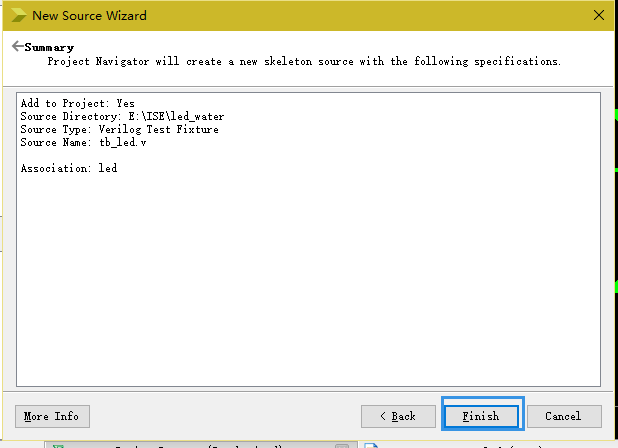

重新新建一个文件,verilog test fixture,文件名为tb_led。

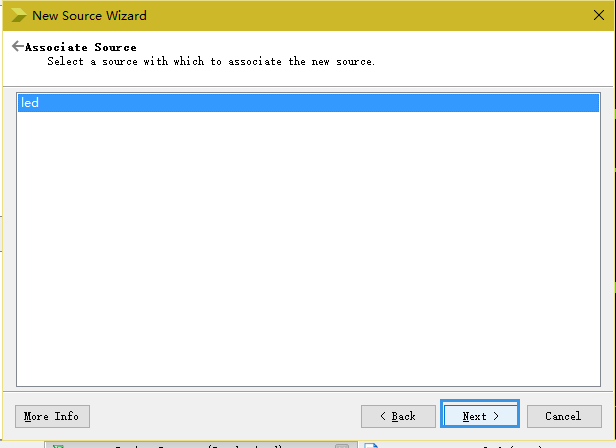

Next~

Finish。

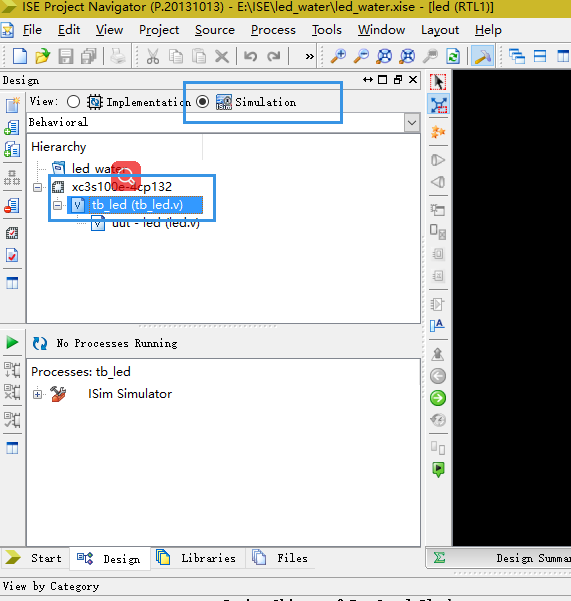

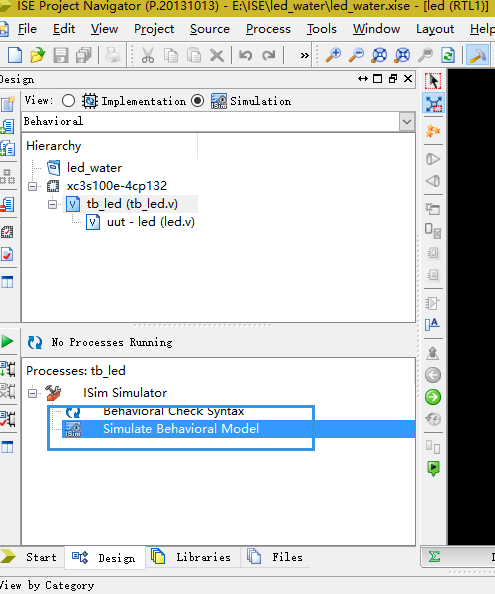

点击simulation,这是仿真界面,双击测试文件,查看代码。

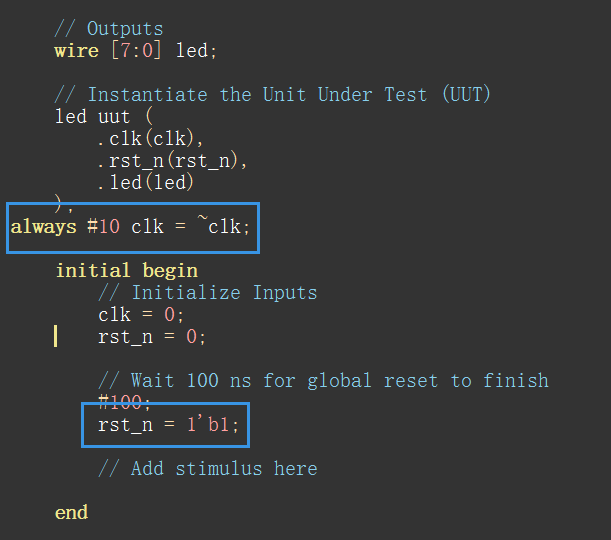

在测试文件里添加这两行代码,产生时钟,复位信号置1,电路正常工作。

为了查看仿真波形迅速,这里将代码里的计数器参数改小点。

点击simulate behavioral model,运行仿真。

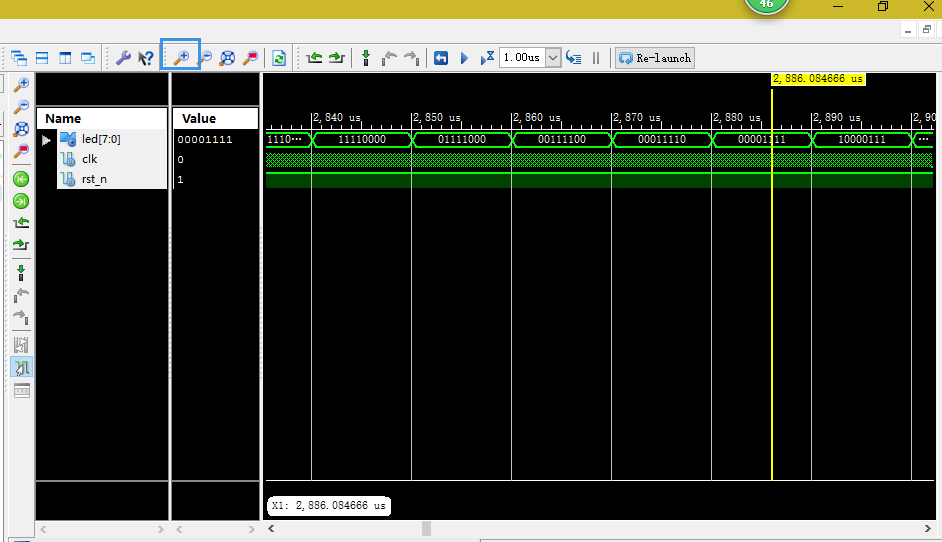

1 开始 2 暂停 3 查看波形

将波形放大查看,可以看到仿真完全正确。

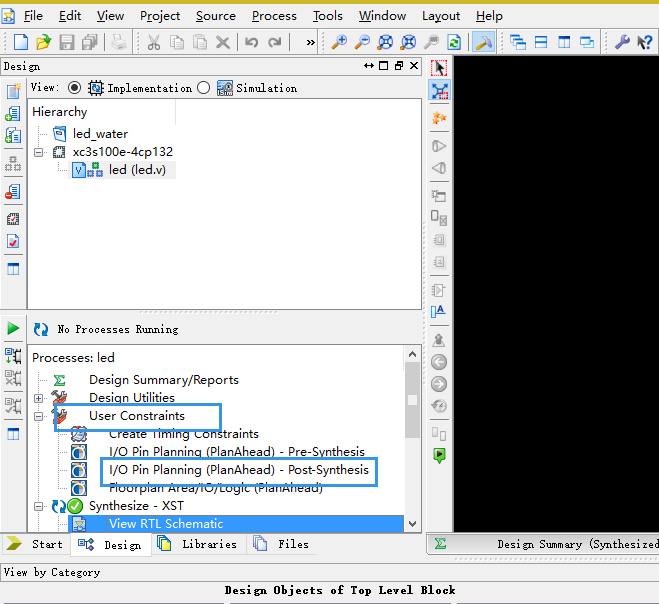

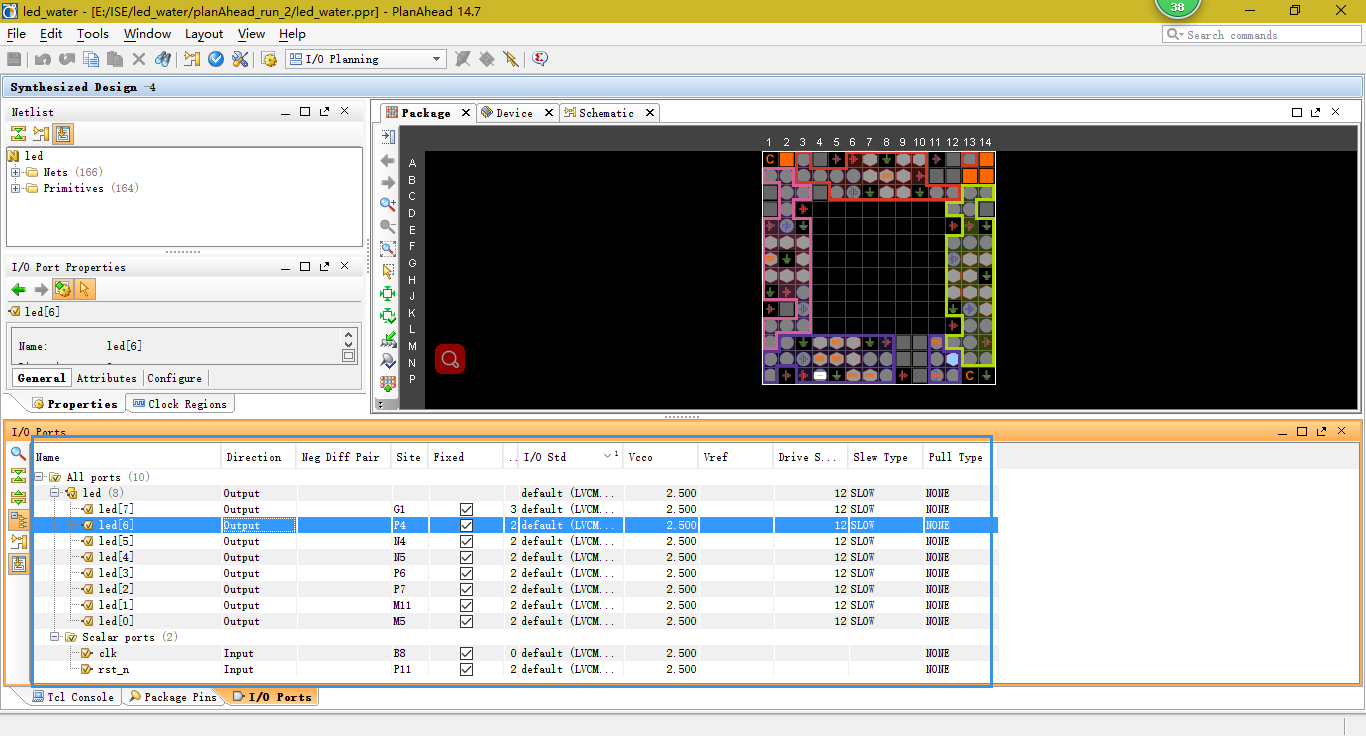

仿真正确后,就可以进行引脚约束从而进行板级仿真了。点击I/O pin planning(planahead)-post-synthesis打开引脚约束软件。

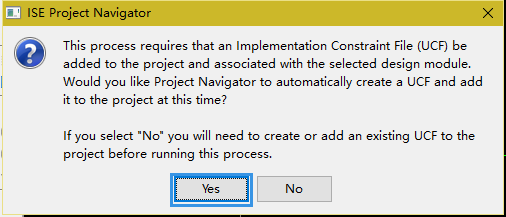

弹出的窗口点击yes。

这个界面Close~

这里就可根据板子上的引脚或手册来约束引脚。完成后点击close。

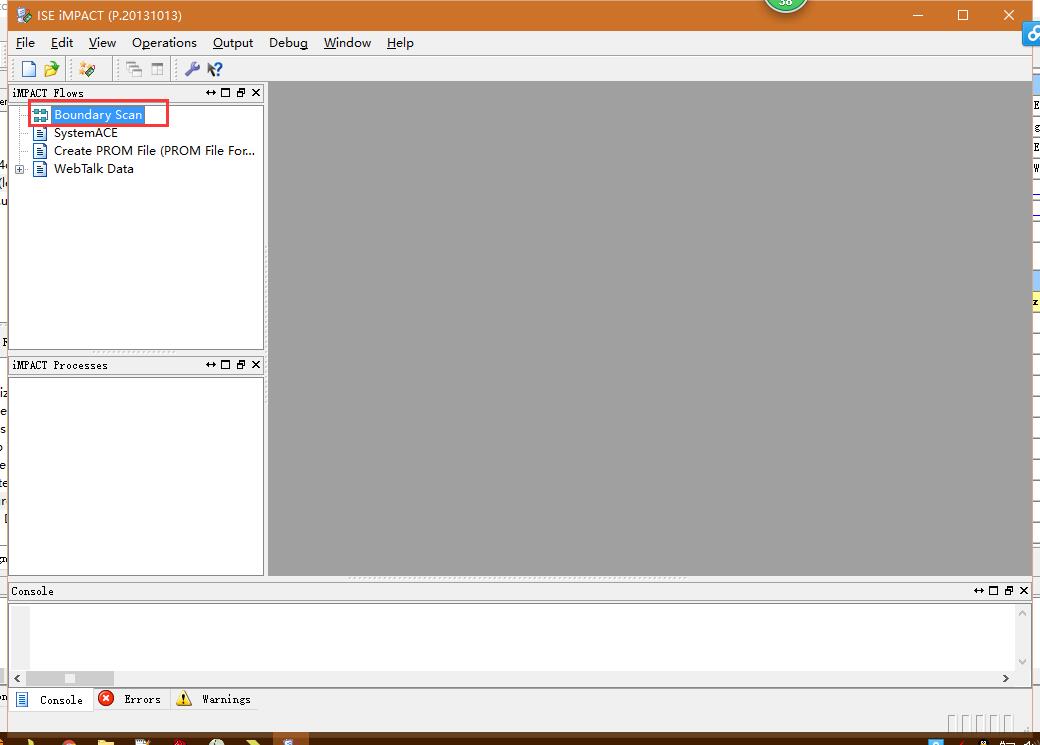

引脚约束完成后就可以综合,点击configure target device进行综合。

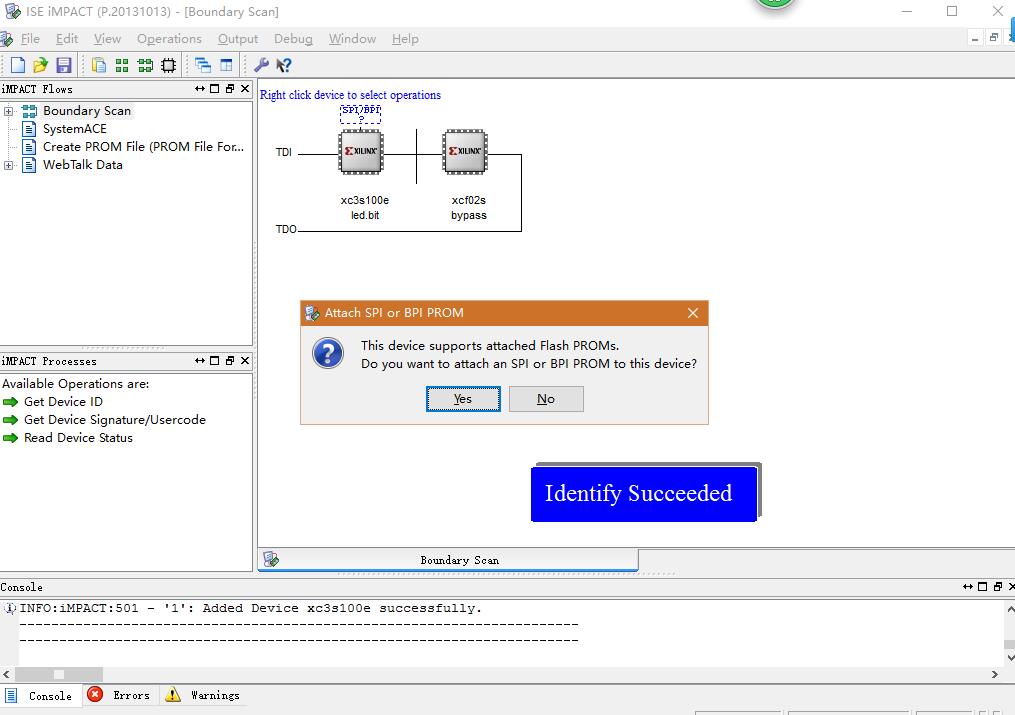

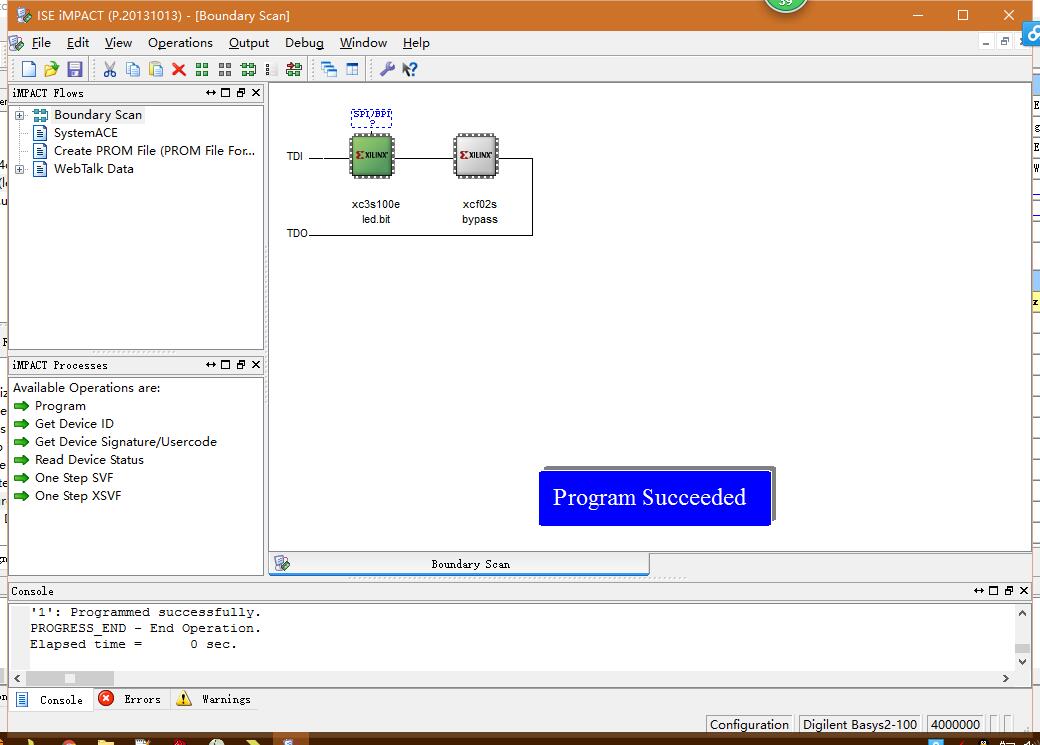

双击boundary scan

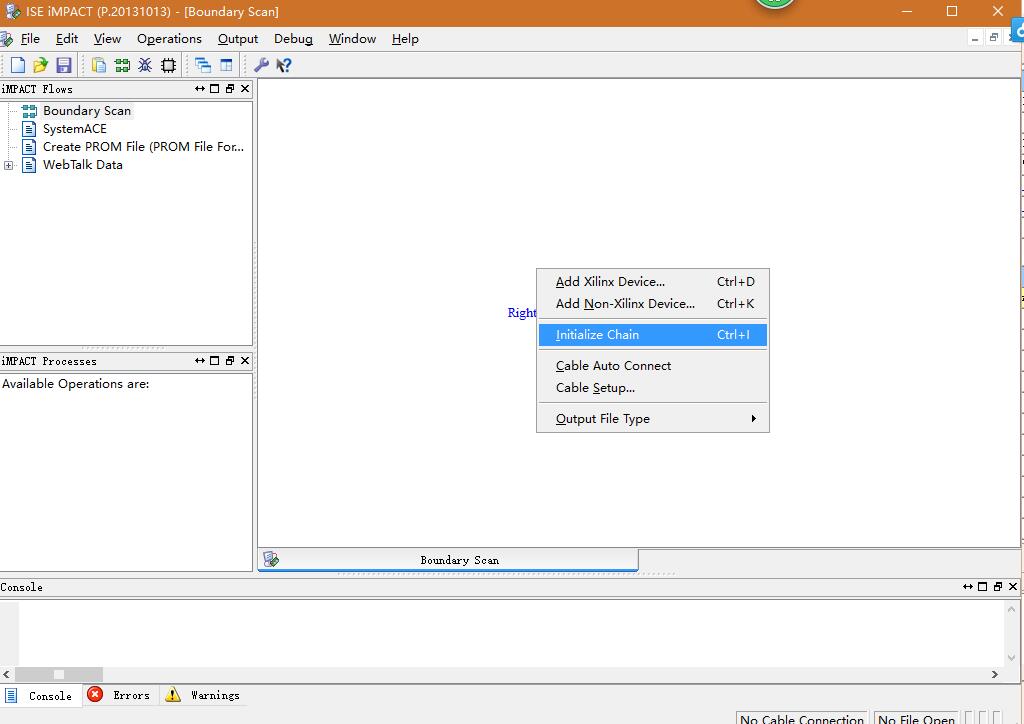

在空白处右键,然后点击initialize chain。

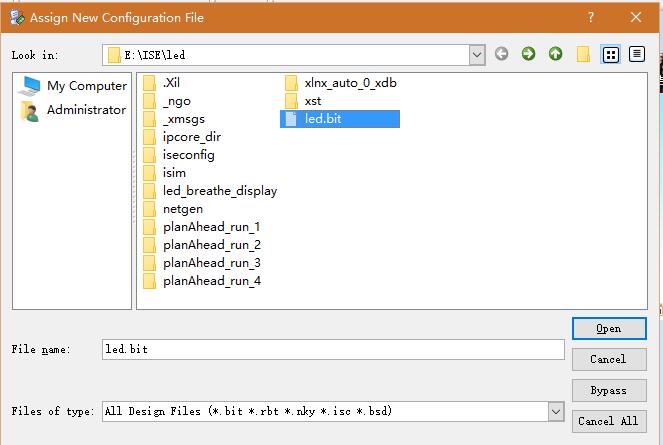

选择生成的bit文件,双击打开。

这个窗口是提示是否下载到flash中,选择no。

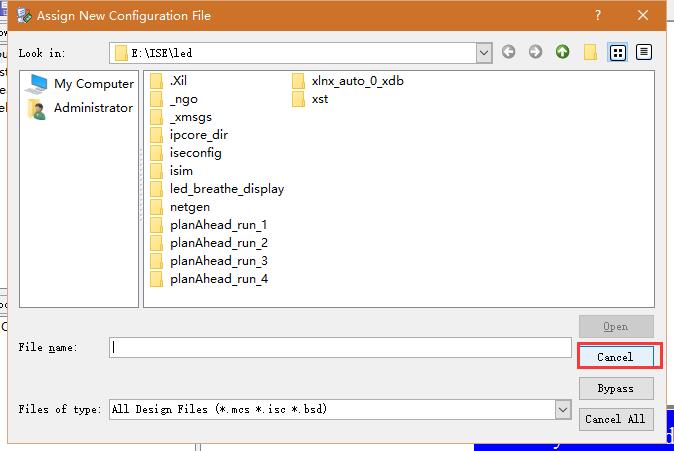

Cancel~

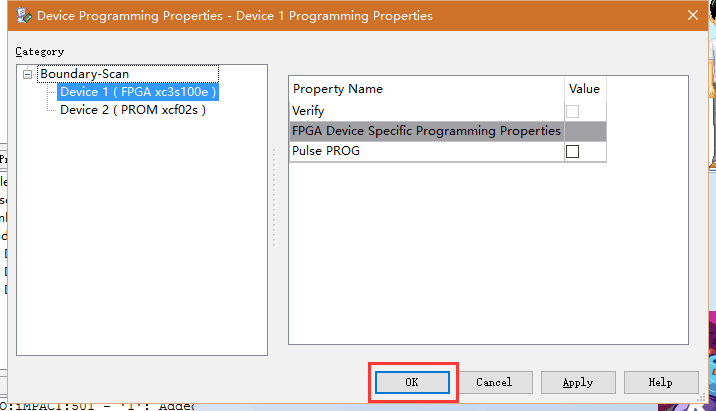

OK~

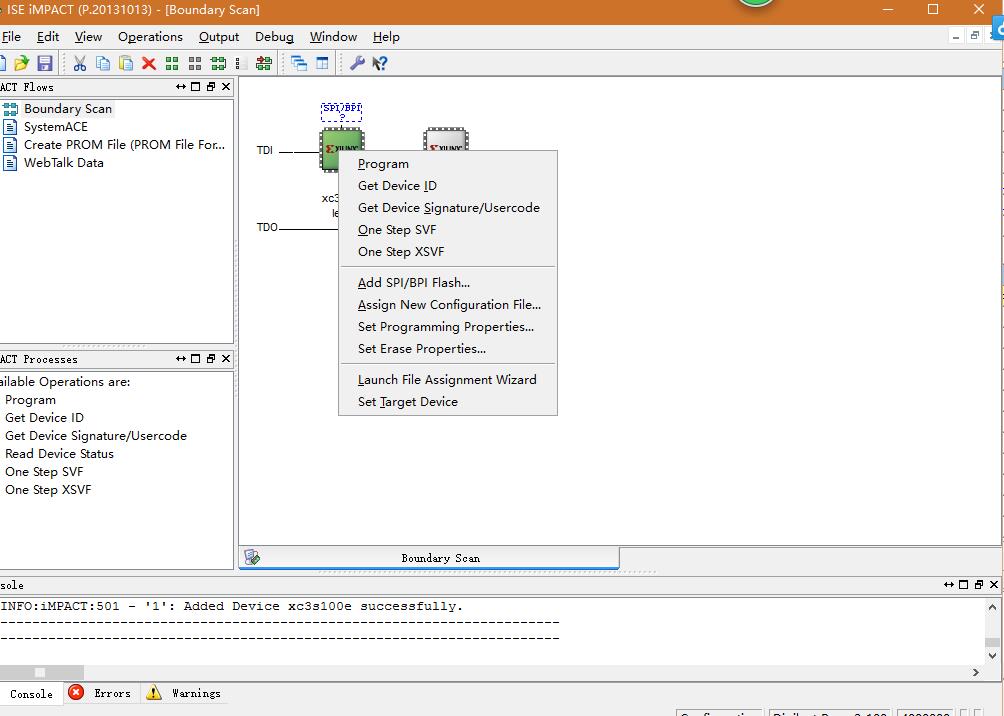

然后个界面点击program,下载bit流文件到板子上。

这样就下载成功了。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

</div>