一、代码

1 //**************************************************************************

2 // *** 名称 : div_clk.v

3 // *** 作者 : xianyu_FPGA

4 // *** 博客 : https://www.cnblogs.com/xianyufpga/

5 // *** 日期 : 2019-08-10

6 // *** 描述 : 任意整数分频,占空比为 1:2

7 //**************************************************************************

8

9 module div_clk

10 //========================< 参数 >==========================================

11 #(

12 parameter DIV = 2 //分频系数(奇偶任意)

13 )

14 //========================< 端口 >==========================================

15 (

16 input wire clk , //时钟,50Mhz

17 input wire rst_n , //复位,低电平有效

18 output wire div_clk //分频时钟

19 );

20 //========================< 信号 >==========================================

21 reg [31:0] pos_cnt ;

22 wire pos_clk ;

23 reg [31:0] neg_cnt ;

24 wire neg_clk ;

25 //==========================================================================

26 //== clk上升沿分频

27 //==========================================================================

28 always @(posedge clk or negedge rst_n) begin

29 if(!rst_n)

30 pos_cnt <= 0;

31 else if(pos_cnt == DIV - 1)

32 pos_cnt <= 0;

33 else

34 pos_cnt <= pos_cnt + 1;

35 end

36

37 assign pos_clk = (pos_cnt < DIV/2) ? 0 : 1;

38 //==========================================================================

39 //== clk下降沿分频

40 //==========================================================================

41 always @(negedge clk or negedge rst_n) begin

42 if(!rst_n)

43 neg_cnt <= 0;

44 else if(neg_cnt == DIV - 1)

45 neg_cnt <= 0;

46 else

47 neg_cnt <= neg_cnt + 1;

48 end

49

50 assign neg_clk = (neg_cnt < DIV/2) ? 0 : 1;

51 //==========================================================================

52 //== 奇偶判断后,输出正确的分频

53 //==========================================================================

54 assign div_clk = DIV[0] ? (pos_clk & neg_clk) : pos_clk;

55

56

57 endmodule

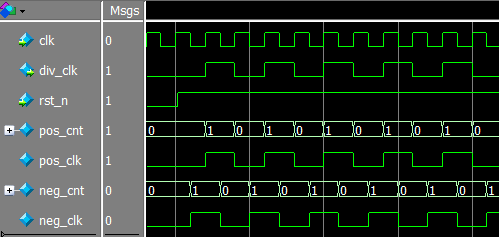

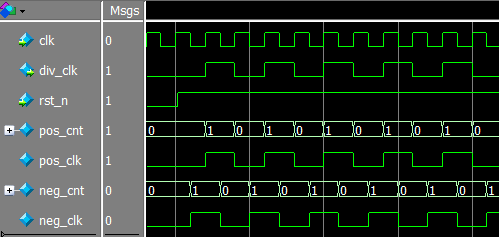

二、仿真情况

1、DIV=2时

2、DIV=3时