时序分析(1):时序约束原理(旧版、可能有错)

一、时序原理

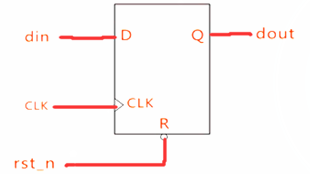

1.建立时间和保持时间

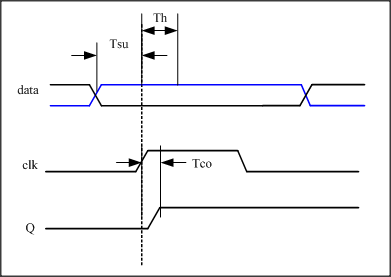

(1)建立时间Tsu:set up time,触发器的时钟上升沿到来以前,数据必须准备好的时间,如果建立时间不足,数据将不能在这个时钟上升沿被稳定的打入触发器。

(2)保持时间Th:hold time,触发器的时钟上升沿到来以后,数据被锁存消化的时间。如果保持时间不足,数据将不能在这个时钟上升沿被稳定的打入触发器。

(3)建立/保持时间是D触发器的一个固有属性,是确定的、不变的。

(4)解决建立时间不足的方法是“减少延时”,而解决保持时间不足的方法是“增加延时”。

(5)FPGA所有时序问题,根本原因都是“建立时间和保持时间”的问题。

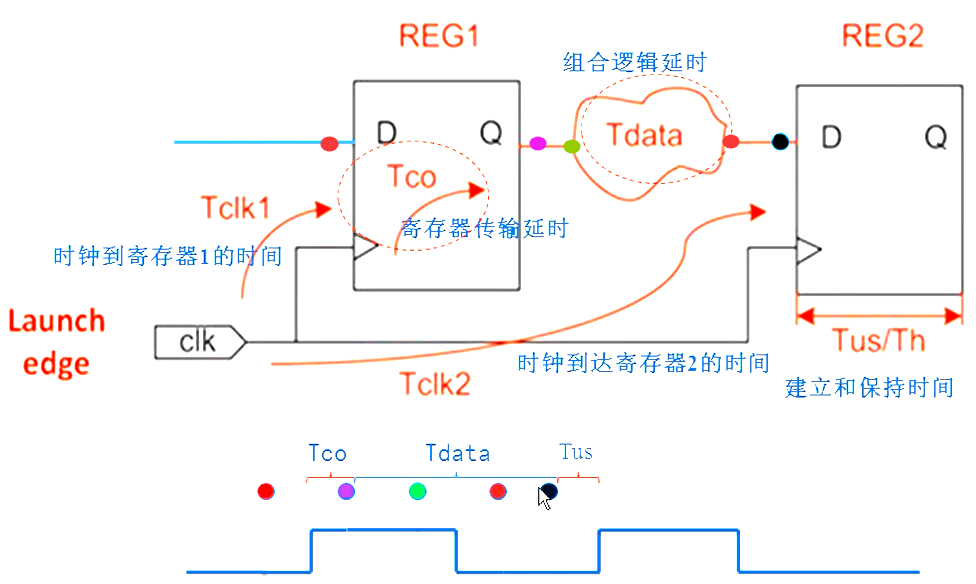

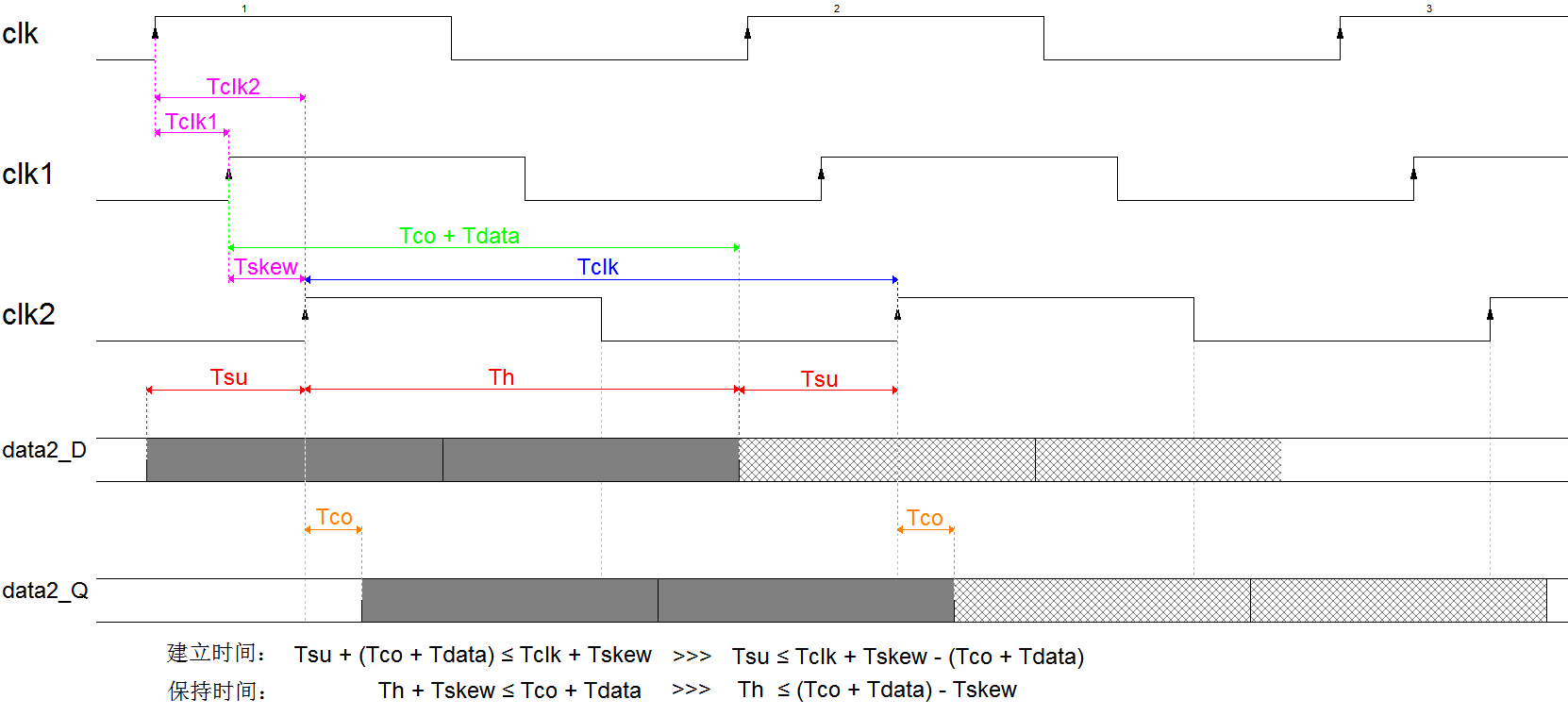

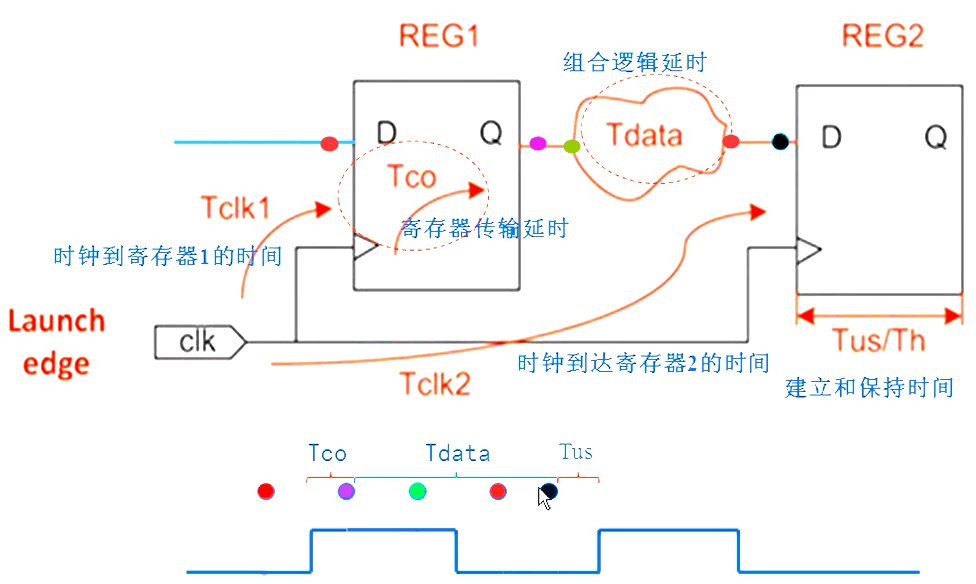

现在来仔细分析一下:

|

信号 |

含义 |

信号 |

含义 |

|

clk |

系统时钟 |

Tclk |

时钟周期 |

|

clk_1 |

源寄存器对应时钟 |

Tclk1 |

时钟到源寄存器REG1的时间 |

|

clk_2 |

目的寄存器对应时钟 |

Tclk2 |

时钟到目的寄存器REG2的时间 |

|

data2_D |

目的寄存器D端数据 |

Tskew |

时钟偏移时间:Tclk2 - Tclk1 |

|

data2_Q |

目的寄存器Q端数据 |

Tco |

数据在寄存器内部传输的时间 |

|

Tsu |

建立时间 |

Tdata |

数据的组合逻辑传输的时间 |

|

Th |

保持时间 |

|

|

注: ①实际时序还涉及“启动沿”、“锁存沿、”“数据到达时间”、“数据需求时间”等概念,但是不方便绘图了,而且上图已经能够粗略解释建立时间和保持时间了。

②上图Tco画在寄存器REG2中,只是为了方便理解概念而已,实际上寄存器REG1也有Tco。

③上图描绘的是极端情况,即:时钟周期Tclk = 建立时间Tsu + 保持时间Th。

④去除时钟偏移Tskew,可得最小时钟周期Tclk(min) = Tco + Tdata + Tsu,这是最快时间,其倒数即为最高时钟频率。

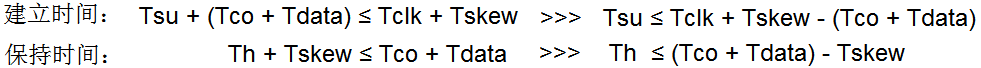

⑤按照上图时序,若要保证有时间富余,可得建立时间和保持时间的满足公式:

2.电路的延时

(1)理论状态

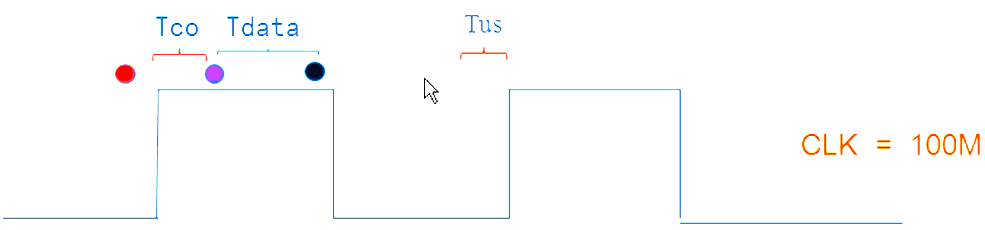

(2)实际状态

中间有时间富余

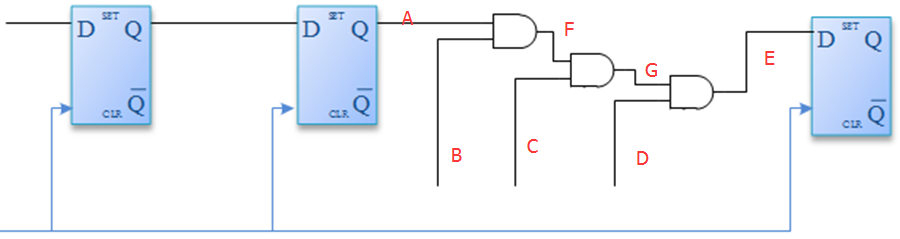

3.关键路径

(1)关键路径:延时最长的路径,决定了能跑到的最高频率,A-E和B-E都是关键路径

(2)关键路径是某个点到某个点之间的。

(3)思考:我一定要跑300M,怎么办?

4.流水线设计

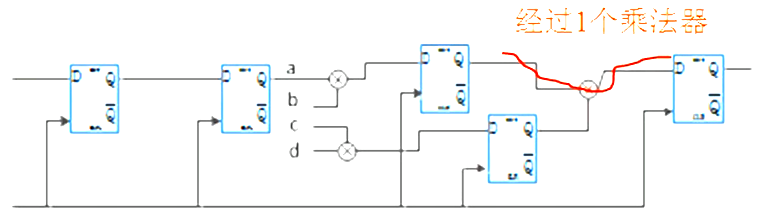

(1)设计时优化:举例s = a * b * c * d,没有增加硬件资源,但得到了优化

(2)继续优化,形成流水线设计。(中间加了一个寄存器进行暂存)

(3)继续优化,乘法器变成加法器。

举例:设reg[3:0] a,reg[1:0] b,求f = a*b。

做法:乘法变加法,f = a*b = a*b[0] + {a,1’b0}*b[1]

(4)继续优化,加法器分成门级电路等,不断细分,时钟频率得到很大提高。

(5)优化举例:

//原设计: a <= A + B + C + D; b <= a + E; ----------------------- //优化设计1: a_tmp1 <= A + B; a_tmp2 <= C + D; a <= a_tmp1 + a_tmp2; b <= a + E; ----------------------- //优化设计2,使用assign: assign a_tmp1 = A + B; assign a_tmp2 = C + D; a <= a_tmp1 + a_tmp2; b <= a + E;

5.通俗理解

某生产线分成4步骤并行工作,A要2小时,B要1小时,C要3小时,D要0.5小时。规定每隔3小时交接一次,要求到点前5分钟交接,到点后10分钟才能工作。那么:

(1)到点前5分钟,类似于FPGA的建立时间。

(2)到点后10分钟,类似于FPGA的保持时间。

(3)每隔3小时交接一次,类似于FPGA的时钟周期。

(4)2小时、1小时等,类似于FPGA的路径延时(Tco+Tdata)。

(5)C花费时间最长,类似于FPGA的关键路径。

(6)为了优化,可以将C的1小时工作,交给D来做。

(7)该生产线实际上不能正常运转。

二、用quartus II分析时序

1.建立工程,进行编译

2.打开时序分析窗口:Tools ---> TimeQuest Timing Analyzer

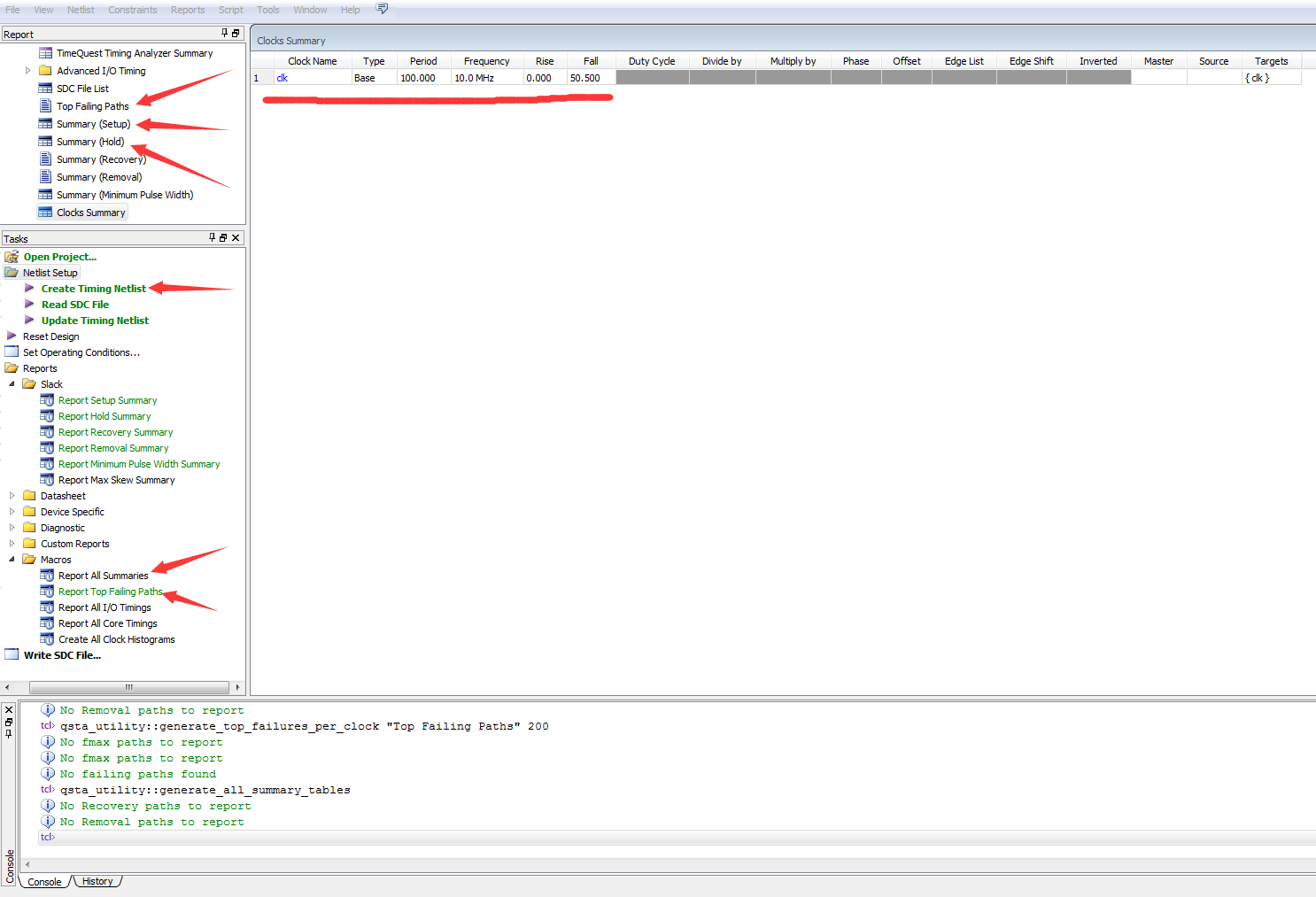

3.创建网表:Tasks窗口 ---> Netlist Setup ---> Create Timing Netlist

4.创建时钟信号

(1)Constraints ---> Creat Clock

(2)设置时间,周期,占空比时间

(3)Targets ---> List中找到时钟信号,添加进来

(4)RUN

5.Tasks窗口---> Macros ---> Report All Summaries,可看到所有情况,标红的为不满足的。

6.Tasks窗口---> Macros ---> Report Top Failing Paths,会把所有不满足的路径报告出来。Slack就是我们要注意研究的,可以知道我们超过了多少时间。

7.保存:Constraints ---> Write SDC File...

8.可点击Files ---> Open...打开刚刚保存的文件,查看里面代码,能看到设置的时钟,可直接对代码进行更改来改变时钟频率。

9.读取:Tasks窗口 ---> Netlist Setup ---> Constraints ---> Read SDC File...

10.弄完约束后,将Sdc文件添加进主页面的Files里,再进行编译,更新timequest网表重新分析。

11.如果哪个路径是我们认定不需要分析的,是我们异步处理不关心的,则可以右键选择 Set False Path (clocks) 这样语句就会改变,重新编译导表就OK了。

三、时序约束步骤

具体时序约束操作有很多,如creat clocks、input delays、output delays、set timing exceptions等,具体内容太多,由于没有真正做过这方面的项目,所以懂的不多,结合所学简要写一点。

1 //---------------------------------------------------- 2 //-- Time Information 3 //---------------------------------------------------- 4 5 1.时间精度设置,默认值为3 6 7 //---------------------------------------------------- 8 //-- Create Clock 9 //---------------------------------------------------- 10 11 1.输入时钟 12 A.输入管脚clk(P38) 13 a.直接输入,最常见 14 b.经过时钟管理单元(mmcm) 15 B.差分时钟(P36) 16 a.N端和P端两个口,只需要约束P端 17 C.GT或恢复的时钟(P39) 18 a.进来时无时钟,但因为ip核自行恢复了 19 20 2.虚拟时钟(P145) 21 A.无[get_ports]所以称为虚拟 22 B.典型应用如复位信号 23 24 //---------------------------------------------------- 25 //-- Create Generated Clock 26 //---------------------------------------------------- 27 28 1.衍生时钟(P36) 29 A.工具自动推导无需约束但建议更改名称 30 B.Altera自动推导需写上:derive_pll_clocks 31 32 2.自分频时钟(P36) 33 A.一般不建议自分频 34 B.自定义约束会覆盖工具推导约束 35 36 3.随路时钟 37 A.调整好随路时钟相位就能不约束input或output 38 39 //---------------------------------------------------- 40 //-- Set Clock Latency 41 //---------------------------------------------------- 42 43 时钟源(晶振)到触发器时钟输入端的延时,分两种 44 A.时钟源延迟(clock source latency) 45 B.时钟网络的延迟( clock network latency) 46 47 //---------------------------------------------------- 48 //-- Set Clock Uncertainty 49 //---------------------------------------------------- 50 51 1.时钟偏差,分两种去相加: 52 A.clock jitter 53 B.clock skew 54 2.可用derive_clock_uncertainty自行生成就不用自己算数 55 56 //---------------------------------------------------- 57 //-- Set Input Delay 58 //---------------------------------------------------- 59 60 1.参数说明 61 A. min for hold analysis 62 B. max for setup analysis 63 64 2.System系统同步(P112) 65 A.FPGA与Source Device共用时钟,二者延时相同 66 B.大部分情况仅仅用于SDR方式 67 a.查数据手册,套公式 68 min = Tco(min) + Tdata(min) 69 max = Tco(max) + Tdata(max) 70 b.示波器测量,套公式 71 min = DV_after 72 max = Period - DV_before 73 74 3.Source源同步(P114) 75 A.时钟和数据一起过来 76 B.SDR 77 a.查数据手册,套公式 78 min = Tco(min) + Tdata(min) 79 max = Tco(max) + Tdata(max) 80 b.示波器测量,套公式 81 min = DV_after 82 max = Period - DV_before 83 C.DDR,一般只用示波器测量,分为rise和fall 84 a.中心对齐 85 1.rise(未标明的就是rise) 86 min = DV_after_re 87 max = 0.5*Period - DV_before_fe 88 2.fall(添加-clock_fall-add_delay) 89 min = DV_after_fe 90 max = 0.5*Period - DV_before_re 91 b.边沿对齐(边沿前取负数) 92 1.rise(未标明者即为rise) 93 min = -skew_before_re 94 max = skew_after_re 95 2.fall(添加-clock_fall-add_delay) 96 min = -skew_before_fe 97 max = skew_before_fe 98 99 4.有数据无时钟(P145) 100 A.设置虚拟时钟,再用虚拟时钟约束此信号 101 B.随便设个both值即可 102 103 //---------------------------------------------------- 104 //-- Set Output Delay 105 //---------------------------------------------------- 106 107 1.参数说明 108 A.min for hold analysis 109 B.max for setup analysis 110 111 2.System系统同步(P130) 112 min = Tdata(min) - Th 113 max = Tdata(max) + Tsu 114 115 3.Source源同步(P131),与随路时钟搭配约束 116 A.两种理论计算方法 117 B.SDR 118 a.Setup/Hold理论 119 min = Tdata(min) - Th 120 max = Tdata(max) + Tsu 121 b.Skew理论 122 min = before_re_skew 123 max = Period - afer_re_skew 124 C.DDR,一般只用示波器测量,分为rise和fall 125 a.中心对齐,用Set/Hold理论 126 1.rise(未标明的就是rise) 127 min = -thd_r 128 max = tsu_r 129 2.fall(添加-clock_fall-add_delay) 130 min = -thd_f 131 max = tsu_f 132 b.边沿对齐,用skew理论 133 1.rise(未标明者即为rise) 134 min = before_re_skew 135 max = 0.5*period - after_fe_skew 136 2.fall(添加-clock_fall-add_delay) 137 min = before_fe_skew 138 max = 0.5*period - after_re_skew 139 140 //---------------------------------------------------- 141 //-- Set Clock Groups 142 //---------------------------------------------------- 143 144 不同时钟之间也可以在这里约束 145 146 //---------------------------------------------------- 147 //-- Set False Path 148 //---------------------------------------------------- 149 150 1.常量或伪常量(P172) 151 2.互斥路径(P173) 152 A.例如双向端口 153 3.异步时钟(P174) 154 A.先处理再约束 155 B.打两拍来同步信号和处理亚稳态 156 C.用异步fifo起到隔离时钟 157 158 //---------------------------------------------------- 159 //-- Set Multicycle path 160 //---------------------------------------------------- 161 162 1.两个寄存器间的数据传输在一个周期内没法完成时,可以 163 通过本命令改变建立值和保持值让其满足时序要求。 164 2.不建议使用多周期路径(P157-P164) 165 166 //---------------------------------------------------- 167 //-- Set Maximum Delay 168 //---------------------------------------------------- 169 170 纯组合逻辑路径,很少使用(P178) 171 172 //---------------------------------------------------- 173 //-- Set Minimum Delay 174 //---------------------------------------------------- 175 176 纯组合逻辑路径,很少使用(P178) 177 178 //---------------------------------------------------- 179 //-- Set Input Transition 180 //---------------------------------------------------- 181 182 很少用到

上述是Altera中常用到的约束方法,实际上里面的每一点都有很大的学问。里面的页数是一篇《timing》的文档,这样就不用记忆语句,直接查阅文档就行了。

四、小技巧

//-- pll时钟改名 //---------------------------------------------------- 1.编译工程,打开timing_quest,创建网表。 2.创建时钟后生成sdc文件,打开sdc文件并在衍生时钟处写上 derive_pll_clocks并保存,回到timing_quest重读该sdc文 件,发现pll时钟已经自动约束好,但是名字很复杂。 3.退出timing_quest,打开sdc文件,将pll时钟的名字改成需要 的名字并保存。回到quartus ii进行编译,打开timing_quest 并更新网表,看到pll时钟改名成功。 //-- 关于false path: //---------------------------------------------------- 1.异步时钟之间一般要进行false path 2.false path前,必须确定已经进行了处理,如打拍或FIFO隔离。 3.不一定都是clock之间的false,有时node之间的就可以。 4.Set Clock Groups中也可以担任跨时钟域的时序约束。

参考资料:[1]明德扬FPGA教程