Verilog学习(13)PLL与搜索代码

一:串行解串器的包格式与搜索代码

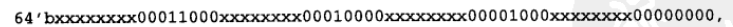

1:并行输入32bit数据,串行传输时,有特定的格式

上面的x表示8比特有效数据里的某一个比特。先发送和接收的是MSB(左侧数据)。为了给接收端的PLL提供一个同步的时钟,我们将在这个串行数据流中寻找从2‘b11到2’b00的递减计数值,当找到时,可输出一个found信号给PLL的时钟端用于同步。

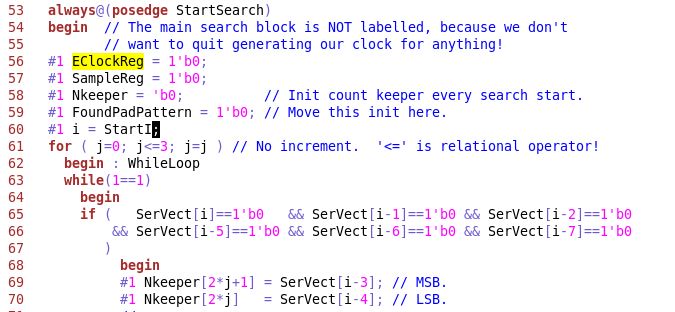

2:在一段数据中,匹配64bit包格式

i:代表64bit中的一个bit,初始为63;

j:一共有4各字节,j代表4各字节里的一个字节,初始为0,即初始为左侧数据(xxxxxxxx00011000);

IJump:十进制16,代表当找到第一个pad时,直接将 i 加到 i + IJump,不用一个一个加了;

nNow:2bit数据里的当前数据,例如,nNOW为第二个pad里的值:2‘b10;

nPrev:2bit数据里的前一个数据,例如,nPrev为第一个pad里的值:2’b11;

CountOK:我们在搜索时,当从11搜索到00时,CountOK=1;

Eclock:由CountOK驱动, 用EclockReg寄存;always @ (posedge CountOK)EclockReg = ~ EclockReg;连接PLL的时钟端。

Found:找到一个64bit包时,返回1;用FoundPadPattern寄存;

Sample:由Found驱动的T寄存器输出端,用SampleReg寄存;always @ (posedge Found)SampleReg = ~ SampleReg 连接PLL的Sample端(晶振允许端);

3:主要代码

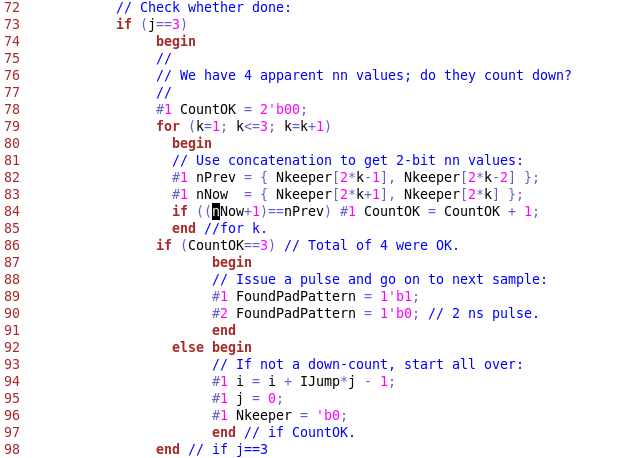

二:PLL行为级锁定

1:architecture

2:说明

第一幅图为搜索代码结构,搜索代码的输出分别作为PLL的时钟端与振荡器端,用以同步