VCS学习(6) 后仿 Fast Gate-level verification

对综合产生的门级网表(Gate-level)进行编译仿真

一:什么是后仿

前仿不包括时序信息,即当作理想的器件看待,仅仅验证代码的功能;后仿,在有时序信息,有延迟情况下(器件自身的延迟,传输线上的延时等,与工艺器件有关)的仿真;后仿主要关注Toggle覆盖率,因为门级网表里面没有RTL级代码,没有if,case等,都是与或非门等。

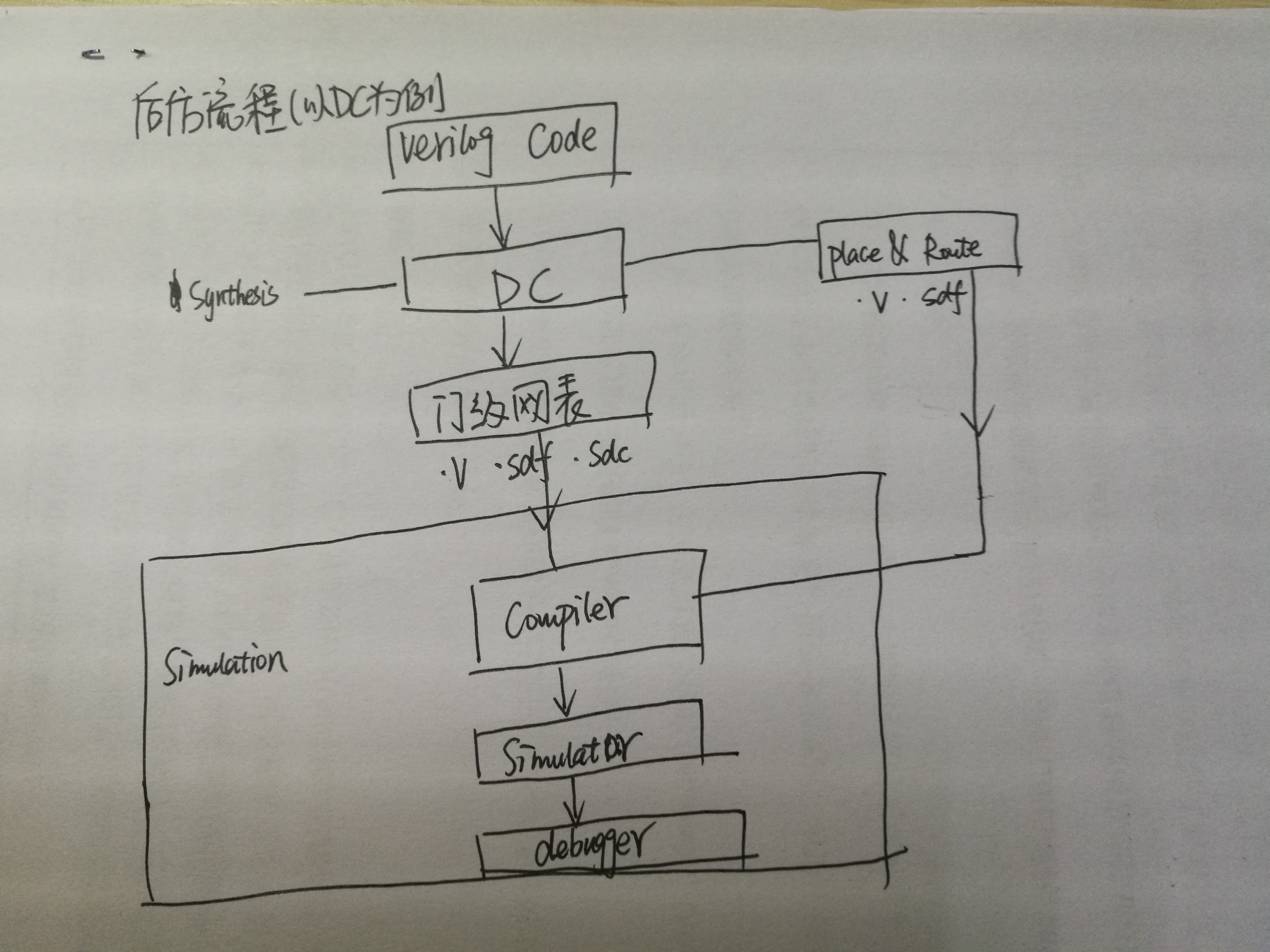

RTL级通过DC综合得到门级网表,布局布线得到门级网表,将两个门级网表加起来才是真正的网表文件;在本文中,我们只关注DC吐出来的网表以说明后仿。

+rad可以对仿真进行优化。

DC后不仅生成门级网表(也是.v文件),还产生.sdf文件(standard delay format,记录单元的时序的信息)。

二:后仿流程

三:SDF文件主要内容

Delays(module,device,interconnect,port)

Timing checks(setup,hold,setuphold,recovery,removal,recrem)

Timing constrains(pathconstraint,skewconstraint,sum,diff)

Timing environment(arrival,departure,slack,waveform)

包括design,时间,工艺,版本,电压,温度,延时信息,基本单元延时信息等。

四:综合后在vcs后仿具体步骤

1: 将综合后的网表文件.v拷贝到rtl代码文件夹里(即源文件夹里),并将原源文件(也是.v)改成.v.bak文件,防止make找不到正确的.v文件;

将综合后的SDF文件拷贝到tb文件夹(即testbench文件夹里);

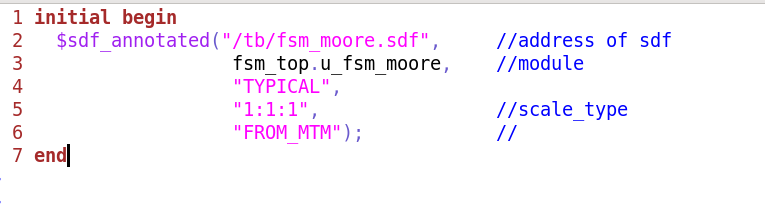

2: 在top层文件里(即testbench文件夹)反标添加SDF;

例如:

3: 在makefile里添加说明(compile里)

#vcs dut_gate.v -v sim_lib.v //.v是网表文件,工艺库-v

4: make com->make sim->make dve->在dve文件上观察波形,发现后仿波形不纯净

五:其他

1: 若SDF文件很大,可以进行预编译,dut.sdf文件变为dut.sdf_c

2: 选中delay方式:在compile开关选项上加+mindelays/+typedelays/+maxdelays

或者在compile开关选项上加+allmtm,在simulate在加+mindelays/+typedelays/+maxdelays

3: 惯性延迟(器件自带),传输延迟

4: 若使用预编译方式,则+rad失效