SPI FLASH学习笔记(一)读操作

FLASH芯片使用:GD5F1GQ4UEYIG

概况

SPI(串行外围接口)NAND闪存可提供超低成本的同时高密度非易失性存储器基于行业标准NAND闪存内核的嵌入式系统存储解决方案。这是一个有吸引力的具有高级功能的SPI-NOR和标准并行NAND闪存的替代产品:

•总引脚数为8,包括VCC和GND

•密度为1G位

•优于SPI-NOR的卓越写入性能和每位成本

•比并行NAND低得多的成本

这种低引脚数NAND闪存遵循行业标准的串行外围设备接口,始终保持从一种密度到另一种密度的相同引出线。该命令集类似于常见的SPI-NOR命令集,修改为处理NAND特定功能并添加了新功能。 GigaDevice SPI NAND是易于集成的NAND闪存内存,具有指定的设计功能以简化主机管理:

•用户可选的内部ECC。 ECC代码是在页面编程操作期间内部生成的。当页面是读取到高速缓存寄存器后,将检测ECC代码并在必要时更正错误。 64字节的备用区是即使启用内部 ECC也可用。设备输出校正后的数据并返回ECC错误状态。

•内部数据通过内部ECC移动或复制回去。该设备可以轻松刷新并管理垃圾收集任务,而无需移入和移出数据。

•使用内部ECC打开读取电源。设备上电后将自动读取第一块的第一页以进行缓存然后主机可以直接从缓存中读取数据以方便启动。此外,内部ECC正确承诺了数据。在基于页面的操作中对其进行编程和读取,而在基于块的操作中对其进行擦除。数据往返于将NAND闪存阵列逐页连接到数据寄存器和缓存寄存器。高速缓存寄存器最接近I / O控制电路,并充当I / O数据的数据缓冲区;数据寄存器最靠近存储器阵列,并作为数据NAND闪存阵列操作的缓冲区。高速缓存寄存器用作缓冲存储器以启用页面和随机数据读/写和回写操作。这些设备还使用SPI状态寄存器来报告状态设备操作。

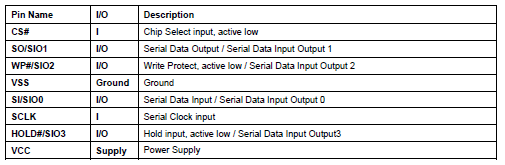

FLASH接品定义:

FLASH框图

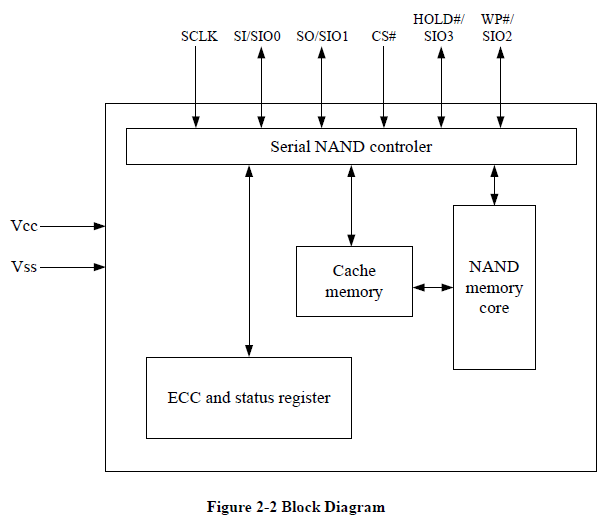

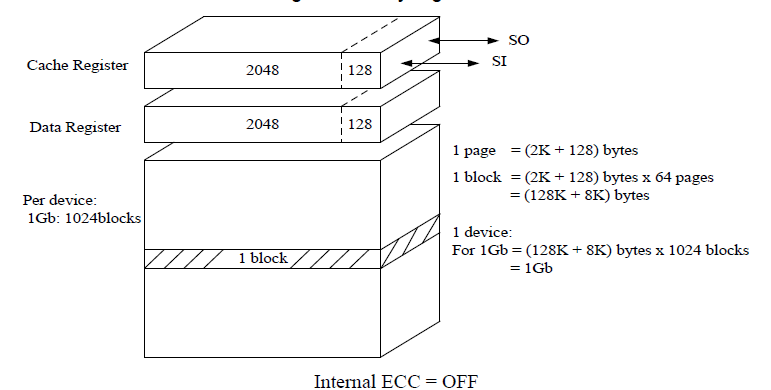

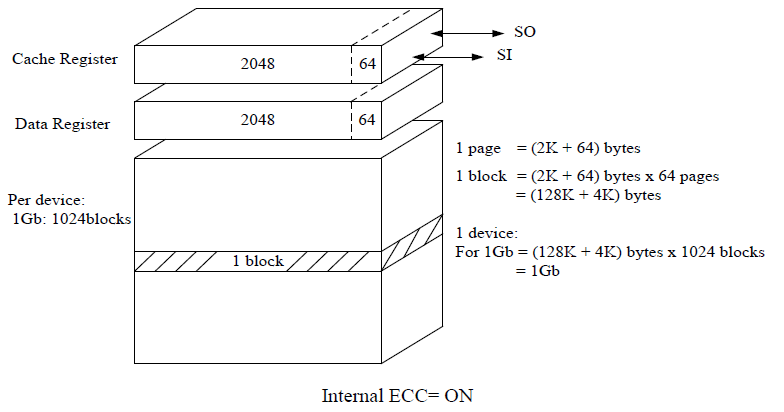

内存阵列结构

注意: 1.启用内部ECC后,用户只可以对整个128字节备用区的前64个字节写数扰, 整个备用区的最后64个字节无法编程,用户可以读取整个128字节的备用区。

2.禁用内部ECC时,用户可以读取和编程整个128字节的备用区。

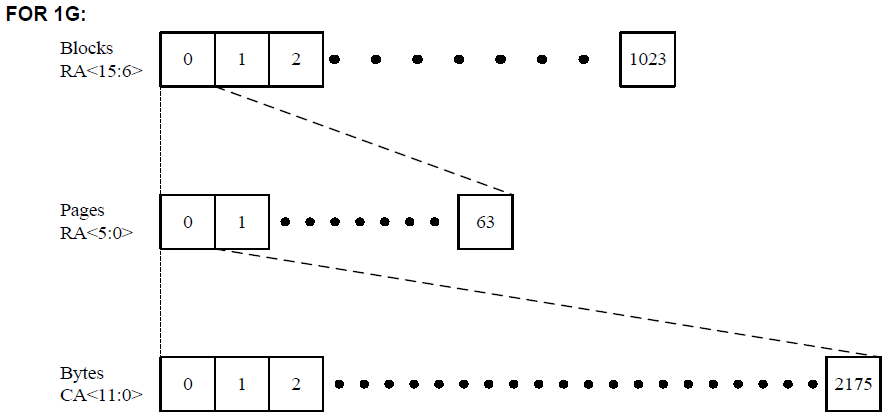

寻址

注意:

1. CA:列地址。 12位地址的地址范围为0到4095字节。 但是,只有字节0至2175有效。 每个页面的字节2176至4095是“超出范围”的,在设备中不存在,

并且无法解决。

2. RA:行地址。 RA <5:0>选择一个块内的页面,RA <15:6>选择一个块。

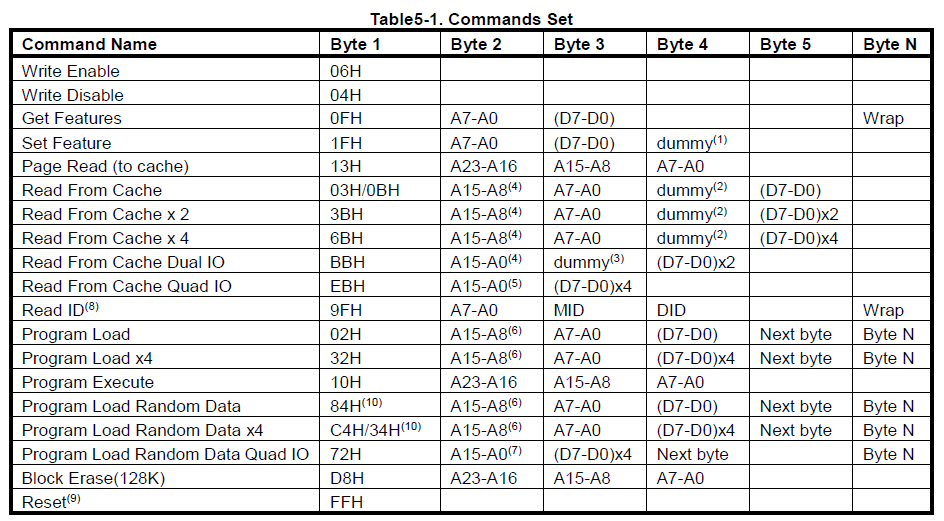

命令列表

Notes:

1. The dummy byte can be inputted or not.

2. The x8 clock = dummy<7:0>.

3. The x8 clock = dummy<7:0>, D7-D0.

4. The x8 clock = dummy<3-0>, A11-A8 or dummy<3-0>, A11-A0.

5. The x8 clock = dummy<3-0>, A11-A0, dummy<7:0>, D7-D0.

6. The x8 clock = dummy<3:0>, A<11:8>.

7. The x8 clock = dummy<3:0>, A<11:0>, D7-D0, D7-D0.

8. MID is Manufacture ID (C8h for GigaDevice), DID is Device ID

When A7-A0 is 00h, read MID and DID.

9. Reset command:

• During busy, Reset will reset PAGE READ/PROGRAM/ERASE operation.

• During idle, Reset will reset status register bits P_FAIL/E_FAIL/WEL/OIP/ECCS/ECCSE.

10. Those commands are only available in Internal Data Move operation.

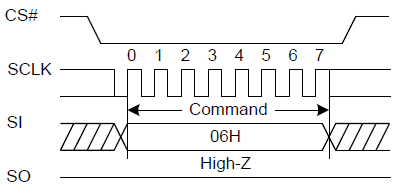

06H写允许命令实例:

写使能(WREN)命令用于设置写使能锁存(WEL)位。 写使能锁存(WEL)位

必须在进行以下更改内存阵列内容的操作之前进行设置:

•页编程

•OTP编程/ OTP保护

•块擦除

复位命令后,可以清除WEL位。

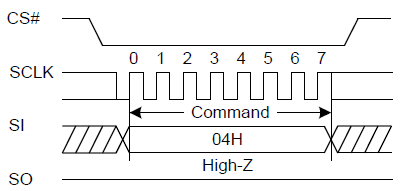

04H写禁止命令实例:

写禁用命令用于复位写使能锁存(WEL)位。 WEL位也可以通过以下方式复位到正常状况:

•页编程

•OTP编程/ OTP保护

•块擦除

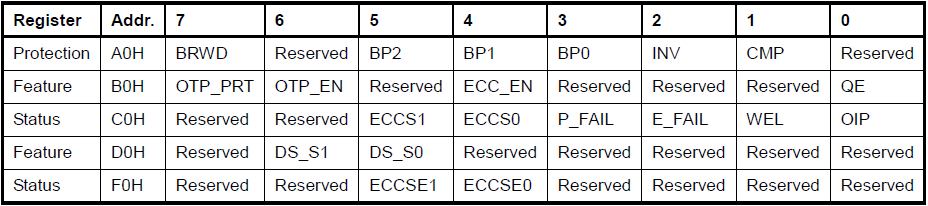

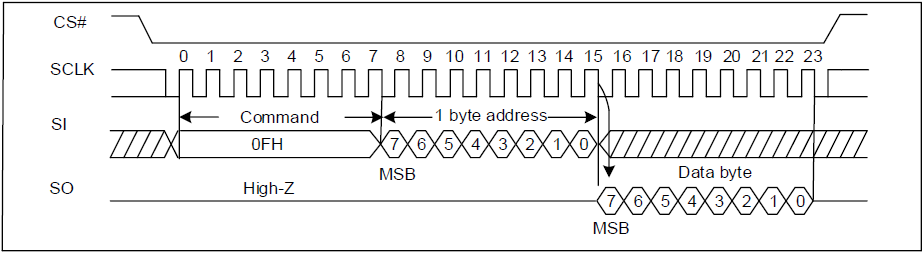

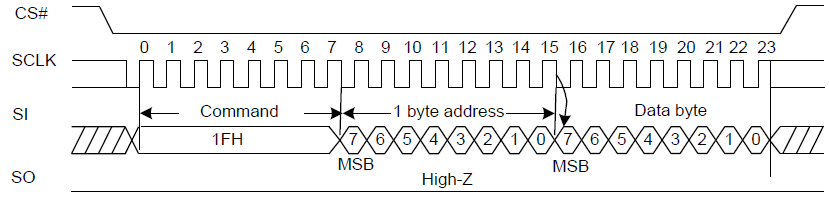

读取功能状态(0FH)和设置功能(1FH)实例

GET FEATURES(0FH)和SET FEATURES(1FH)命令用于监视设备状态并更改设备行为。 这些命令使用1字节的功能地址来确定要读取或修改的功能。

可以通过设置特定功能位来启用或禁用诸如OTP和块锁定之类的功能(如下所示)表)。 除了WEL以外,大多数读取状态寄存器,而WEL是WRITE ENABLE(06H)命令的可写位。设置功能后,该功能将保持活动状态,直到关闭电源并重新打开设备或写入该功能为止。 除非另有按下表中指定的那样,一旦设置了设备,即使发出RESET(FFH)命令,它也会保持设置状态。

注意:如果启用了BRWD且WP#为LOW,则无法更改块锁定寄存器。如果启用了QE,则可以执行Quad IO操作。设置该功能时,所有保留位必须保持为低电平。

上电后,00h是输出驱动器寄存器的默认数据字节值。

Get Features Sequence Diagram

注意:输出将实时更新,直到将CS#驱动为高电平为止。set features命令在数据字节之后也支持虚拟字节模式。 特征字节B0H中的特征

除OTP_PRT位外,其余均为易失性。

Set Features Sequence Diagram

读操作实例:

页面读操作

PAGE READ(13H)命令将数据从NAND闪存阵列传输到高速缓存寄存器。命令

顺序如下:

•13H(页面读取到缓存)

•0FH(使用“获取功能”命令读取状态)

•03H或0BH(从高速缓存读取)/ 3BH(从高速缓存x2读取)/ 6BH(从高速缓存x4读取)/ BBH(从高速缓存双IO读取)/ EBH(从高速缓存四路IO读取)

PAGE READ命令需要一个24位地址。注册块/页面地址后,设备启动从主阵列传输到缓存寄存器,并且在tRD时间内忙碌。在这段时间内,获取功能(0FH)

可以发出命令以监视状态。跟随页面读取操作,即RANDOM DATA READ

为了发出高速缓存中的数据,必须发出(03H / 0BH / 3BH / 6BH / BBH / EBH)命令。输出数据开始在命令中指定的初始地址处,一旦到达2176字节节的结束边界,输出会自动跳到起始边界,直到CS#被拉高以终止此操作。参考波形以查看整个读取操作。

Page Read to Cache (13H)

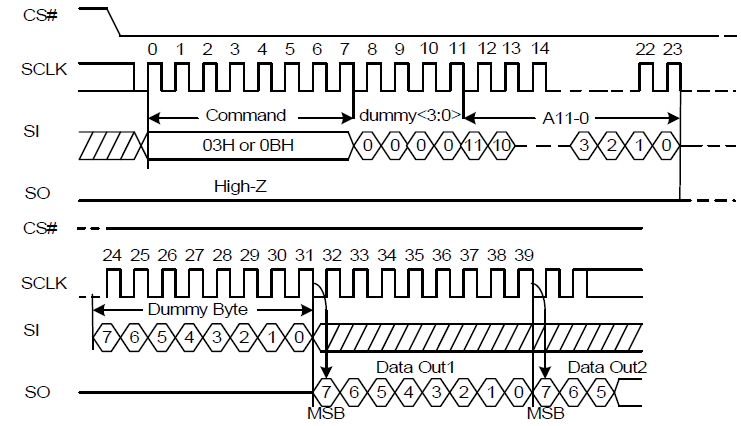

Read From Cache (03H or 0BH)

Read From Cache x2 (3BH)

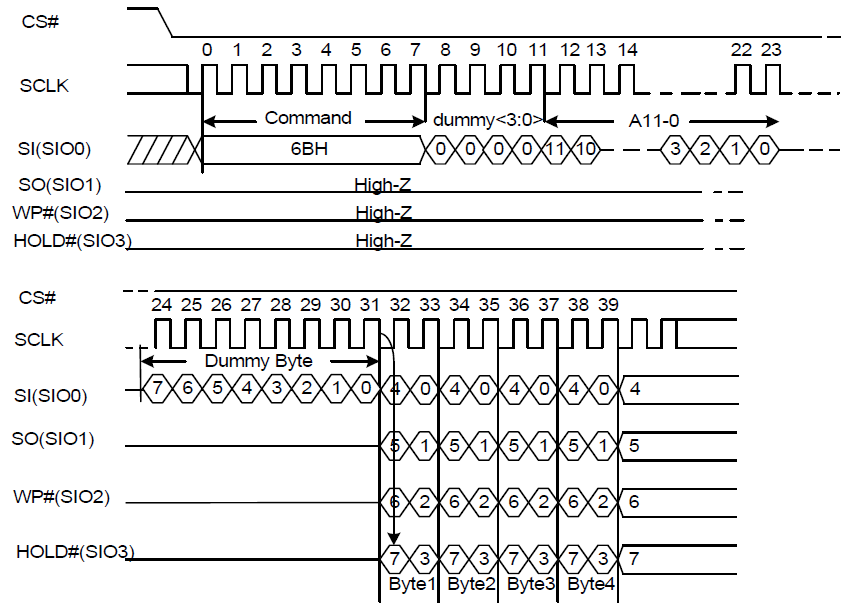

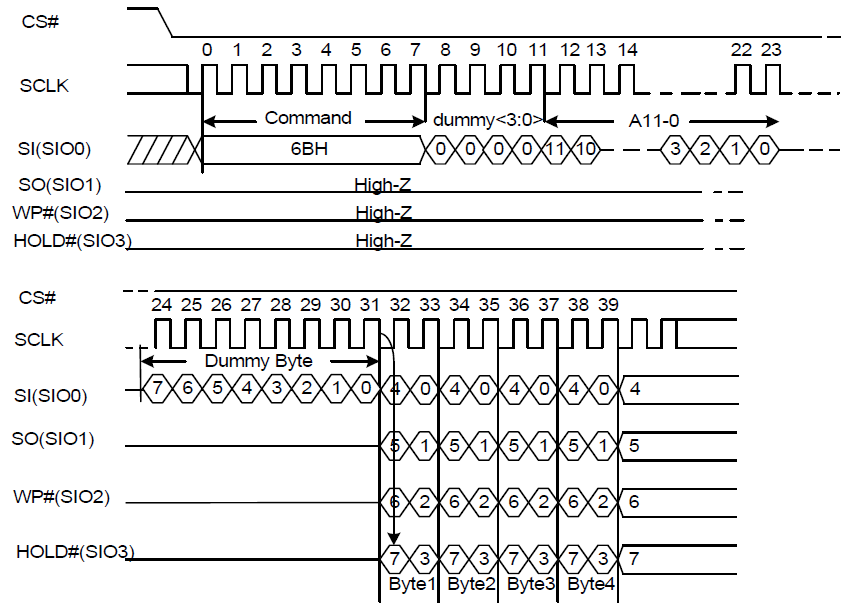

Read From Cache x4 (6BH)

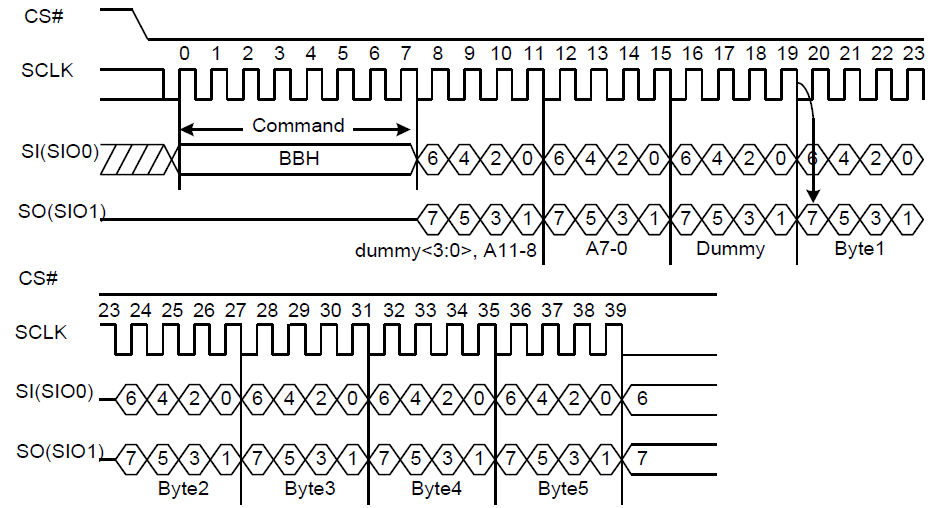

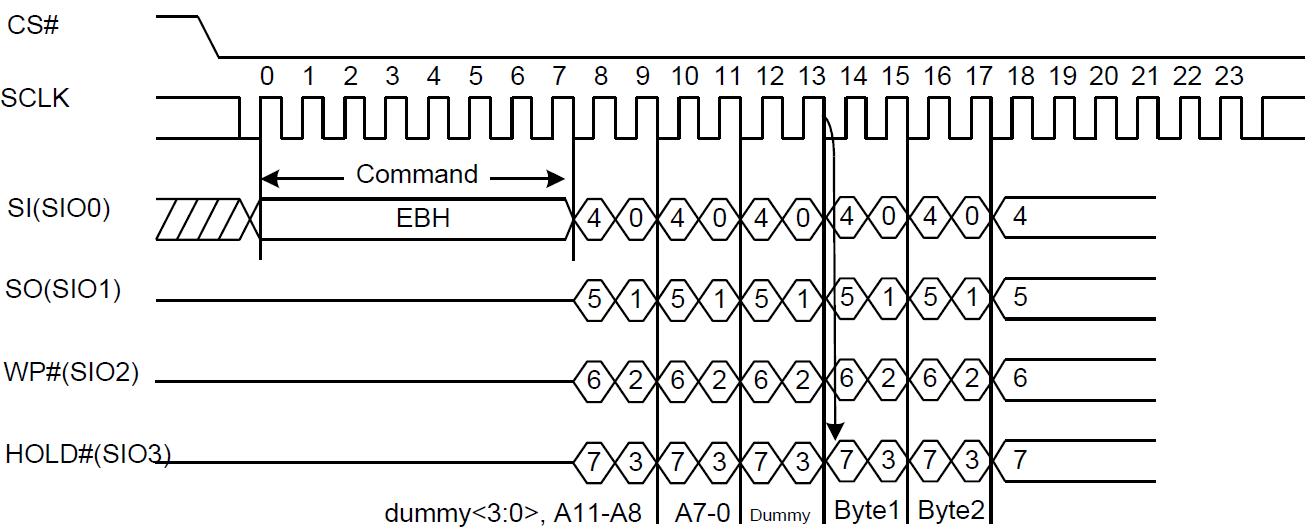

Read From Cache Dual IO (BBH)

“从双I / O读取缓存”命令(BBH)与“从窗体读取缓存x2”命令(3BH)相似,但具有能够输入4个虚拟位,后跟一个12位列地址作为起始字节地址和一个虚拟字节

通过SIO0和SIO1,每个位在SCLK的上升沿被锁存,然后将高速缓存内容移出2位每个时钟周期从SIO0和SIO1开始。 第一个地址字节可以在任何位置。 地址自动增加

在每个数据字节移出边界包裹位之后,将其移至下一个更高的地址。

Read From Cache Dual IO Sequence Diagram

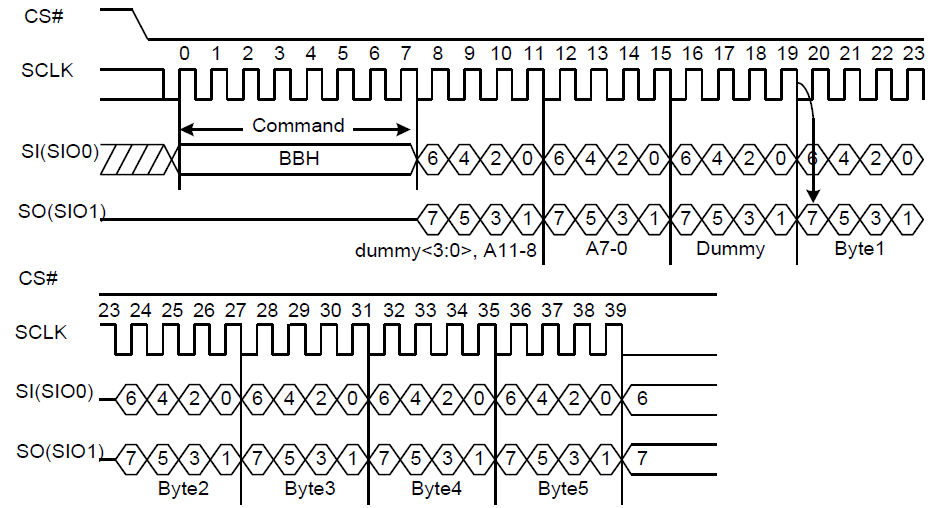

Read From Cache Quad IO (EBH)

从高速缓存Quad IO读取命令类似于从高速缓存x4读取命令,但具有输入功能4个虚拟位,后跟一个12位的列地址(起始字节地址)和一个虚拟字节,后跟SIO0,SIO1,SIO3,SIO4,每个位在SCLK的上升沿被锁存,然后每个时钟将高速缓存内容移出4位从SIO0,SIO1,SIO2,SIO3开始循环。 寻址的第一个字节可以在任何位置。 地址是自动的在每个数据字节移出边界环绕位之后,递增到下一个更高的地址。 四重启用必须将功能(B0 [0])的位(QE)设置为启用从高速缓存Quad IO命令读取。

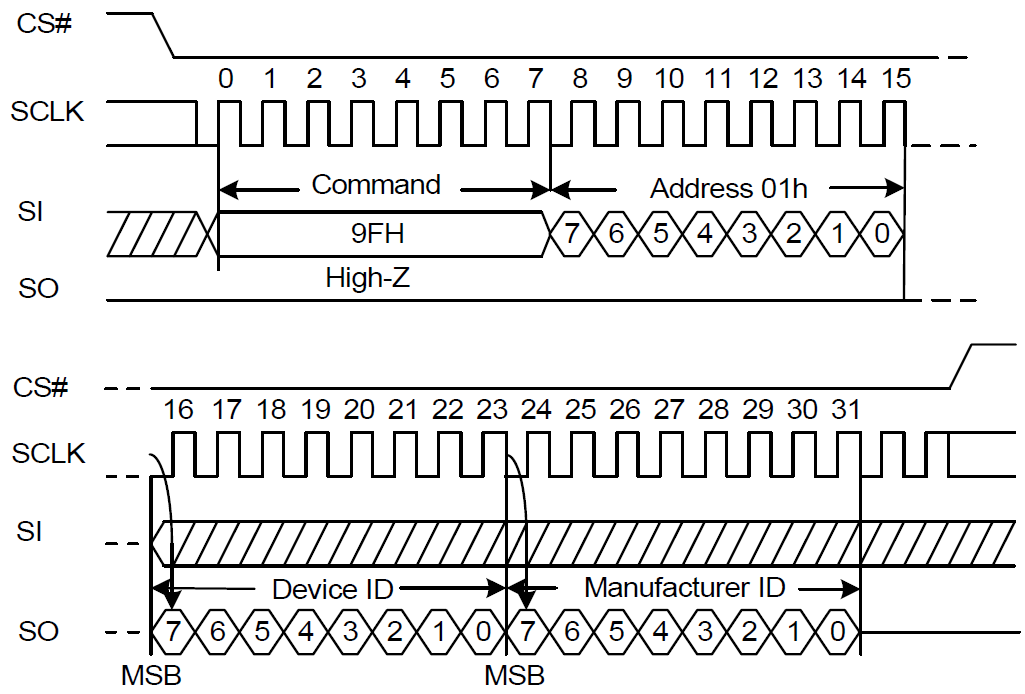

Read ID

READ ID命令用于标识NAND闪存设备。

•使用地址00H〜01H,READ ID命令输出制造商ID和设备ID。

Read ID Sequence Diagram (address 00h)

Read ID Sequence Diagram (address 01h)