物理综合:关于UDSM后端设计总结

![]() 随着科技的发展,65nm及65nm以下的工艺节点成为设计的主流

随着科技的发展,65nm及65nm以下的工艺节点成为设计的主流

- 随着工艺的发展,绝对的物理变异导致相对较大的电气特性变异

- 随着工艺的发展,时序收敛变得越来越困难

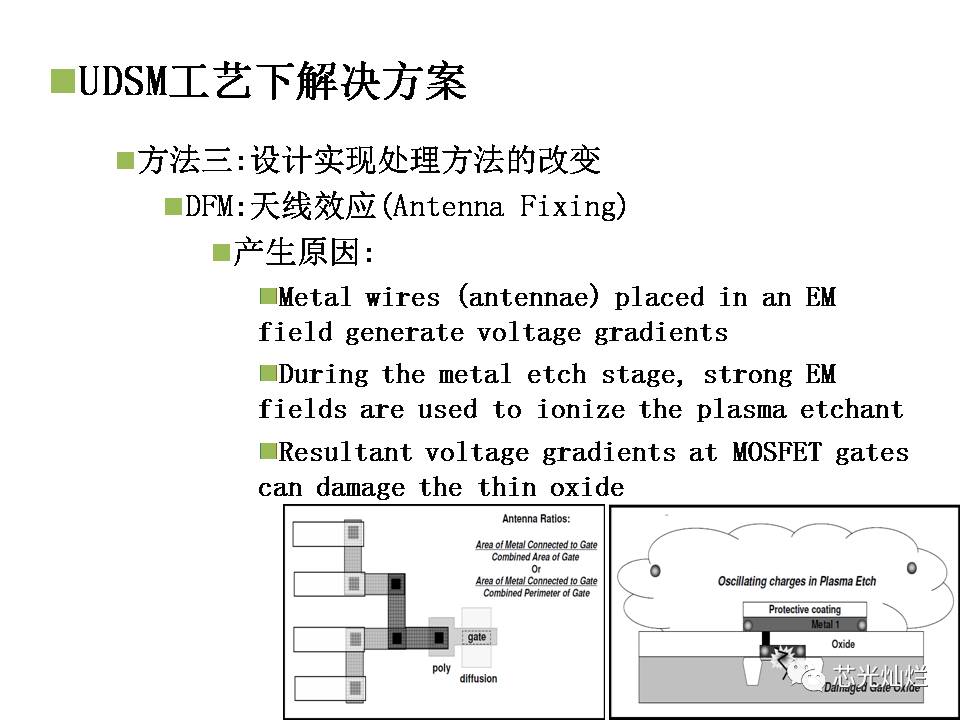

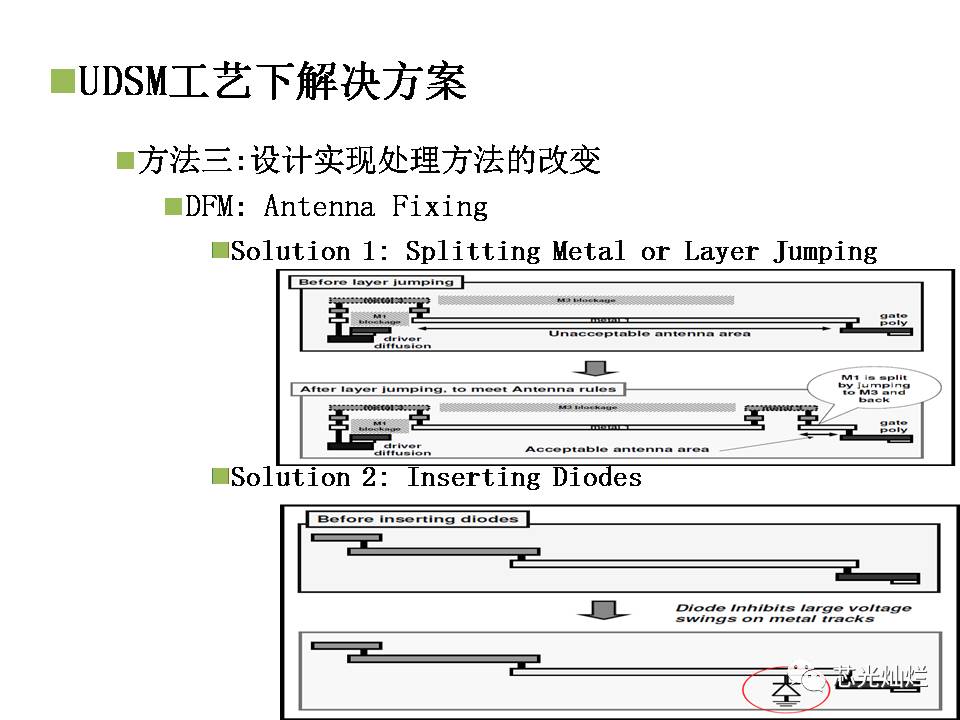

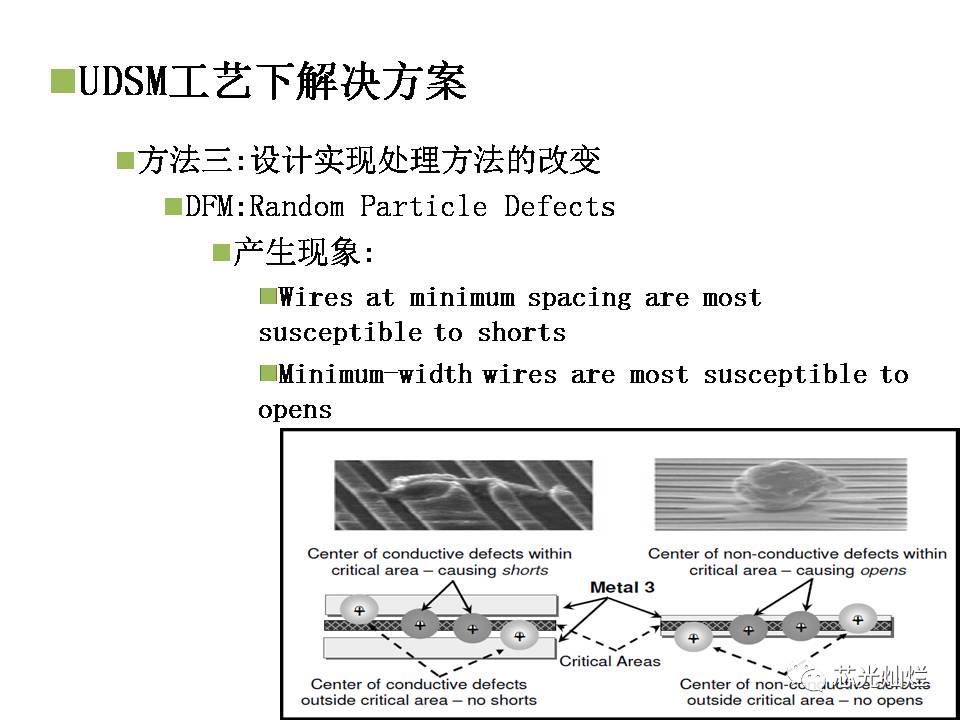

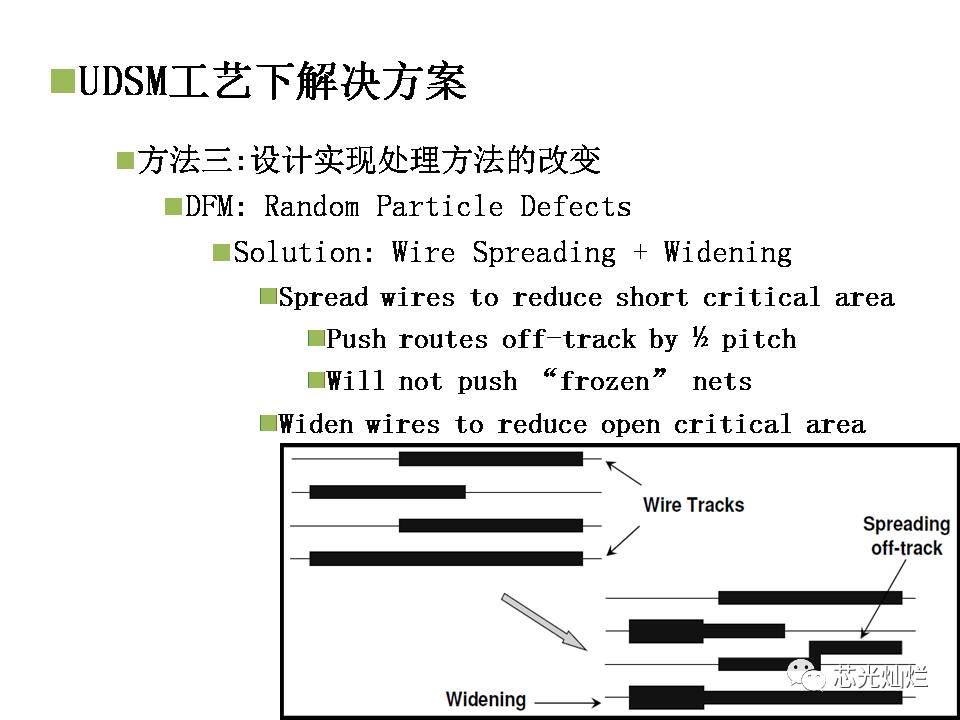

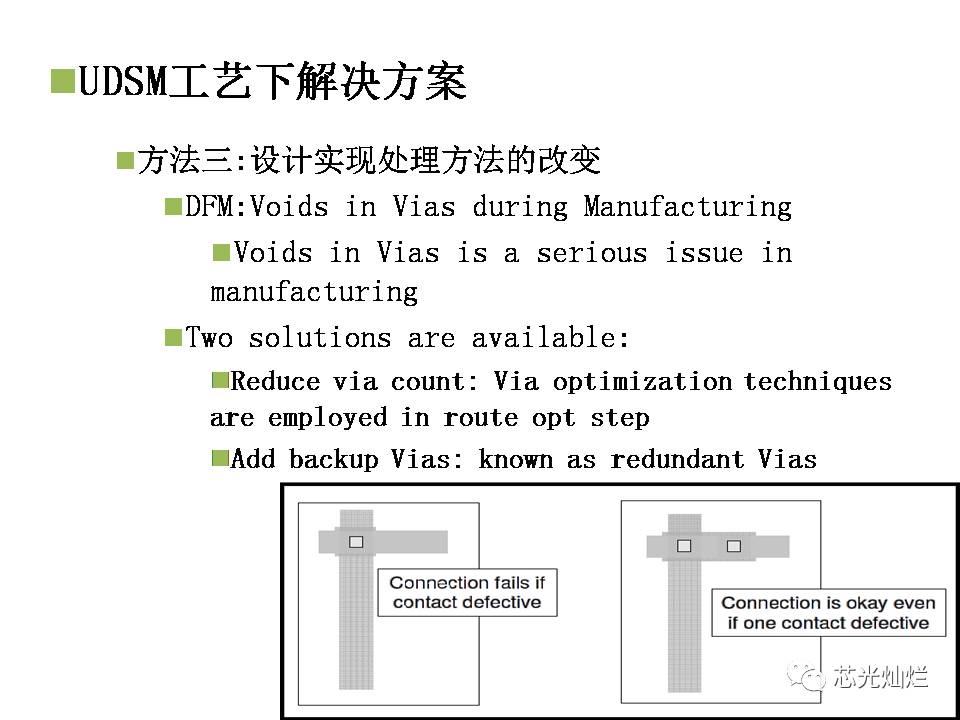

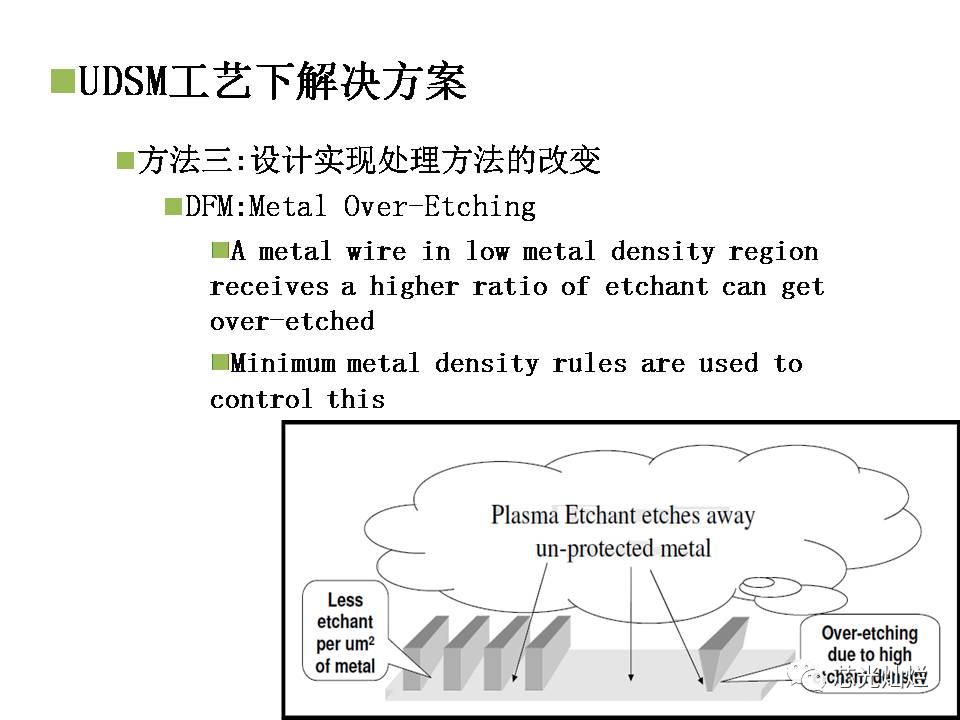

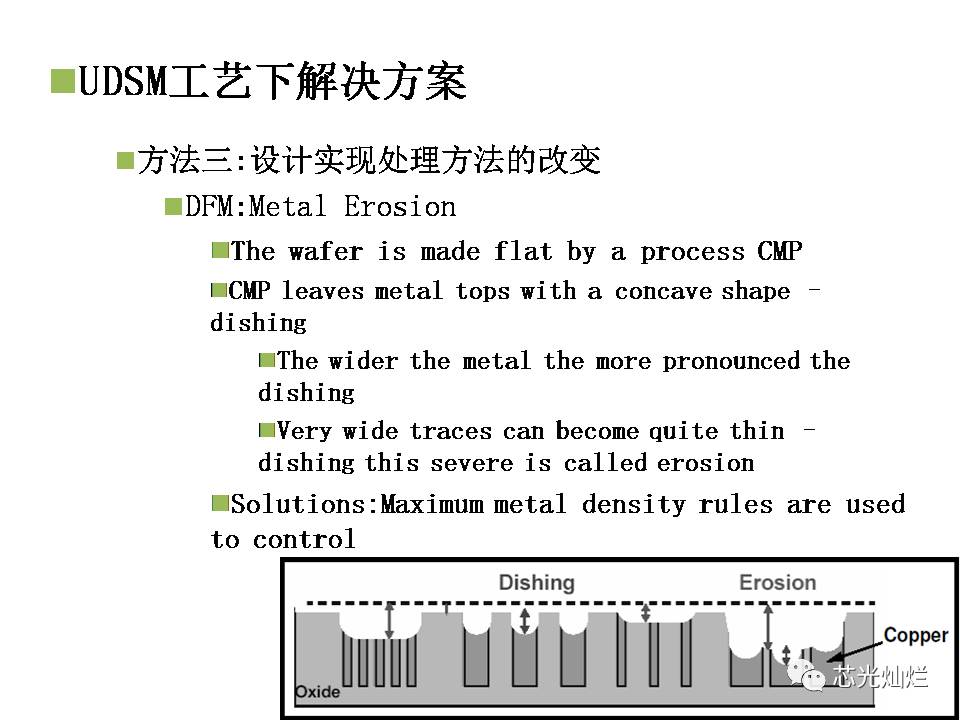

- 可制造性的问题(DFM)变得越来越关键

- 本文针对UDSM后端设计中的问题,做一个分析和总结希望对大家的面试和工作有帮助

- UDSM下工艺库,从90nm往下,library更新为CCS(Composite Current Source)模型,相比以前的NLDM模型,CCS更精确

时序,功耗,噪声的完美结合,包含以下信息

High impedance interconnect

Miller effect

Dynamic IR-drop

Multi-voltage

Temperature Inversion

支持

Noise glitch propagation

Scaling of temperature/voltage

UDSM带来的问题

- 问题产生的核心原因:

- 硅芯片特征尺寸现在小于用来生成这些特征的光的波长,随着特征尺寸越来越小,导致出现在硅片上的图形形状与理想形状的差异越来越大

- 先进半导体的制造依赖于设计和制造之间的巧妙平衡

- 制造问题会引起

良率下降(通过改进DFM技术改进)

性能劣化(通过改进时序分析技术改进)

功耗上升(通过改进DFM技术改进)

更多资讯,请关注个人公众号:芯光灿烂

【魏老师说IC】旨在通过该平台为大家提供一个集成电路技术交流、分享、学习的平台,如果有任何问题或者咨询,可以在博客中留言或者关注个人微信公众号“芯光灿烂”进行更深入的交流和学习。

随着科技的发展,65nm及65nm以下的工艺节点成为设计的主流

随着科技的发展,65nm及65nm以下的工艺节点成为设计的主流

浙公网安备 33010602011771号

浙公网安备 33010602011771号