物理综合:关于wire_load

-

Wire load model Vs Topographical Mode

-

针对 wire load model(WLMs模式)

-

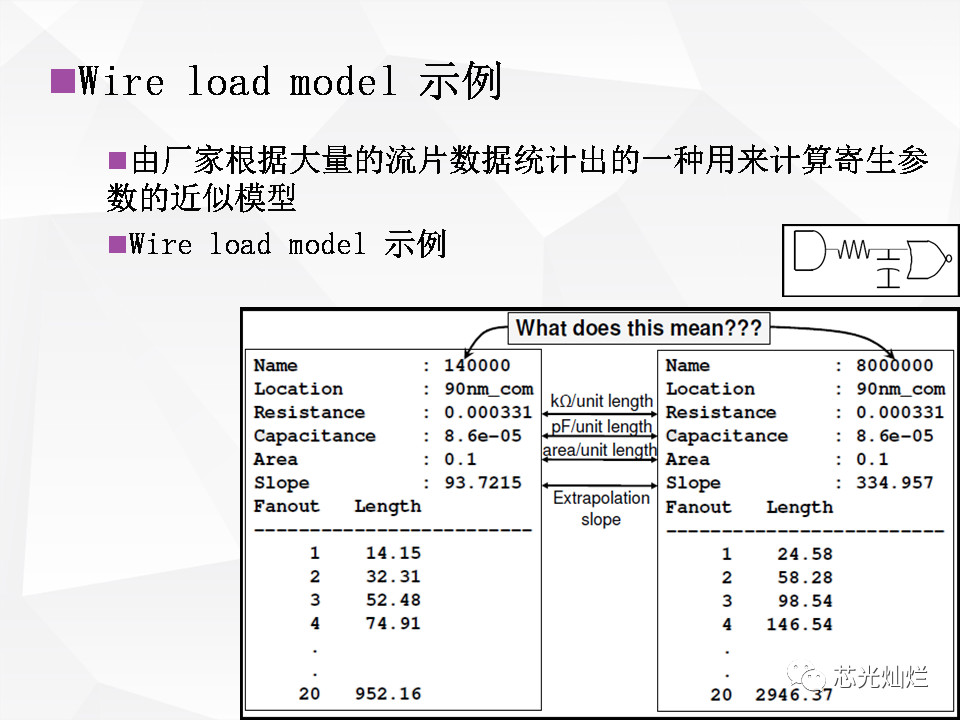

Wire load model (WLMs)是厂家基于统计规律得出的一套模型.换言之,考虑到设计的不同,不是每个设计都完全满足

-

针对Topographical mode(DcT模式)

-

Topographical mode 减少了对 WLMs的依赖

-

针对版图信息做寄生参数的选择和优化,理论上更符合项目的实际情况

-

和最终的物理结果相比,时序收敛性的问题得到了很大的加强和改善

-

仅支持DcT模式,需要有额外的license支持

-

Wire load model总结

-

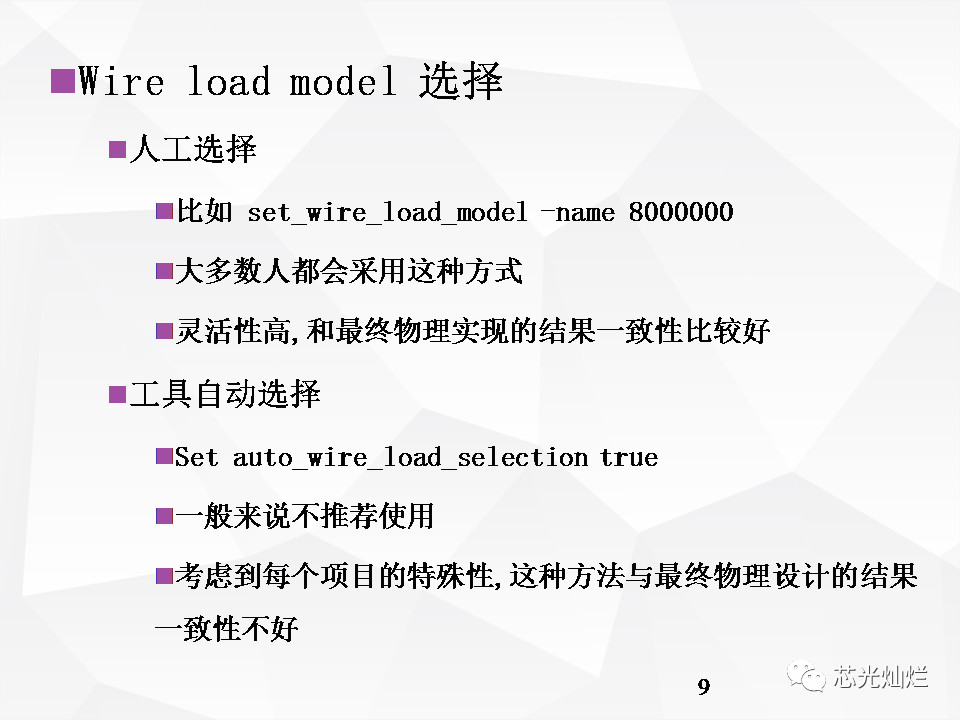

Wire load model 的方式和数值的选择,将极大的影响芯片的时序结果和后端物理实现的时序收敛性

-

请根据项目的实际情况,合理选择综合的方式和方法

-

一般来说,最初综合完成之后,需要根据设计所含的门数判断芯片的大小,选择合理的WLMs进行迭代.这样做的结果才有物理意义

-

与后端结果的时序收敛性是判断综合策略是否合理的唯一标准

-

一般来说,综合方式和方法的选择,要给后端设计人员留有一定的设计裕量

-

随着工艺向更小的尺寸发展,DcT将成为潮流

【魏老师说IC】旨在通过该平台为大家提供一个集成电路技术交流、分享、学习的平台,如果有任何问题或者咨询,可以在博客中留言或者关注个人微信公众号“芯光灿烂”进行更深入的交流和学习。

浙公网安备 33010602011771号

浙公网安备 33010602011771号